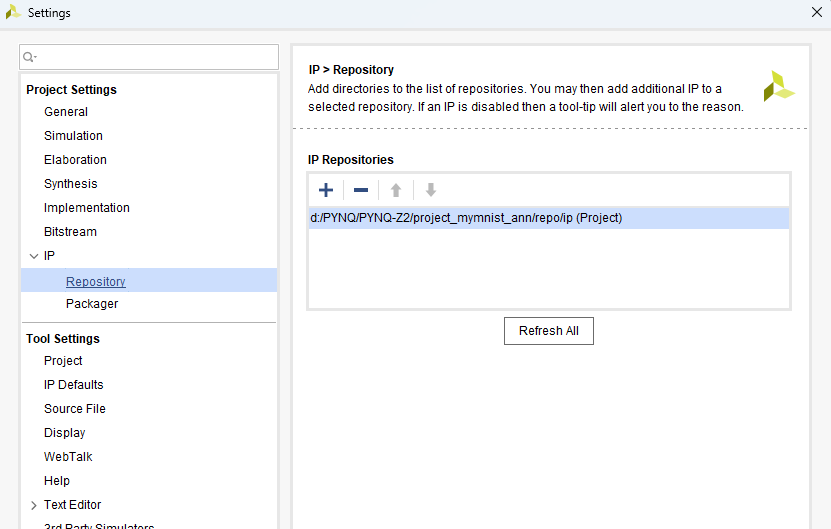

添加文件库后才能搜到IP

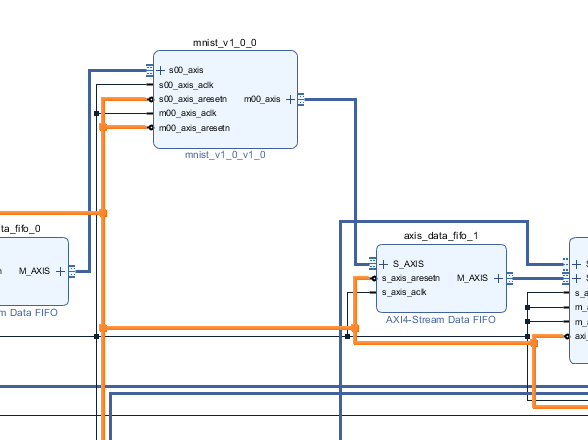

添加IP后连线

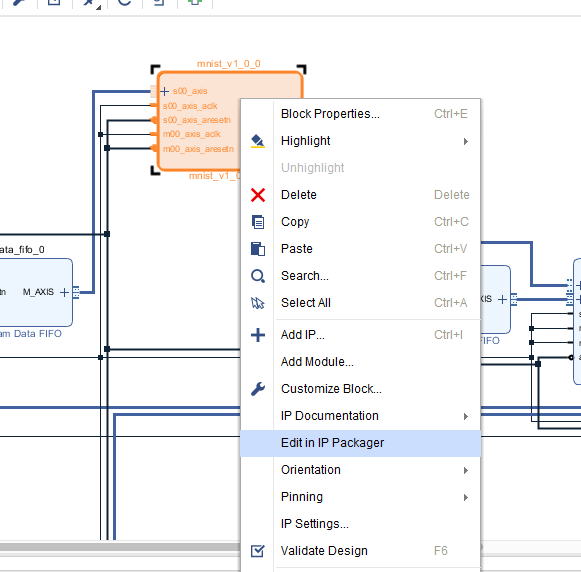

看这个IP的文件

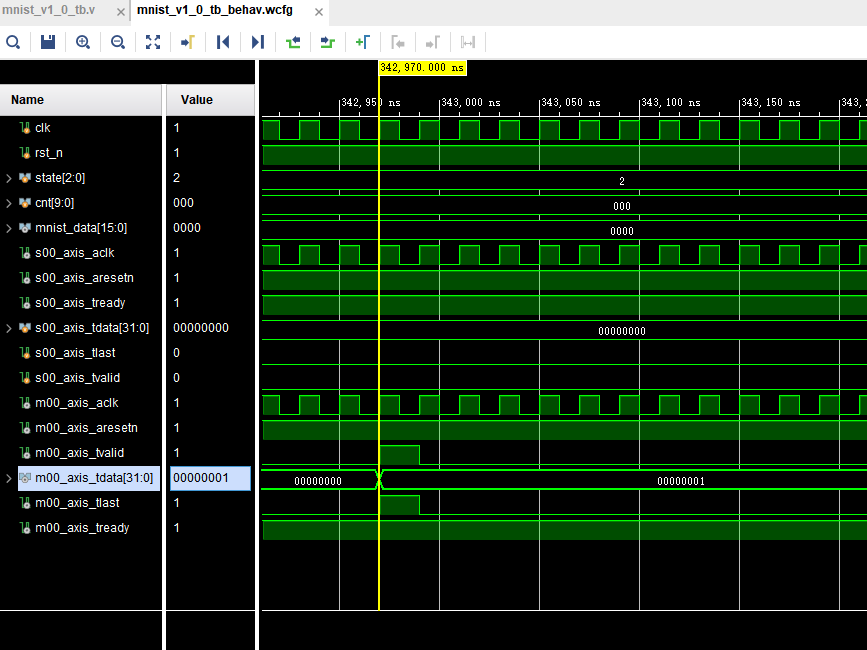

查看一simulation

添加testbench的Verilog或者systemverilog文件后,启动仿真报错:

ERROR: [XSIM 43-3268] Logical library name '"../../../../../../repo/ip/sim/BN_blkmem.v"' should not contain white space, new line, /, \, = or . ERROR: [XSIM 43-3217] mnist_v1_0_tb_vlog.prj (line 3): Incorrect project file syntax. Correct syntax is one of: vhdl <worklib> <file>, verilog <worklib> <file> [<file> ...] [[-d <macro>] ...] [[-i <include>] ...], or NOSORT. Presence of NOSORT on a line of its own disables file order sorting.

解决方法,将所有文件放入默认库中,

在vivado命令行执行:

set_property library xil_defaultlib [get_files]

from pynq import Overlay

import pynq.lib.dma

from pynq import allocate

import time

import numpy as np

import matplotlib.pyplot as plt

import os

mnist_test_design = Overlay("./bitstreams/demo.bit")

img = plt.imread("./images/mnist/9/3.bmp")

plt.imshow(img)

img_size = 28

input_buf = allocate(shape=(img_size*img_size,), dtype=np.uint32)

output_buf = allocate(shape=(1,), dtype=np.uint32)

for i in range(img_size):

for j in range(img_size):

input_buf[img_size*i+j] = img[i][j]

dma_send_recv = mnist_test_design.axi_dma_0

start = time.time()

dma_send_recv.sendchannel.transfer(input_buf)

dma_send_recv.recvchannel.transfer(output_buf)

dma_send_recv.sendchannel.wait()

dma_send_recv.recvchannel.wait()

end = time.time()

print('time cost: ' + str(round(end-start,5)) + ' s')

print('label: ' +str(output_buf[0]))

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?