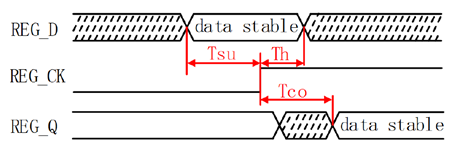

Tsu Th Tco

一、用没有delay的clock理解

对于实际的D触发器来说,为了保证在时钟的上升沿能够正确的将D端的数据寄存并输出到Q端,需要满足以下两点:

1.D端的数据必须在时钟上升沿到来之前的一定时间内就已经保持稳定,该时间被称为D触发器的建立时间(Tsu)

2.D端的数据必须在时钟上升沿到来之后的一定时间内继续保持稳定,该时间被称为D触发器的保持时间(Th)

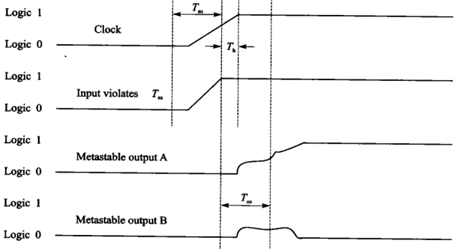

如果不能同时满足上述两个条件,那么D端的数据就可能无法正确的被寄存并输出至Q端3.同时,对于D触发器来说,D端的数据也不可能会在时钟上升沿出现的那一刻就立即更新到Q端,从时钟的上升沿到D端的数据稳定出现在Q端,也有一个时间,该时间称为寄存器的时钟到输出延迟(Tco)

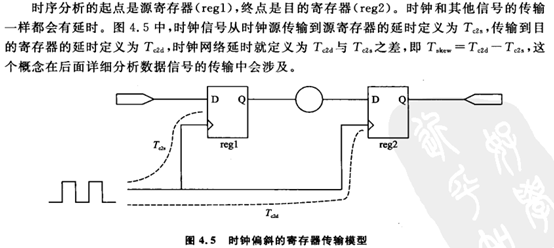

二、用有delay的clock理解

寄存器建立的时间 Tsu(set up)

寄存器的保持时间Th(hold)

时钟变化到输出的时间Tco(clock to output)

对于有delay的clock 书上是以50% Vdd为界限区分高电平和低电平

Clock Skew

建立时间(Tsu):是指在时钟上升沿到来之前数据必须保持稳定的时间。

保持时间(Th):是指在时钟上升沿到来以后数据必须保持稳定的时间。

一个数据需要在时钟的上升沿被锁存,那么这个数据就必须在这个时钟上升沿的建立时间和保持时间内保持稳定。

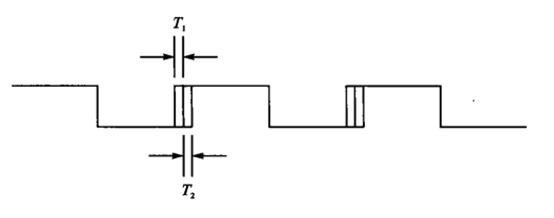

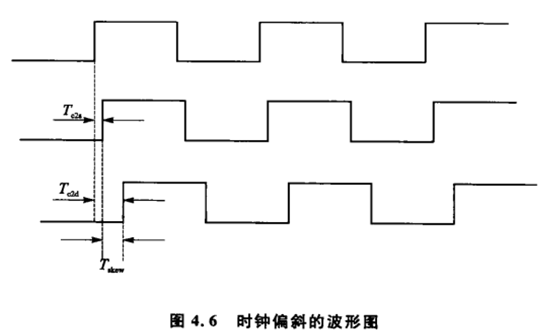

Clock Skew

从时钟的根节点到每个寄存器时钟端的延迟,由于走的路径不同,到达时间也不同。它们的延迟之差称为时钟偏斜(clock skew)。时钟信号边沿变化的不确定时间称之为时钟偏斜(clock skew)。

回到之前的建立时间和保持时间,严格的来说,建立时间就应该是Tsu+T1,保持时间也就应该是Th+T2。

具体波形图在图4.6所示。

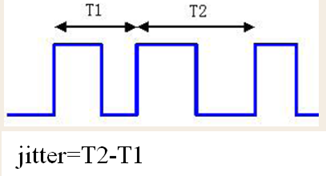

Clock Jitter

所谓时钟抖动(clock jitter),就是指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。如下图所示:

时钟频率具有随环境温度变换的特性,理想的方波是不存在的。在不影响系统性能的情况下,允许时钟在一个很小的时间范围内变换(这个变化的范围往往是微乎其微,有时甚至可以不去考虑),这个相对的变化时间即为时钟抖动,时钟抖动(clock jitter)是源时钟的不确定性因素(clock uncertainty)之一。

7785

7785

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?