锁相环学习电路,有教程

对新手非常友好,一看就懂

[1],输出频率800MHz或者1GHz,

采用Ring_VCO的结构

[2],输入参考频率20MHz

[3],分频器是40-50分频

4,电荷泵电流20uA

5,工艺是smic 55nm

每个模块都有单独的testbench

可送一些仿真,设计参考资料

还有matlab,verilog-a建模推导。

cadence官方手把手教你仿真文档

锁相环的理论推导,相位噪声

呈现最完整的project,大量高清仿真截图和电路截图,非常适合新手学习做报告。

前仿真,无版图,

ID:75269725965240772

模拟芯片设计新手营

锁相环学习电路,有教程

对新手非常友好,一看就懂

锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于电子系统中的时钟同步技术。它可以通过自身的反馈机制,使得输出信号的频率与输入参考信号的频率保持一致,从而实现信号同步。本文将介绍一个锁相环学习电路,旨在为新手提供一个友好、易懂的教程,帮助他们快速理解和掌握锁相环的工作原理和设计方法。

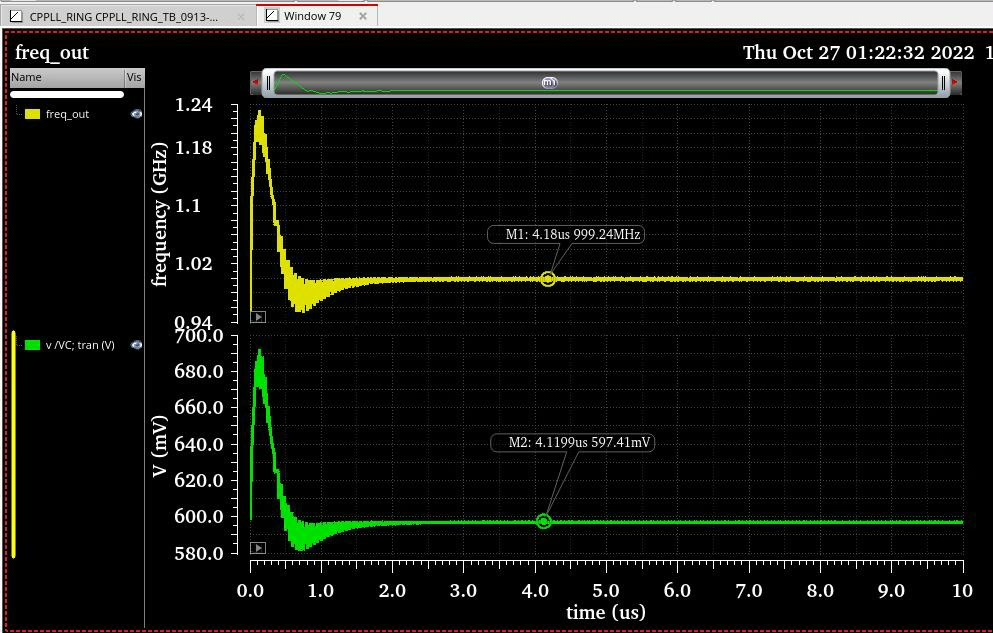

首先,我们来看一下这个锁相环学习电路的基本参数。输出频率可以选择800MHz或者1GHz,采用了Ring_VCO的结构。输入参考频率为20MHz,分频器采用40-50分频。电荷泵电流设置为20uA,工艺使用了smic 55nm。每个模块都有单独的testbench,方便进行仿真测试。而且,我们还提供了一些仿真和设计参考资料,如matlab和verilog-a建模推导。此外,cadence官方也提供了手把手教你仿真的文档,帮助新手快速上手。

在锁相环学习电路的设计过程中,理论推导和相位噪声是两个重要的方面。我们将以最完整的项目呈现,包括大量高清仿真截图和电路截图,这对于新手学习并制作报告非常有帮助。需要注意的是,这是一个前仿真的项目,暂时没有版图设计。

首先,让我们来了解一下锁相环的原理。锁相环主要由相位比较器、环形振荡器(Ring_VCO)、低通滤波器和分频器组成。相位比较器将输入参考信号与环路输出信号进行比较,产生一个误差信号。环形振荡器根据误差信号生成一个振荡信号,其频率与误差信号成正比。低通滤波器用来过滤掉高频噪声,使得振荡信号更加稳定。最后,分频器将振荡信号进行分频,得到输出信号。通过不断调整环形振荡器的频率,锁相环可以使输出频率与输入参考频率保持一致。

在锁相环的设计中,相位噪声是一个非常重要的指标。相位噪声是指输出信号相位的不稳定性,主要来源于环形振荡器和参考信号的噪声。为了降低相位噪声,我们需要选择合适的环形振荡器结构,并进行适当的滤波和去噪处理。

在实际的锁相环设计中,仿真测试是不可或缺的一步。通过仿真,我们可以评估锁相环的性能指标,检测设计中的问题,并进行参数优化。为了方便学习者进行仿真测试,我们为每个模块都提供了单独的testbench,可以直接加载到仿真工具中进行使用。

同时,在本项目中,我们也提供了一些仿真和设计参考资料,如matlab和verilog-a建模推导。这些资料可以帮助学习者更好地理解锁相环的原理和设计方法。此外,cadence官方也提供了一份详细的文档,手把手教学如何进行仿真,对于新手来说非常友好。

综上所述,锁相环学习电路是一个针对新手的教程,致力于提供一个友好、易懂的锁相环学习平台。通过学习这个电路,新手可以快速了解锁相环的工作原理和设计方法。我们提供了大量高清仿真截图和电路截图,以及一些仿真和设计参考资料,帮助新手进行实际的仿真和设计工作。同时,cadence官方也提供了详细的手把手教学文档,为新手提供更多的帮助。希望本教程能够对学习者有所启发,帮助他们在锁相环的领域取得更好的成就。

参考文献:

[1] Smith J. Phase-Locked Loops: Design, Simulation, and Applications[M]. McGraw-Hill, 2003.

【相关代码,程序地址】:http://fansik.cn/725965240772.html

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?