#include <bits/stdc++.h>

using namespace std;

const int N=2e5+10;

typedef long long LL;

LL res[N];

int main()

{

int t;

cin>>t;

while(t--)

{

int n;

cin>>n;

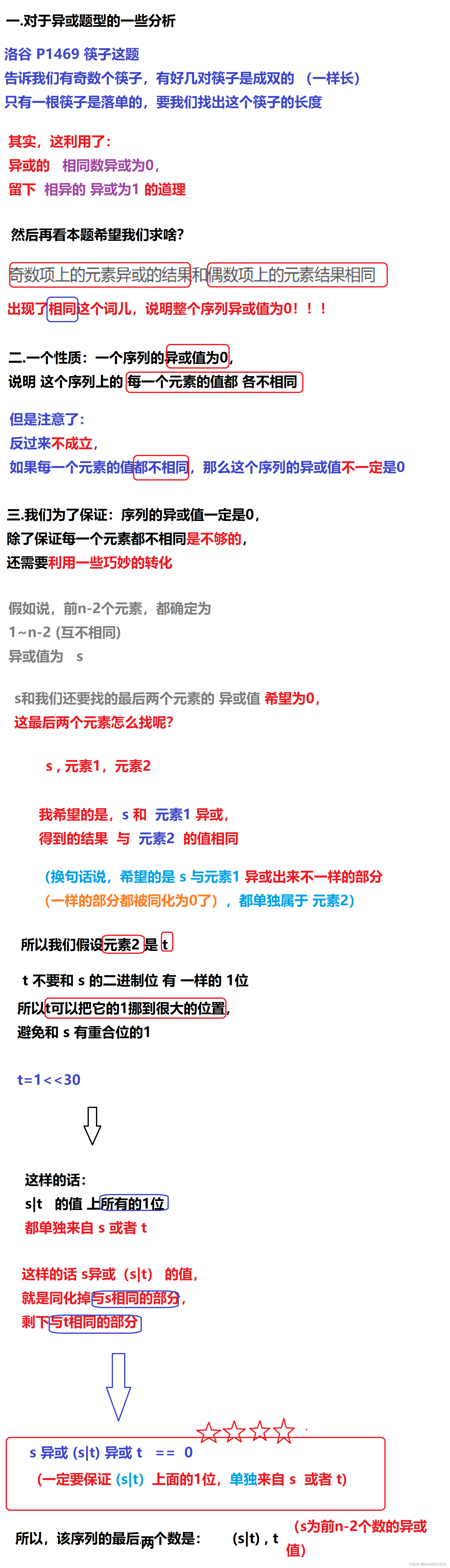

int s=0;

for(int i=0;i<n-2;i++)

{

res[i]=i;

s^=i;

}

if(s==0)

{

res[0]=(1<<30)-1;

s=(1<<30)-1;

}

res[n-2]=s|(1<<30);

res[n-1]=1<<30;

for(int i=0;i<=n-1;i++)

{

cout<<res[i]<<" ";

}

cout<<endl;

}

return 0;

}

1407

1407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?