年至中旬,FPGA行业的求职门槛正悄然提升,这一点在近年来的校招面试中尤为显著。前两年或许还能凭基础问题过关,如今必须做好充分准备才能脱颖而出。

简历打磨指南

简历是敲门砖,确定求职意向后需尽早着手准备。FPGA领域简历需聚焦以下核心:

- 项目选择:精选2-3个最具技术深度的项目,每个项目突出差异化亮点(如高速接口设计、算法硬件加速、时序优化等)

- 技术细节:量化成果数据(如"实现500MHz时钟域跨异步处理"、"资源利用率优化30%")

- 工具链掌握:明确标注使用的EDA工具(Vivado/Quartus/ModelSim)及版本

行业特性决定面试必考专业问题,应对策略:

- 理论实践结合:回答需包含设计原理+实现细节(如"采用四段式状态机设计,通过时序约束解决亚稳态")

- 临场应变:遇难题可分解回答:"这个问题可从三个层面分析……目前我接触较多的是XX场景的应用"

- 心态管理:保持技术探讨的谦逊态度,对未知领域可答:"这个方向我研究尚浅,但根据已有经验推测……"

- 知识体系化:建议按数字电路基础→HDL编码→时序分析→系统设计的路径系统复习

面试全流程解析

典型专业面流程:

自我介绍(5分钟)→项目深挖→技术问答→反问环节

- 自我介绍:外企准备英文版本,重点突显FPGA项目经验(如"Implemented image preprocessing pipeline on Xilinx Zynq-7000 platform")

- 项目防御:提前预演可能追问点(如"时钟域交叉如何处理"、"约束文件编写规范")

- 职责描述:采用STAR法则(Situation情境-Task任务-Action行动-Result结果)阐述项目贡献

项目描述模板

优质项目介绍需包含:

"在XX项目中(如基于FPGA的4K视频编码加速卡),我负责(H.264熵编码模块设计),采用(Verilog实现+流水线优化),达成(吞吐量提升40%同时资源占用减少25%)的技术指标,该成果已应用于(某型无人机视觉系统)"

无项目应对方案:

- 自主设计经典模块(如AXI4总线控制器、NCO发生器)

- 参与开源项目(如OpenCores贡献代码)

- 课程设计深度包装(如"数字信号处理课程设计→基于FPGA的FIR滤波器实现")

大厂面试真题:紫光同创FPGA工程师岗

岗位:FPGA开发工程师

地点:深圳

一面(技术面30分钟)

- 自我介绍(需涵盖FPGA项目经验)

- 详述毕业设计中FPGA加速部分的技术路线

- 解释DDR3控制器设计的时序收敛策略

- 阐述如何用FPGA实现异步FIFO的跨时钟域处理

- 技术追问:

- 谈谈你对Xilinx UltraScale+架构的理解

- 描述一次完整的FPGA开发流程(从需求分析到板级调试)

二面(HR面20分钟)

常规问题:

- 职业规划

- 期望工作地点

- 能否接受项目制工作模式

三面(技术+综合面30分钟)

- 深度技术探讨:

- 如何用FPGA实现动态部分重配置

- 对比ASIC与FPGA在图像处理场景的适用性

- 行为面试:

- 描述最具挑战性的项目攻坚经历

- 如何看待FPGA在AI加速领域的发展

- 开放性问题:

- 设计一个基于FPGA的千兆以太网数据采集系统

- 验证策略:如何确保DMA控制器的数据传输完整性

反问环节建议:

- 团队当前主攻方向(如5G通信/数据中心加速)

- 新员工培养体系(是否包含FPGA高级课程培训)

备考锦囊

- 技术热点:关注Chiplet与FPGA融合、HLS高阶综合、AI加速架构等前沿方向

- 工具进阶:熟练TCL脚本编写、掌握Vivado IP Integrator等高级功能

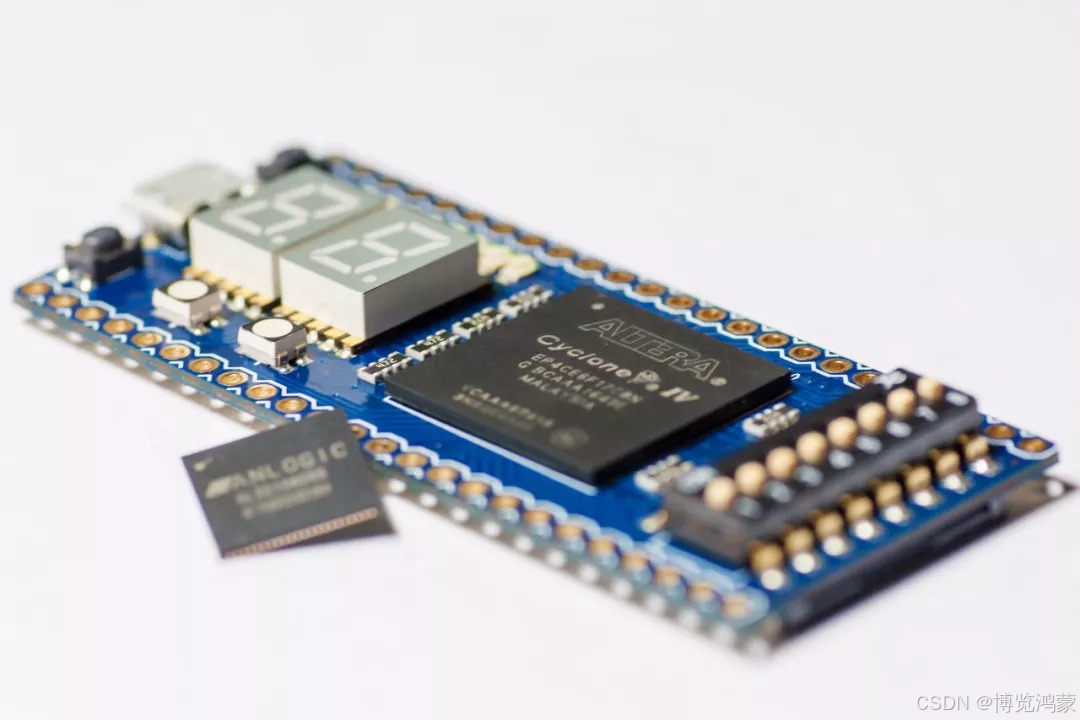

- 实操验证:建议通过Xilinx/Intel官方开发板完成至少1个完整项目

需要FPGA学习资料的同学,可私信留下正确联系方式,宸极教育导师将为您提供定制化学习路径!求职路上,宸极教育伴您成长。

516

516

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?