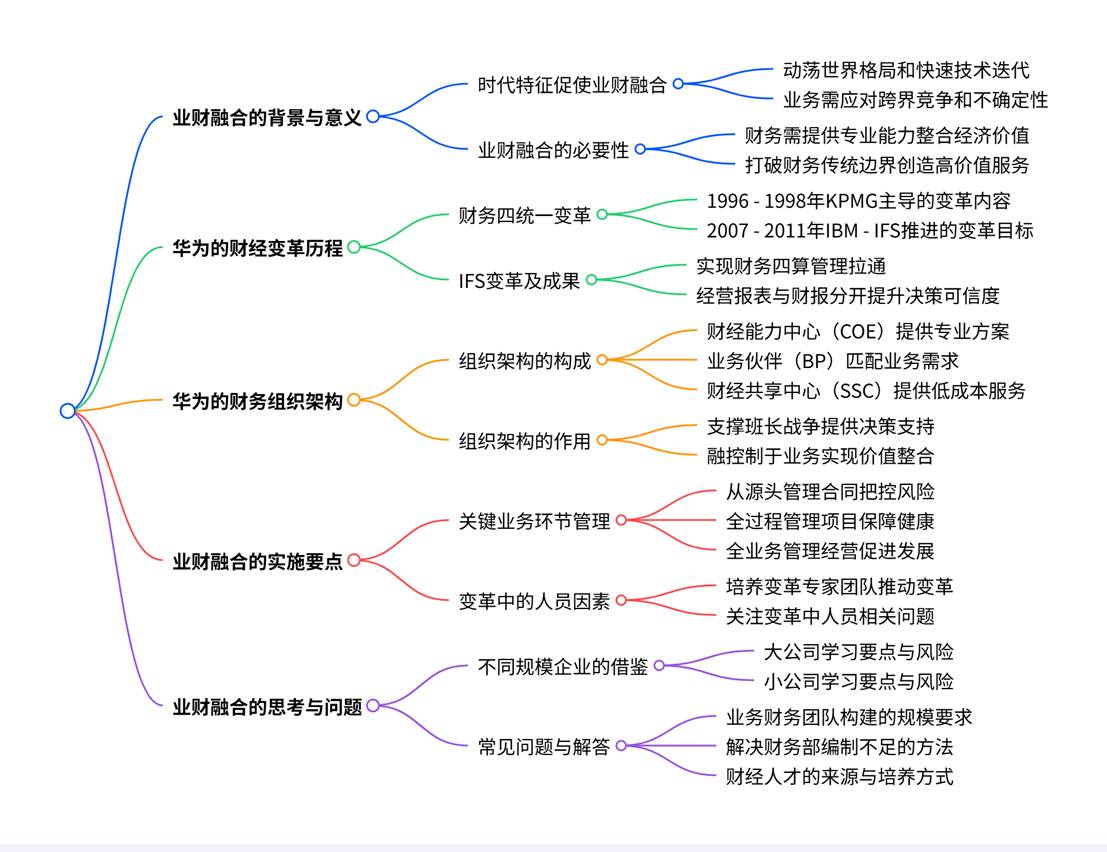

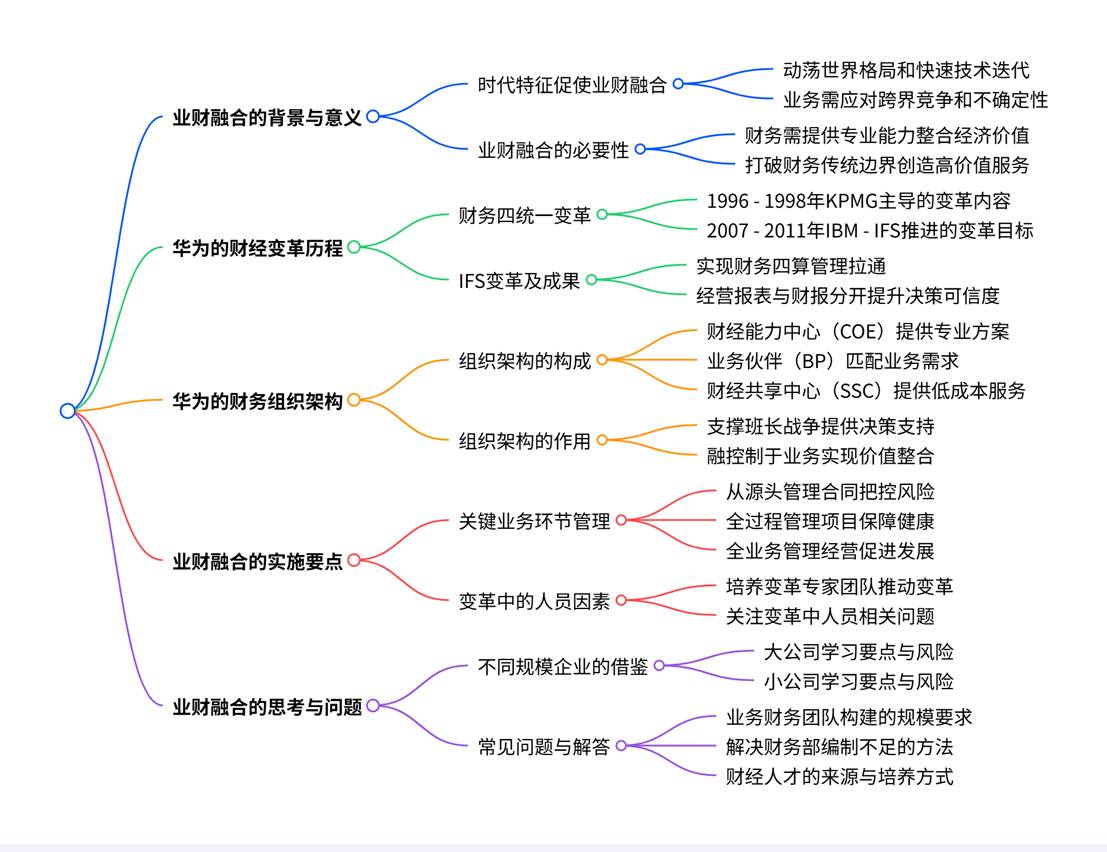

在当今快速变化、竞争激烈的时代,业务面临不确定性,业财融合至关重要。以华为为例,其从财务到财经的转型,历经财务四统一变革、IFS 变革等,构建了包含财经能力中心(COE)、业务伙伴(BP)和财经共享中心(SSC)的财务组织架构 。通过实现财务四算拉通、提升预算预测、项目财务、经营分析能力,赋能经营。同时强调变革要关注人的因素,在业财融合过程中,企业需思考规模与团队构建、人员编制、人才培养等问题,任正非也对 CFO 在业务支持与风险管控方面提出了要求。

在当今快速变化、竞争激烈的时代,业务面临不确定性,业财融合至关重要。以华为为例,其从财务到财经的转型,历经财务四统一变革、IFS 变革等,构建了包含财经能力中心(COE)、业务伙伴(BP)和财经共享中心(SSC)的财务组织架构 。通过实现财务四算拉通、提升预算预测、项目财务、经营分析能力,赋能经营。同时强调变革要关注人的因素,在业财融合过程中,企业需思考规模与团队构建、人员编制、人才培养等问题,任正非也对 CFO 在业务支持与风险管控方面提出了要求。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?