一个典型的CPU(此处讨论的不是某一具体的CPU)由运算器、控制器、寄存器(CPU工作原理)等器件构成,这些器件靠内部总线相连。前一章所说的总线,相对于CPU内部来说是外部总线。内部总线实现CPU内部各个器件之间的联系,外部总线实现CPU和主板上其他器件的联系。简单地说,在CPU中:

运算器进行信息处理;

寄存器进行信息存储

控制器控制各种器件进行工作;

内部总线连接各种器件,在它们之间进行数据的传送。

对于一个汇编程序员来说,CPU中的主要部件是寄存器。寄存器是CPU中程序员可以用指令读写的部件。程序员通过改变各种寄存器中的内容来实现对CPU的控制。

不同的CPU,寄存器的个数、结构是不相同的。8086CPU有14个寄存器,每个寄存器有一个名称。这些寄存是:AX、BX、CX、DX、SI、DI、SP、BP、IP、CS、SS、DS、ES、PSW。我们不对这些寄存器进行一次性的介绍,在课程的进行中,需要用到哪些寄存器,再介绍哪些寄存器。

2.1 通用寄存器

8086CPU的所有寄存器都是16位的,可以存放两个字节。AX、BX、CX、DX这4个寄存器通常用来存放一般性的数据,被称为通用寄存器。

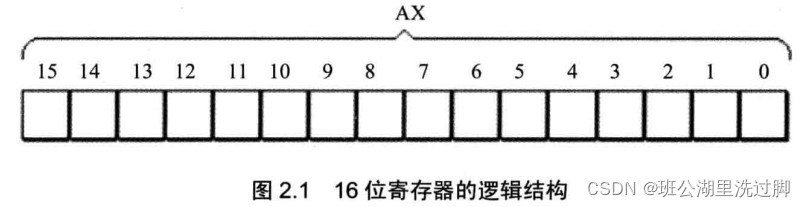

以AX为例,寄存器的逻辑结构如图2.1所示。

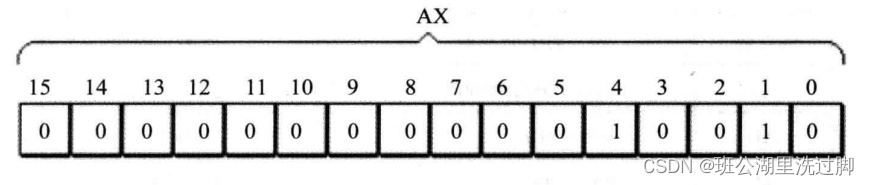

一个16位寄存器可以存储一个16位的数据,数据在寄存器中的存放情况如图2.2所示。

想一想,一个16位寄存器所能存储的数据的最大值为多少? (2的16次方-1 = 65535)

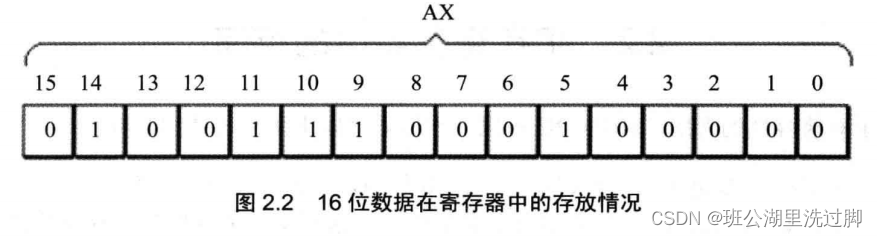

8086CPU的上一代CPU中的寄存器都是8位的,为了保证兼容,使原来基于上代CPU编写的程序稍加修改就可以运行在8086之上,8086CPU的AX、BX、CX、DX这4个寄存器都可分为两个可独立使用的8位寄存器来用:

AX可分为AH和AL

BX可分为BH和BL

CX可分为CH和CL

DX可分为DH和DL

数据:18, 二进制表示: 10010, 在寄存器AX中的存储,

数据:20000, 二进制表示:100111000100000在寄存器AX中的存储:

以AX为例,8086CPU的16位寄存器分为两个8位寄存器的情况如图2.3所示。

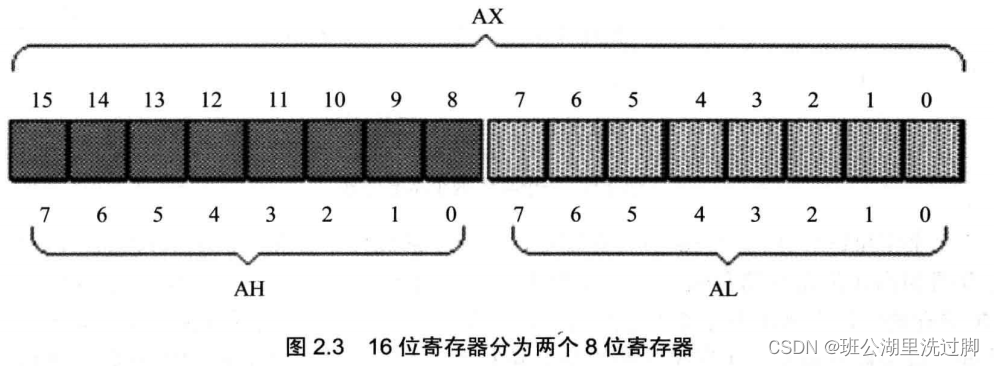

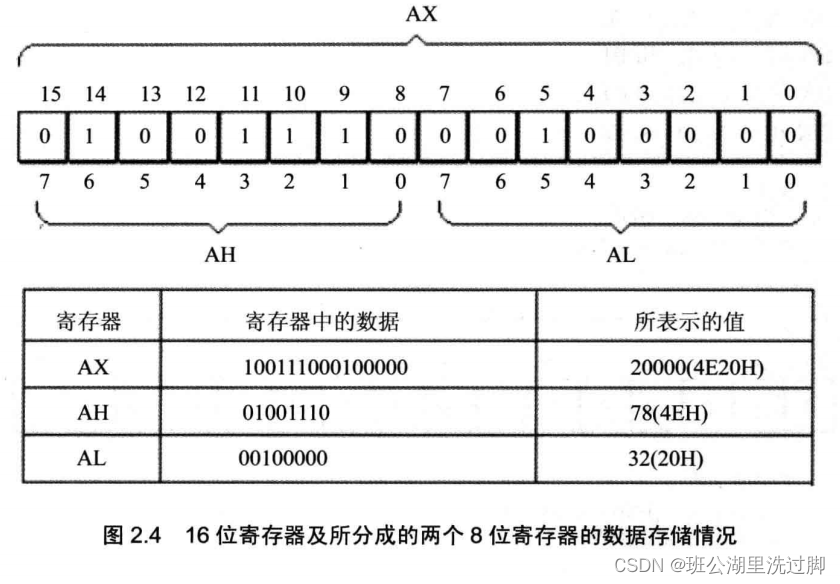

AX的低8位(0位~7位)构成了AL寄存器,高8位(8位~15位)构成了AH寄存器。AH和AL寄存器是可以独立使用的8位寄存器。图2.4展示了16位寄存器及它所分成的两个8位寄存器的数据存储的情况。

想一想,一个8位寄存器所能存储的数据的最大值为多少?(2的8次方-1 = 255)

2.2 字在寄存器中的存储

出于对兼容性的考虑,8086CPU可以一次性处理以下两种尺寸的数据。

字节:记为byte, 一个字节由8个bit组成,可以存在8位寄存器中。

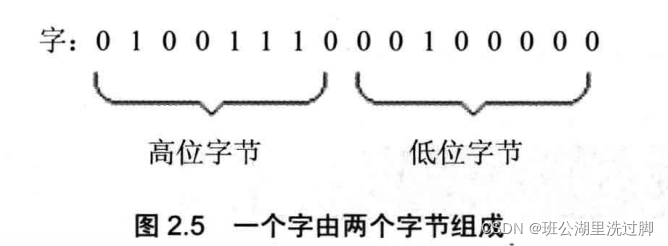

字:记为word,一个字由两个字节组成,这两个字节分别称为这个字的高位字节和低位字节,如图2.5所示。

一个字可以存在一个16位寄存器中,这个字的高位字节和低位字节自然就存在这个寄存器的高8位寄存器和低8位寄存器中。如图2.4所示,一个字型数据20000,存在AX寄存器中,在AH中存储了它的高8位,在AL中存储了它的低8位。AH和AL中的数据,即可以看成是一个字型数据的高8位和低8位,这个字型数据的大小是20000;又可以看成是两个独立字节型数据,它们的大小分别是78和32。

2.3几条汇编指令

通过汇编指令控制CPU进行工作,看一下表2.1中的几条指令

| 汇编指令 | 控制CPU完成的操作 | 用高级语言的语法描述 |

|---|---|---|

| mov ax, 18 | 将18送入寄存器AX | AX=18 |

| mov ah, 78 | 将78送入寄存器AH | AH=78 |

| add ax, 8 | 将寄存器AX中的数值加上8 | AX=AX+8 |

| mov ax, bx | 将寄存器BX中的数据送入寄存器AX | AX=BX |

| add ax, bx | 将AX和BX中的数值相加,结果存在AX | AX=AX+BX |

汇编指令或寄存器名称在编写时不区分大小写,例如: mov ax, 18和MOV AX, 18意思是一样的。

接下来看一下CPU执行表2.2中所列的程序段中的每条指令后,对寄存器中的数据进行改变。

| 程序段中的指令 | 指令执行后AX中的数据 | 指令执行后BX中的数据 |

|---|---|---|

| mov ax, 4E20H | 4E20H | 0000H |

| add ax,1406H | 6226H | 0000H |

| mov bx, 2000H | 6226H | 2000H |

| add ax, bx | 8226H | 2000H |

| mov bx, ax | 8226H | 8226H |

| add ax,bx | ?(参见问题2.1) 044CH | 8226H |

问题2.1

指令执行后AX中的数据为多少?思考后看分析。

分析:

程序段中的最后一条指令add ax, bx,在执行前ax和bx中的数据都为8226H,相加后所得的值为1044CH,但是ax为16位寄存器,只能存放4位十六进制的数据,所以最高位的1不能在ax中保存,ax中的数据为:044CH。

表2.3中所列的一段程序的执行情况

| 程序段中的指令 | 指令执行后AX中的数据 | 指令执行后BX中的数据 |

|---|---|---|

| mov ax, 001AH | 001AH | 0000H |

| mov bx, 0026H | 001AH | 0026H |

| add al, bl | 0040H | 0026H |

| add ah, bl | 2640H | 0026H |

| add bh, al | 2640H | 4026H |

| mov ah,0 | 0040H | 4026H |

| add al, 85H | 00C5H | 4026H |

| add al, 93H | ?(参见问题2.2) | 4026H |

问题2.2

指令执行后AX中的数据为多少?思考 后看分析。

分析:

程序段中的最后一条指令add al, 93H,在执行前,al中的数据为C5H,相加后所得 值为158H,担是al为8位寄存器,只能存放两位十六进制的数据,所以最高位的1丢失,ax中的数据为:0058H.(这里的丢失,指的是进位值不能在8位寄存器中保存,但是CPU并不真的丢弃这个进位值,关于这个问题,我们将在后面的课程中讨论。)

注意,此时al是作为一个独立的8位寄存器来使用的,和ah没有关系,CPU在执行这条指令时认为ah和al是两个不相关的寄存器。不要错误地认为,诸如add al, 93H的指令产生在进位会存储在ah中,add al,93H进行的是8位运算。

如果执行add ax,93H,低8位的进位会存储在ah中,CPU在执行这条指令时认为只有一个16位寄存器ax,进行的是16位运算。指令add ax,93H执行后,ax中的值为:0158H。此时,使用的寄存器是16位寄存器ax, add ax, 93H相当于将ax中的16位数据00C5H和另一个16位数据0093H相加,结果是16位的0158H。

在进行数据传送或运算时,要注意指令的两个操作对象的位数应当是一致的,例如:

mov ax, bx

mov bx, cx

mov ax, 18H

mov al, 18H

add ax, bx

add ax, 20000

等都是正确的指令,而:

mov ax, bl (在8位寄存器和16位寄存器之间传送数据)

mov bh, ax (在16位寄存器和8位寄存吕之间传送数据)

mov al, 20000 (8位寄存器最大可存放值为255的数据)

add al, 100H (将一个高于8位的数据加到一个8位寄存器中)

等都是错误的指令,错误的原因都是指令的两个操作对象的位数不一致。

检测点2.1

(1)写出每条汇编指令执行后相关寄存器中的值。

mov ax, 62627 AX=F4A3H

mov ah, 31H AX=31A3H

mov al,23H AX=3123H

add ax,ax AX=6246H

mov bx,826CH BX=826CH

mov cx,ax CX=6246H

mov ax,bx AX=826CH

add ax,bx AX=04D8H

mov al,bh AX=0482H

mov ah,bl AX=6C82H

add ah,ah AX=D882H

add al,6 AX=D888H

add al,al AX=D810H

mov ax,cx AX=6246H

(2)只能使用目前学过的汇编指令,最多使得4条指令,编程计算2的4次方。

mov ax, 2

add ax, ax

add ax, ax

add ax, ax

2.4 物理地址

我们知道,CPU访问内存单元时,要给出内存单元的地址。所有的内存单元构成的存储空间是一个一维的线性空间,每一个内存单元在这个空间中都是唯一的地址,我们将这个唯一的地址称为物理地址。

CPU通过地址总线送入存储器的,必须是一个内存单元的物理地址。在CPU向地址总线上发现物理地址之前,必须要在内部先形成这个物理地址。不同的CPU可以有不同的形成物理地址的方式。我们现在讨论8086CPU是如何在内部形成内存单元的物理地址的。

2.5 16位结构的CPU

我们说8086CPU的上一代CPU(8080,8085)等是8位机,而8086是16位机,也可以说8086是16位结构的CPU。那么什么是16位结构的CPU呢?

概括地讲,16位结构(16位机、字长为16位等常见说法,与16位结构的含义相同)描述了一个CPU具有下面几方面的结构特性。

运算器一次最多可以处理16位的数据;

寄存器的最大宽度为16位;

寄存器和运行器之间的通路为16位。

8086是16位结构的CPU,这也就是说,在8086内存,能够一次性处理、传输、暂时存储的信息的最大长度是16位的。内存单元的地址在送上地址总线之前,必须在CPU中处理、传输、暂时放,对于16位CPU,能一次性处理、传输、暂时存储16位的地址。

2.6 8086CPU给出物理地址的方法

8086CPU有20位地址总线,可以传送20位地址,达到1MB寻址能力。8086CPU又是16位结构,在内部一次性处理、传输、暂时存储的地址为16位。从8086CPU的内部结构来看,如果将地址从内部简单地发出,那么它只能送出16位的地址,表现出的寻址能力吸有64KB。8086CPU采用一种在内部用两个16位地址合成的方法来形成一个20位的物理地址。

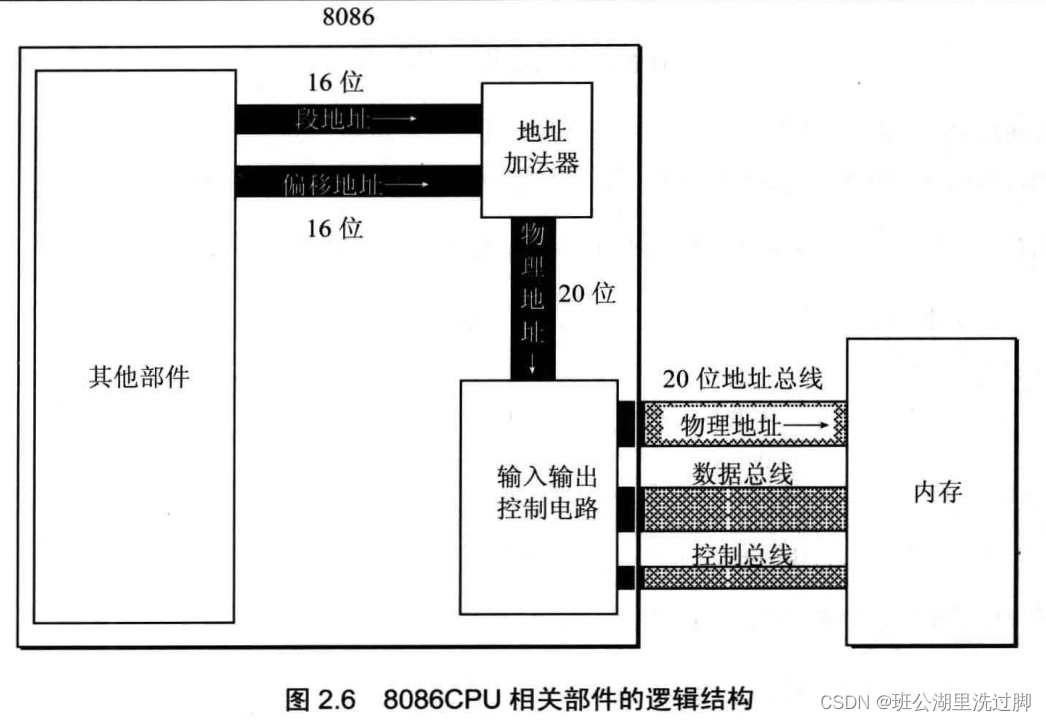

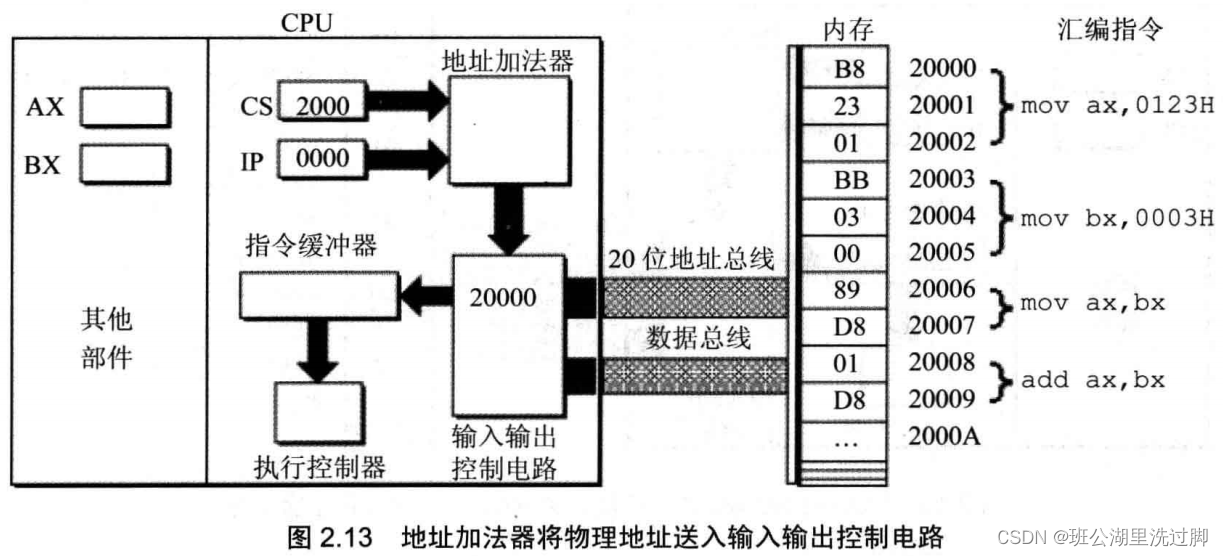

8086CPU相关部件的逻辑结构如图2.6所示。

如果2.6所示,当8086CPU要读写内存时:

(1)CPU中的相关部件提供两个16位的址,一个称为段地址,另一个称为偏移地址

(2)段地址和偏移地址通过内部总线送入一个称为地址加法器的部件

(3)地址加法器将两个16位地址合成为一个20位的物理地址

(4)地址加法器通过内部总线将20位物理地址送 入输入输出控制电路

(5)输入输出控制电路将20位物理地址送上地址总线;

(6)20位物理地址被地址总线传送到存储器。

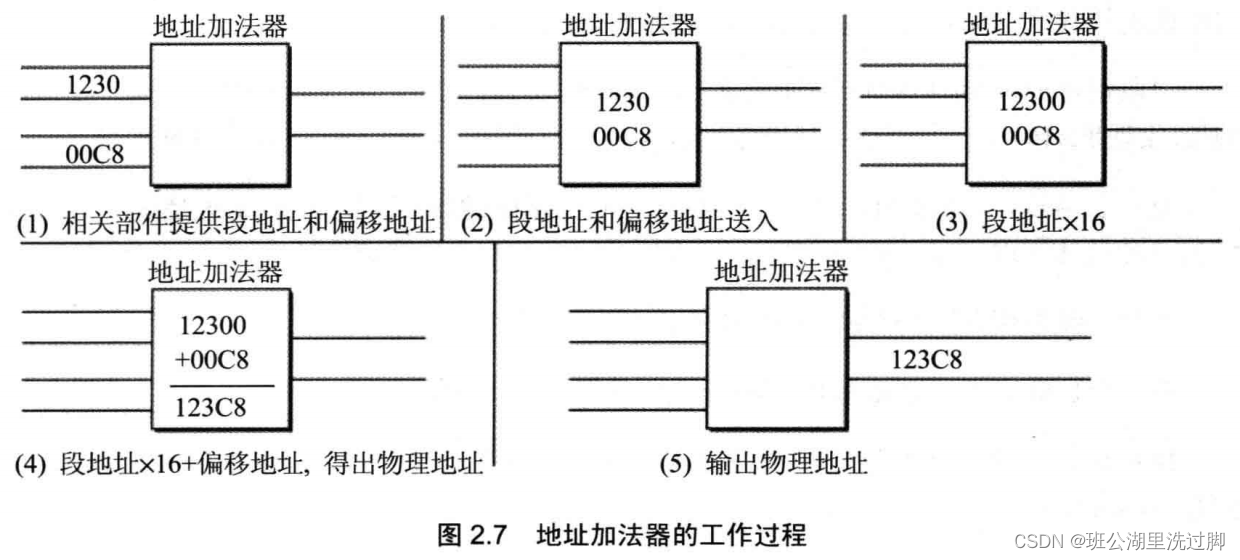

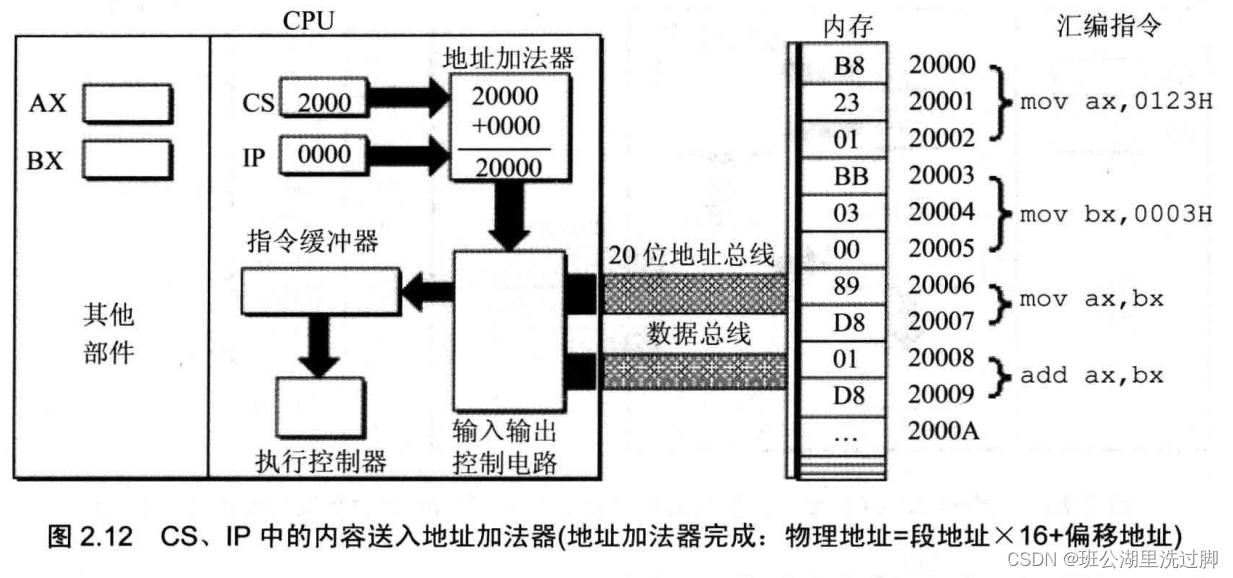

地址加法器采用物理地址=段地址X16+偏移地址的方法用段地址和偏移地址合成物理地址(20位)。例如,8086CPU要访问地址为123C8H的内存单元,此时,地址加法器的工作过程如图2.7所示(图中数据绋为16进制表示)

由段地址X16引发的讨论

“段地址X16”有一个更为常用的说法是左移4位,计算机中的所有信息都是以二进制的形式存储的,段地址当然也不例外。机器只能处理二进制信息,“左移4位”中的位,指的是二进制位。

我们看一个例子,一个数据为2H,二进制形为10B,对其进行左移运算:

| 左移位数 | 二进制 | 十六进制 | 十进制 |

|---|---|---|---|

| 0 | 10B | 2H | 2 |

| 1 | 100B | 4H | 4 |

| 2 | 1000B | 8H | 8 |

| 3 | 10000B | 10H | 16 |

| 4 | 100000B | 20H | 32 |

观察上面移位次数和各种形式数据的关系,我们可以发现:

(1)一个数据的二进制形式左移1位,相当于该数据乘以2

(2)一个数据的二进制形式左移N位,相当于该数据乘以2的N次方

(3)地址加法器如何完成段地址X16的运算?就是将以二进制形式存放的段地址左移4位。

进一步思考,我们可看出:一个数据的十六进制形式左移1位,相当于乘以16;一个数据的十进制形式左移1位,相当于乘以10game个X进制的数据左移1位,相当于乘以X。

2.7 “段地址X16+偏移地址=物理地址”的本质含义

注意,这里讨论的是8086CPU段地址和偏移地址的本质含义,而不是为了解闷在具体的问题而在本质含义之上引申出来的更高级的逻辑意义。不管以多少种不同的逻辑意义去看待“段地址X16+偏移地址=物理地址”的寻址模式,一定要清楚地知道它的本质含义,这样才能更灵活地利用它来分析、解决问题。如果只拘泥于某一种引申出来的逻辑含义,而模糊本质含义的话,将从意识上限制对这种寻址功能的灵活应用。

“段地址X16+偏移地址=物理地址”的本质含义是:CPU在访问内存时,用一个基础地址(段地址X16)和一个相对于基础地址的偏移地址相加,给出内存单元的物理地址。

更一般地说,8086CPU的这种寻址功能 是“基础地址+偏移地址=物理地址”寻址模式的一种具体实现方案。8086CPU中,段地址X16可看作是基础地址。

2.8 段的概念

我们注意到,“段地址”这个名称中 包含着“段”的概念。这种说法可能对一些学习者产生了误导,

使人误以为内存被划分成了一个一个的段,每一个段有一个段地址。如果我们在一开始形成了这种

认识,将影响以后对汇编语言的深入理解和灵活应用。

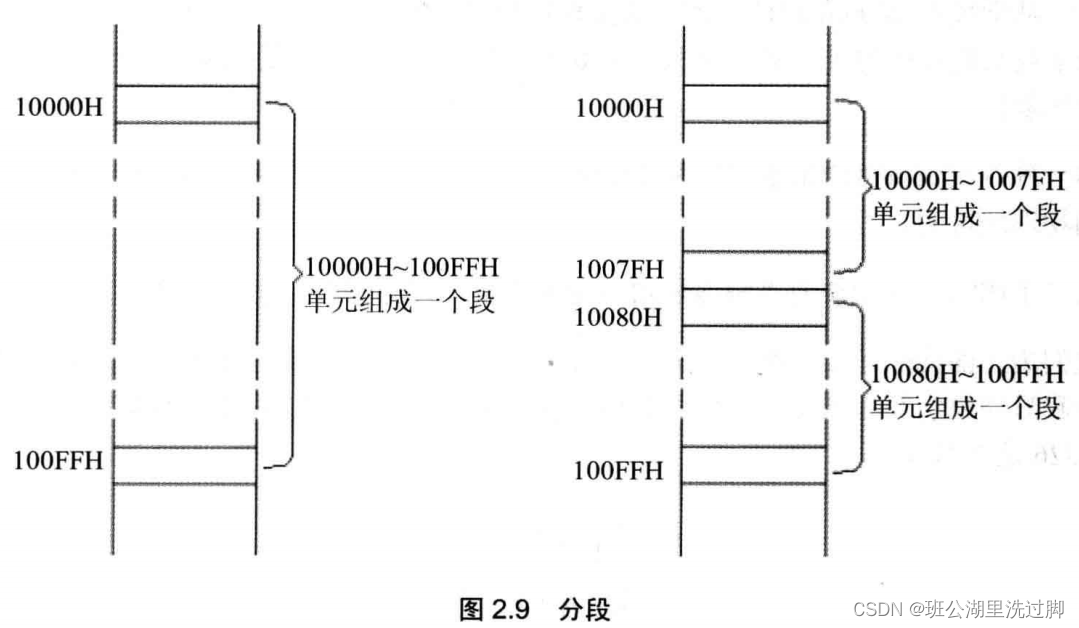

其实,内存并没有分段,段的划分来自于CPU,由于8086CPU用“基础地址(段地址X16)+偏移地址=物理地址”的方式给出内存单元的物理地址,使得我们可以用分段的方式来管理内存。如图2.9所示,我们可以认为:地址10000H~100FFH的内存单元组成一个段,该段的起始地址(基础地址)为10000H,段地址为1000H,大小为100H,我们也可以认为地址10000H~1007FH、10080H~100FFH的内存单元组成两个段,它们的起始地址(基础地址)为:10000H和10080H,段地址为:1000H(乘16=10000H)和1008H(乘16=10080H),大小都是80H。

以后,在编程时可以根据需要,将若干地址连续的内存单元看作一个段,用段地址X16定位段的超始地址(基础地址),用偏移地址定位段中的内存单元。有两点需要注意:段地址X16必然是16的倍数,所以一个段的起始地址也一定是16的倍数;偏移地址为16位,16位地址的寻址能力为64KB,所以一个段的长度最大为64KB。

内存单元地址小结

CPU访问内存单元时,必须向内存提供内存单元的物理地址。8086CPU在内部用段地址和偏移地址移位相加的方法形成最终的物理地址。

思考下面的两个问题。

(1)观察下面的地址,你有什么发现?

物理地址 段地址 偏移地址

21F60H 2000H 1F60H

2100H 0F60H

21F0H 0060H

21F6H 0000H

1F00H 2F60H

结论:CPU可以用不同的段地址和偏移地址形成同一个物理地址。

比如CPU要访问21F60H单元,则它给出的段地址SA和偏移地址EA满足SA X 16 + EA = 21F60H即可。

(2)如果给定一个段地址,仅通过变化偏移地址来进行寻址,最多可定位多少个内存单元?

结论:偏移地址16位,变化范围为0~FFFFH,仅用偏移地址来寻址最多可寻64KB个内存单元。

比如给定段地址1000H,用偏移地址寻址,CPU的寻址范围为10000H~1FFFFH。

在8086PC机中,存储单元的地址用两个元素来描述,即段地址和偏移地址。

“数据在21F60H内存单元中。”这句话对于8086PC机一般不这样讲,取而代之的是两种类似的说法:1、数据存在内存2000:1F60单元中;2、数据存在内存的20000Have段中的1F60H单元中。这两种描述都表示“数据在内存21f60h单元中”。

可以根据需要,将地址连接、超始地址为16的倍数的一组内存单元定义为一个段。

检测点2.2

(1)给定段地址为0001H,仅通过变化偏移地址寻址,CPU的寻址范围为0010H到1000FH。

(2)有一数据存放在内存20000H单元中,现给定段地址为SA,若想用偏移地址寻到此单元,则SA应满足的条是:最小为1001H 最大为2000H。

提示,反过来思考一下,当段地址给定为多少,CPU无论怎么变化偏移地址都无法寻到20000H单元?

2.9 段寄存器

我们前面讲到,8086CPU的访问内存时要由相关部提供内存单元的段地址和偏移地址,送入地址加法器合成物理地址。这里,需要看一下,是什么部件提供段地址。段地址为8086CPU的段寄存器中存放。8086CPU有4个段寄存器:CS、DS、SS、ES。当8086CPU要访问内存时由这4个段寄存器提供内存单元的段地址。本单中只看一下CS。

2.10 CS和IP

CS和IP是8086CPU中两个最关键的寄存器,它们指示了CPU当前要读取指令的地址。CS为代码段寄存器,IP为指令指针寄存器,从名称上我们可以看出它们和指令的关系 。

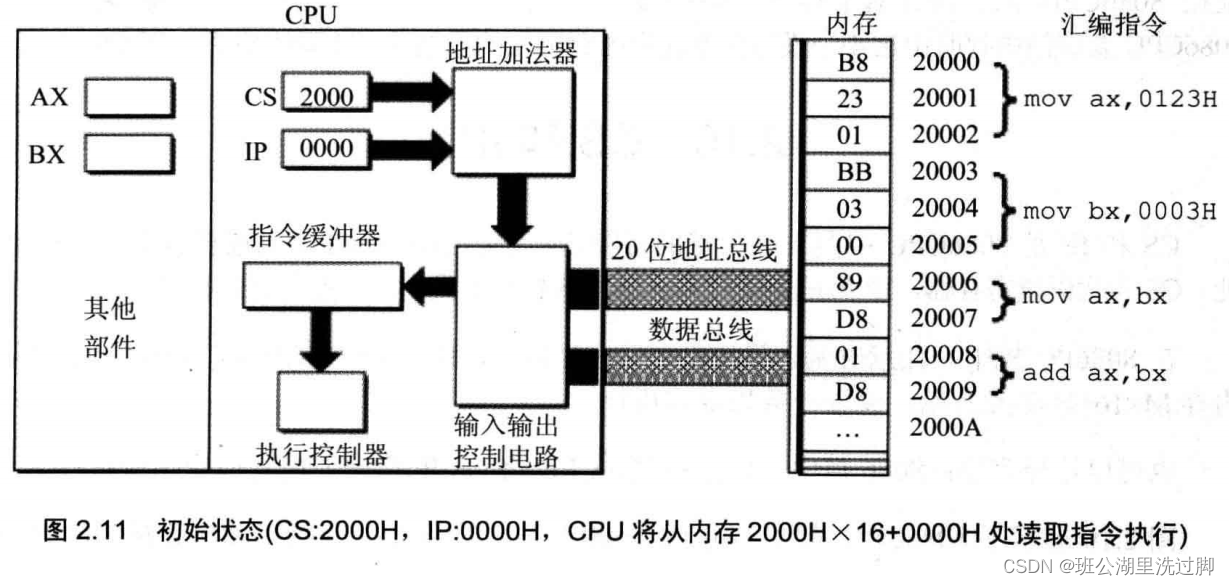

在8086PC机中,任意时刻,设CS中的内容为M,IP中的内容为N,8086CPU将从内存M X 16+N单元开始,读取一条指令并执行。

也可以这样表述:8086机中,任意时刻,CPU将CS:IP指向的内容当作指令执行。

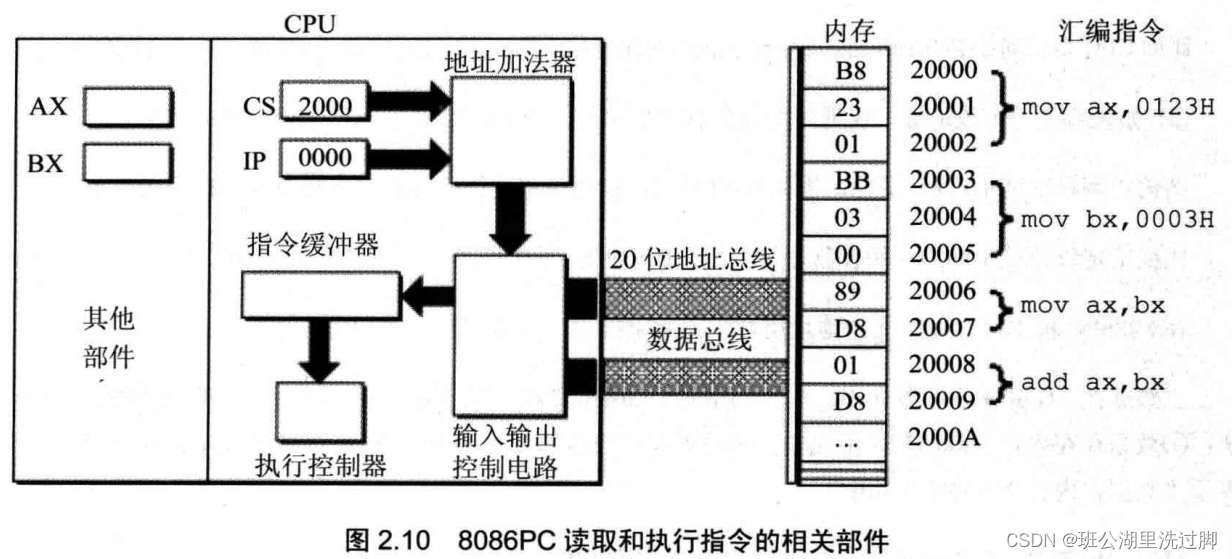

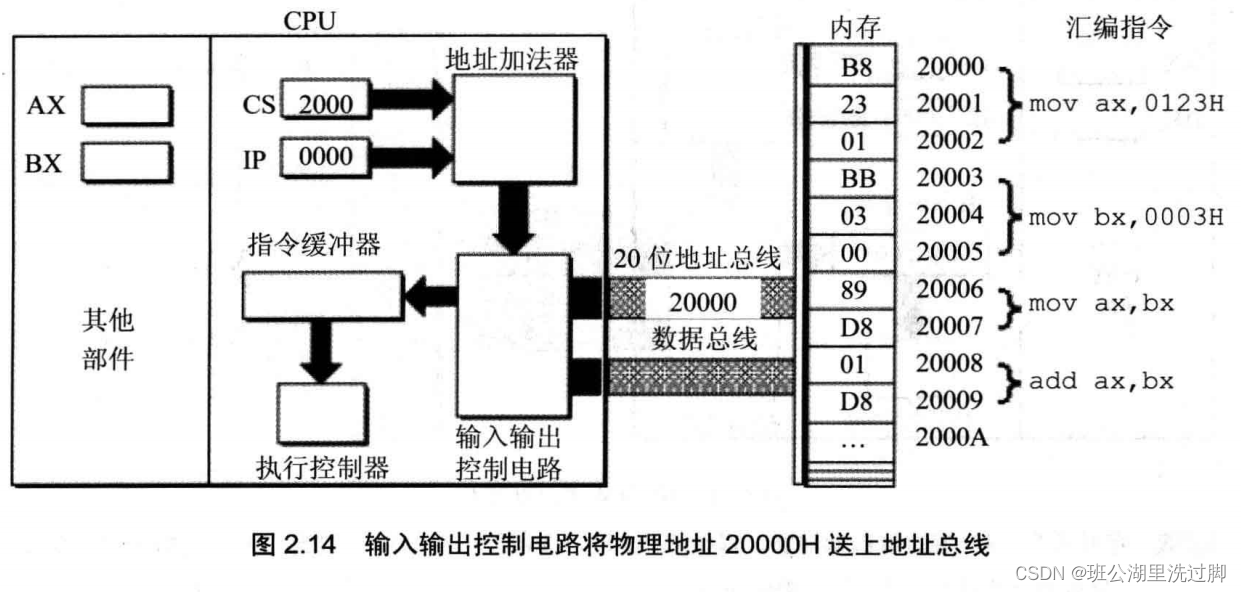

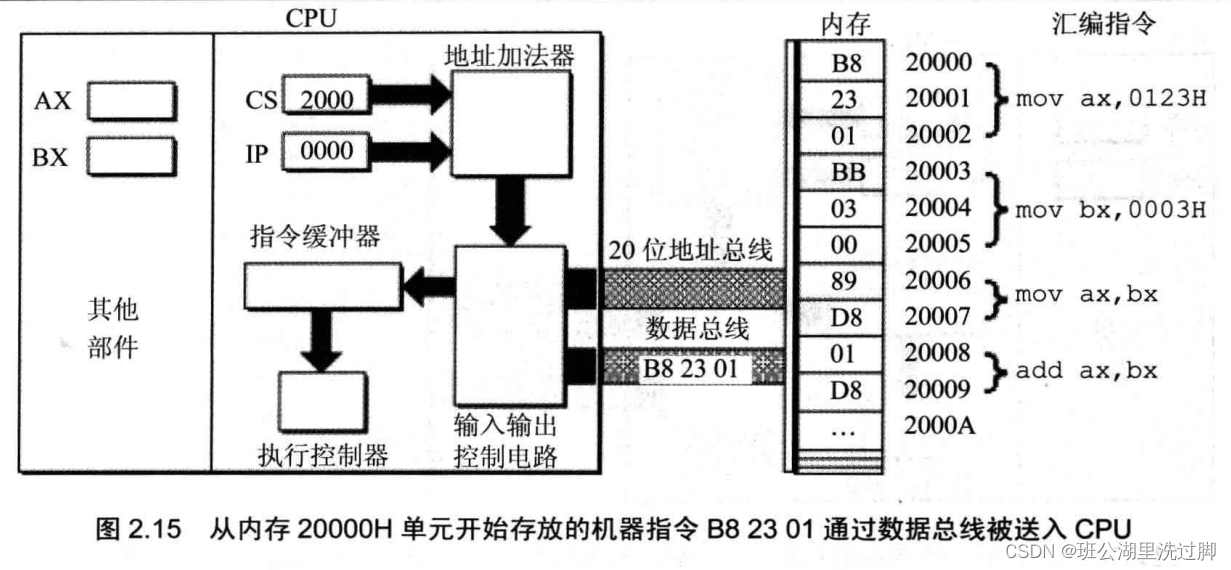

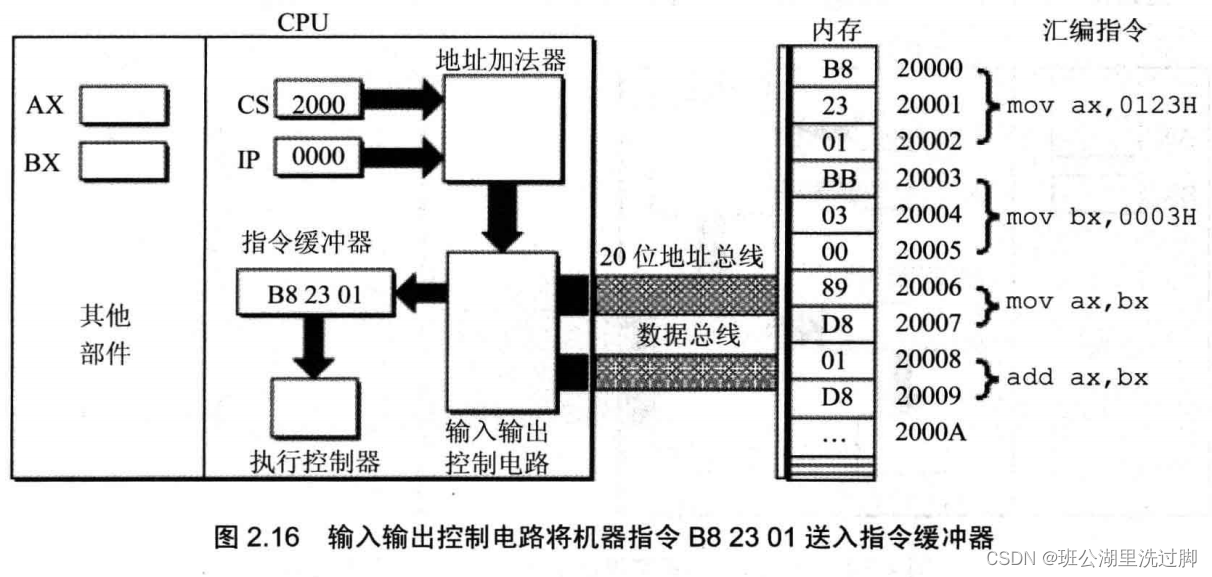

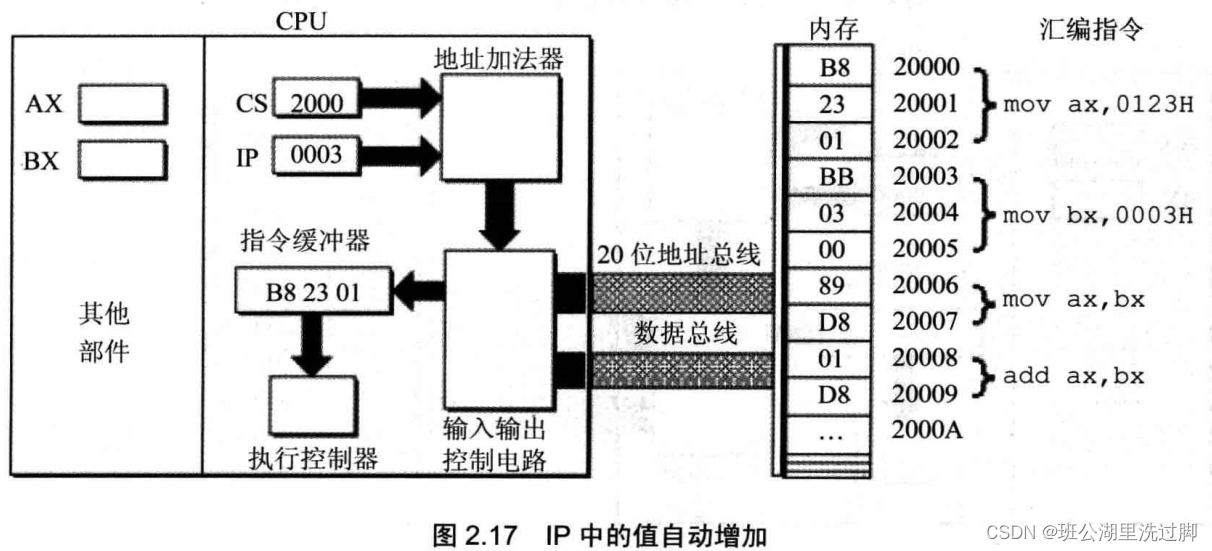

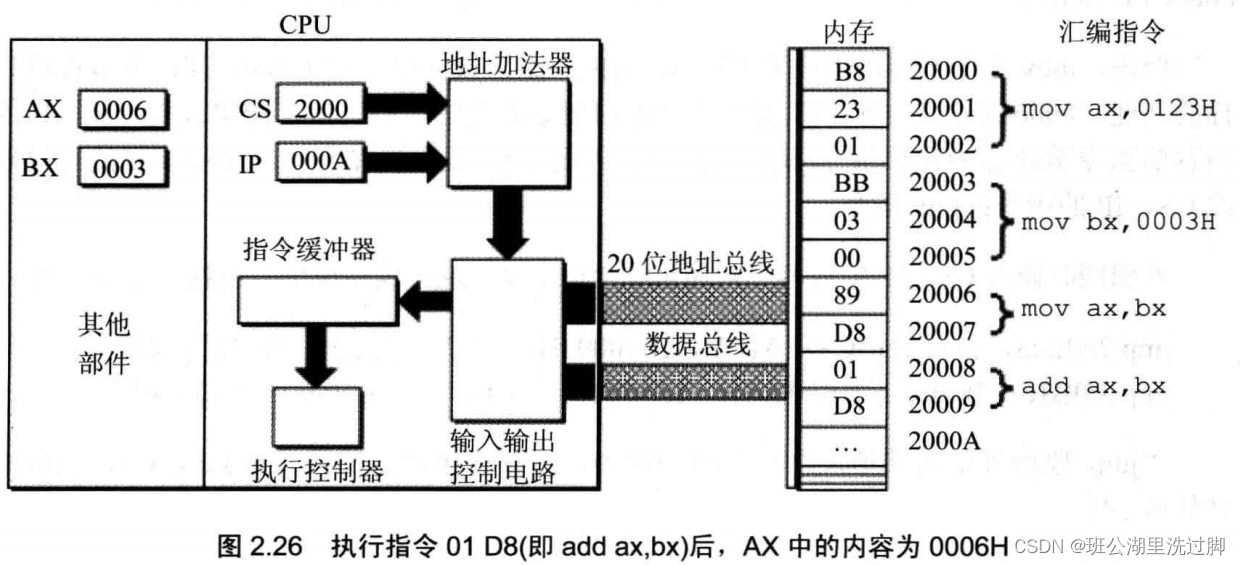

图2.10展示了8086CPU读取、执行指令的工作原理(图中只包括了和所要说明的问题密切相关的部件,图中数字都为十六进制)

图2.10说明如下。

(1)8086CPU当前状态:CS中的内容为2000H,IP中的内容为000H;

(2)内存20000H~20009H单元存放着可执行的机器码;

(3)内存20000H~20009H单元中存放的机器码对应的汇编指令如下。

地址:20000H~20002H,内容:B8 23 01,长度:3Byte,对应汇编指令:mov ax, 0123H

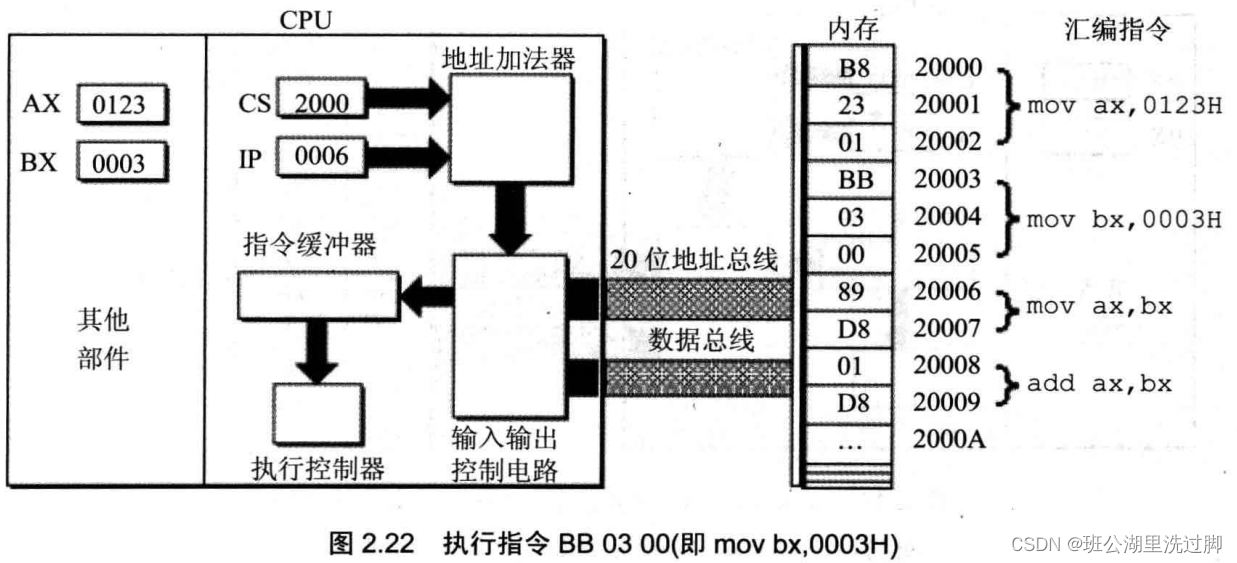

地址:20003H~20005H,内容:BB 03 00,长度:3Byte,对应汇编指令:mov bx, 0003H

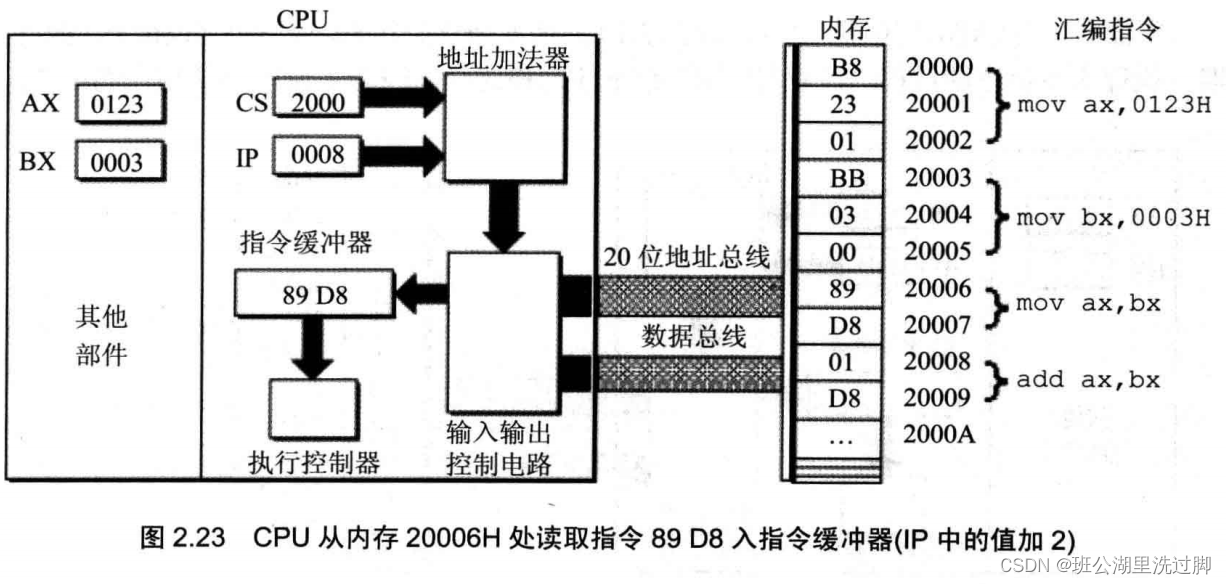

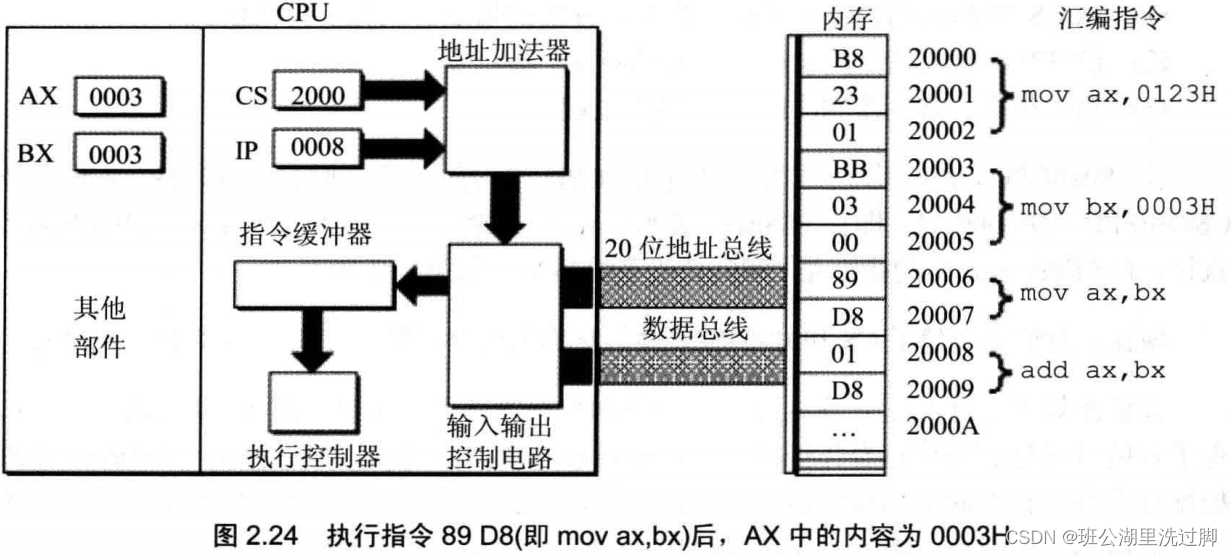

地址:20006H~20007H,内容:89 D8,长度:2Byte,对应汇编指令:mov ax,bx

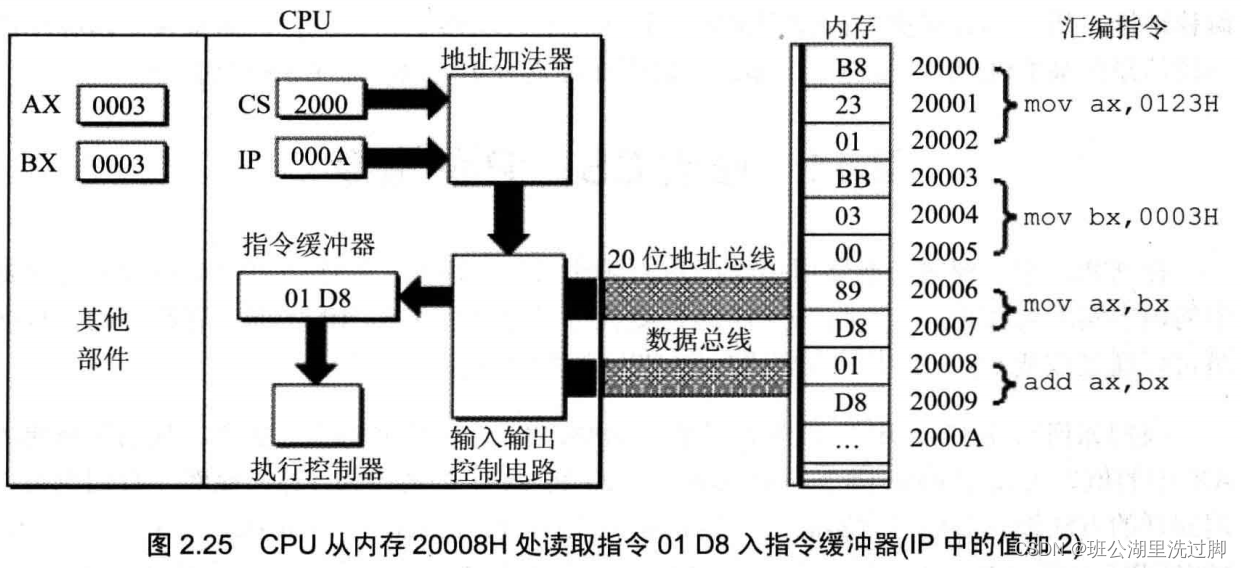

地址:20008H~20009H,内容:01 D8,长度:2Byte,对应汇编指令:add ax,bx

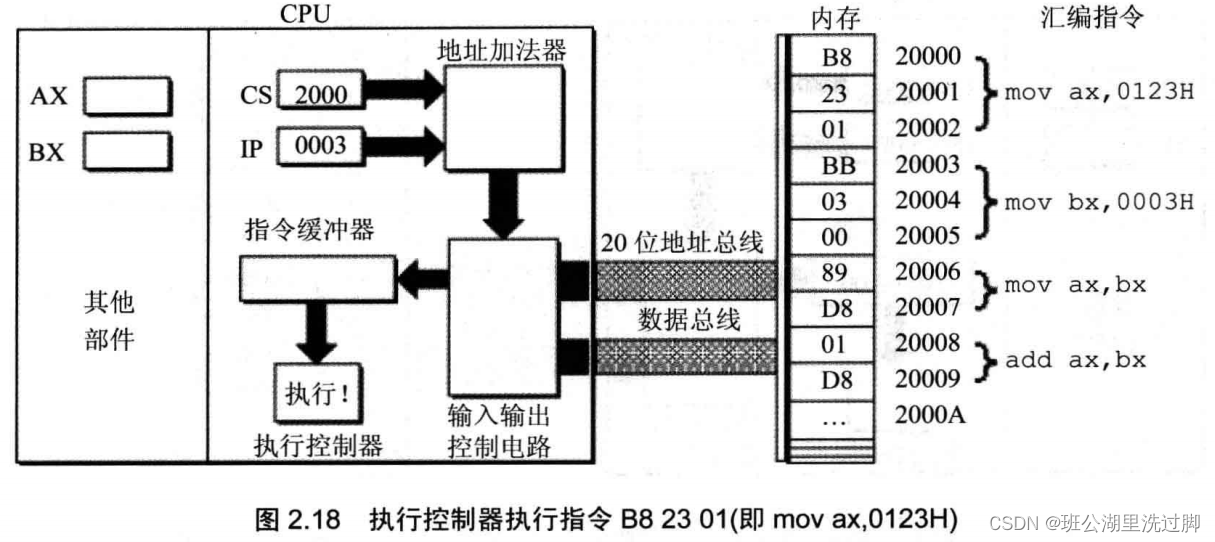

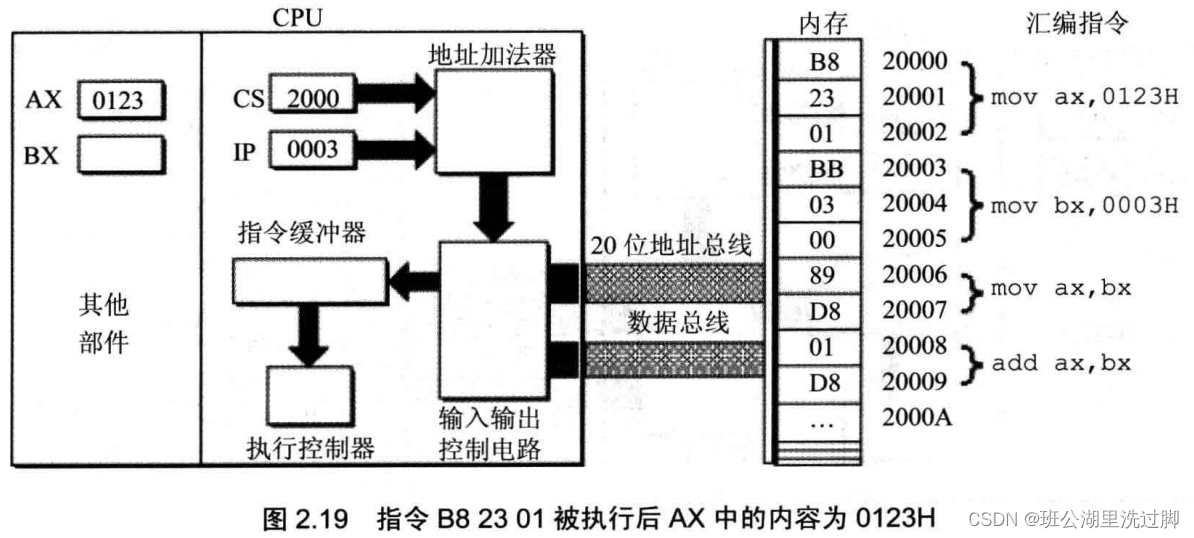

下面的一组图(图2.11~2.19),以图2.10描述的情况为初始状态,展示了8086CPU读取、执行一条指令的过程。注意每幅图中发生的变化(下面对8086CPU的描述,是在逻辑结构、宏观过程的层面上进行的,目的是使读者对CPU工作原理有一个清晰、直观的认识,为汇编语言的学习打下基础。其中隐藏了CPU的物理结构以及具体的工作细节)。

读取一条指令后,IP中的值自动增加,以使CPU可以读取下一条指令。因当前读入的指令B82301长度为3个字节,所以IP中的值为3。此时,CS:IP指向内存单元2000:0003。

此时,CPU将从内存单元2000:0003处读取指令

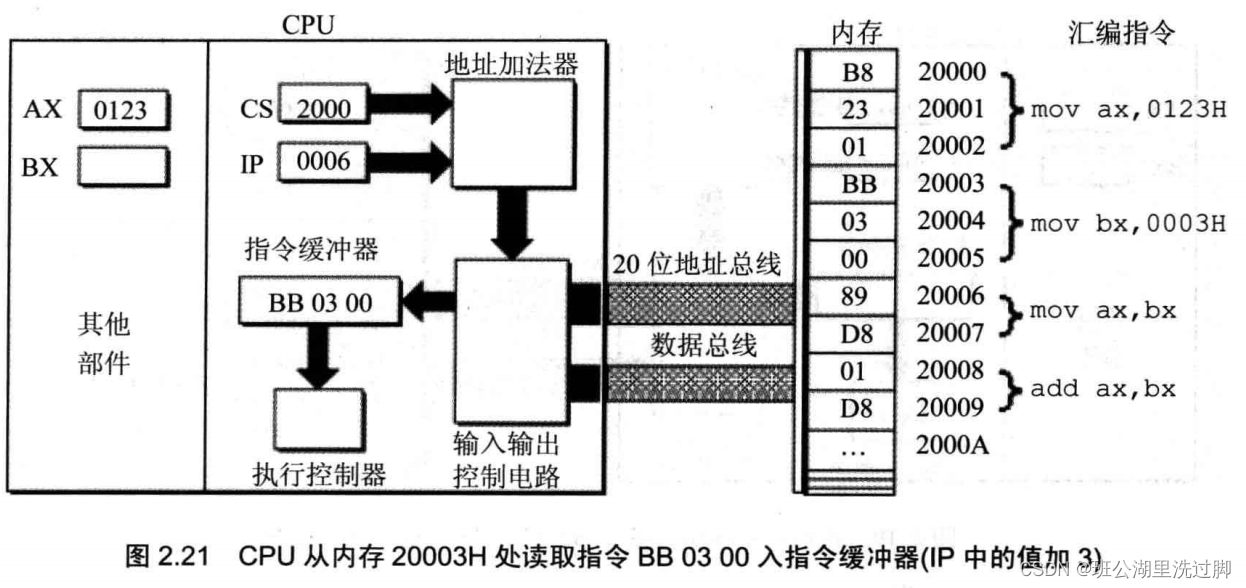

下面的一组图(图2.20~图2.26),以图2.19的情况为初始状态,展示了8086CPU继续读取、执行3条指令的过程。注意IP的变化(下面的描述中,隐蔽了读取每条指令的细节)。

通过上面的过程展示,8086CPU的工作过程可以简要描述如下。

(1)从CS:IP指向的内存单元读取指令,读取的指令进入指令缓冲器。

(2)IP=IP+所读取指令的长度,从而指向下一条指令;

(3)执行指令。转到步骤(1),重复这个过程。

在8086CPU加电启动或复位后(即CPU刚开始工作时)CS和IP被设置为CS=FFFFH,IP=0000H,即在8086PC机刚启动时,CPU从内存FFFF0H单元中读取指令执行,FFFF0H单元中的指令是8086PC机开机后执行的第一条指令。

现在,我们更清楚了CS和IP的重要性,它们的内容提供了CPU要执行指令的地址。

我们在第1章中讲过,在内存中,指令和数据没有任何区别,都是二进制信息,CPU在工作的时候把有的信息看作指令,有的信息看作数据。现在,如果提出一个问题:CPU根据什么将内存中的信息看作指令?如何回答?我们可以说,CPU将CS:IP指向的内存单元中的内容看作指令,因为,在任何时候,CPU和CS、IP中的内容当作指令的段地址和偏移地址,用它们合成指令的物理地址,到内存中坊取指令码,执行。如果说,内存中一段信息曾被CPU执行过的话,那么,它所在的内存单元必然被CS:IP指向过。

2.11 修改CS、IP的指令

在CPU中,程序中能够用指令读写的部件只有寄存器,程序员可以通过改变寄存器中的内容实现对CPU的控制。CPU从何处执行指令是由CS、IP中的内容决定的,程序员可以通过改变CS、IP中的内容来控制CPU执行目标指令。

我们如何改变CS、IP的值呢?显然,8086CPU必须提供相应的指令。我们如何修改AX中的值?可以用mov指令,如mov ax,123将ax中的值设为123,显然,我们也可以用同样的方法设置其他寄存器的值,如mov bx,123, mov cx,123, mov dx,123等。其实,8086CPU大部分寄存器的值,都可以用mov指令来改变,mov指令被称为传送指令。

但是,mov指令不能用于设置CS、IP的值,原因很简单,因为8086CPU没有提供这样的功能。8086CPU为CS、IP提供了另外的指令来改变它们的值。能够改变CS、IP的内容的指令被统称为转移指令(我们以后会深入研究)。我们现在介绍一个最简单的可以修改CS、IP的指令;jmp指令。

若想同时修改CS、IP的内容,可以形如“jmp 段地址:偏移地址”的指令完成,如

jmp 2AE3:3,执行后:CS=2AE3H, IP=0003H,CPU将从2AE33H处理读取指令。

jmp 3:0B16,执行后:CS=0003H, IP=0B16H, CPU将从00B46H处理读取指令。

“jmp 段地址:偏移地址”指令的功能为:用指令中给出的段地址修改CS,偏移地址修改IP。

若想仅修改IP的内容,可用形如“jmp 某一合法寄存器”的指令完成,如

jmp ax, 指令执行前:ax=1000H, CS=2000H, IP=003H

指令执行后:ax=1000H, CS=2000H, IP=1000H

jmp bx, 指令执行前:bx=0B16H, CS=2000H, IP=0003H

指令执行后:bx=0B16H, CS=2000H, IP=0B16H

"jmp 某一合法寄存器"指令的功能为:用户寄存器的值修改IP.

jmp ax,在含义上好似:mov IP, ax.

注意,我们在适当的时候,会用已知的汇编指令的语法来描述新学的汇编指令的功能。采用一种“用汇编解释汇编”的方法来使用读者更好地理解汇编指令的功能,这样做有助于读者进行知识的相互融会。要强调的是,我们是用“已知的汇编”指令的语法进行描述,并不是用“已知的汇编指令”来描述,比如,我们用mov IP,ax来描述jmp ax,并不是说真有mov IP,ax这样的指令,而用mov指令的语法来说jmp指令的功能。我们以用同样的方法描述jmp 3:01B6的功能: jmp 3:01B6在含义上好似mov CS,3 mov IP,01B6.

问题2.3

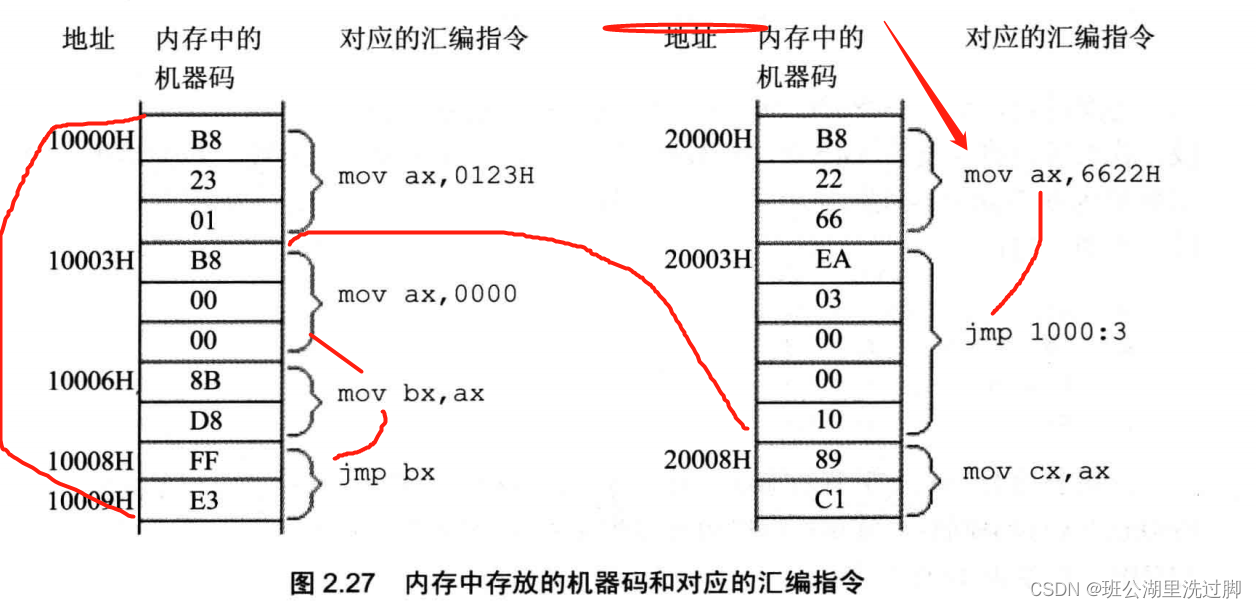

内存中存放的机器码和对应的汇编指令情况如图2.27所示,设CPU初始态:CS=2000H,IP=0000H,请写了指令执行序列,思考后看分析。

分析:

CPU对图2.27中的指令的执行过程如下。

(1)当前CS=2000H, IP=0000H, 则CPU从内存2000H×16 + 0 = 20000H处理读取指令,

读入的指令是:B8 22 66(mov ax, 6622H),读入后IP=IP+3=0003H;

(2)指令执行后,CS=2000H, IP=0003H,则CPU从内存2000H×16+0003H=20003H处理读取指令,读入的指令是:EA 03 00 00 10(jmp 1000:0003),读入后IP=IP+5=0008H;

(3)指令执行后,CS=1000H, IP=0003H, 则CPU从内存1000H×16+0003H=10003H处读取指令,读入的指令是:B8 00 00(mov ax, 000),读入后IP=IP+3=0006H;

(4)指令执行后,CS=1000H,IP=0006H,则CPU从内存1000H×16 + 0006H=10006H处理读取指令,读入的指令是:8B D8(mov bx, ax),读入后IP=IP+2=0008H;

(5)指令执行后,CS=1000H,IP=0008H,则CPU从内存1000H×16 + 0008H=10008H处理读取指令,读入的指令是:FF E3(jmp bx),读入后IP=IP+2=000AH;

(6)指令执行后,CS=1000H,IP=0000H,则CPU从内存10000H处理读取指令......

经分析后,可知指令执行序列为:

(1)mov ax, 6622H

(2)jmp 1000:3

(3)mov ax, 0000

(4)mov bx, ax

(5)jmp bx

(6)mov ax, 0123H

跳转到第3步执行

2.12 代码段

前面讲过,对于8086PC机,在编程时,可以根据需要,将一组内存单元定义为一个段。我们可以将长度为N(N≤64KB)的一组代码,存在一组地址连续、起始地址为16的倍数的内存单元中,我们可以认为,这段内存是用来存放代码的,从而定义了一个代码段。比如,将:

mov ax, 0000 (B8 00 00)

add ax, 0123H (05 23 01)

mov bx, ax (8B D8)

jmp bx (FF E3)

这段长度为10个字节的指令,存放在123B0H~123B9H的一组内存单元中,我们就可以认为,123B0H~123B9H这段内存是用来存放代码的,是一个代码段,它的段地址为123BH,长度为10个字节。

如何使得代码中的指令被执行呢?将一段内存当作代码段,仅仅是我们在编程时的一种安排,CPU并不会由于这种安排,就自动地将我们定义的代码段中的指令当作指令来执行。CPU只认被CS:IP指向的内存单元中的内容为指令。所以,要让CPU执行我们放在代码段中的指令,必须要将CS:IP指向所定义的代码段中的第一条指令的首地址。对于上面的例子,我们将一段代码存放在123B0H~123B9H内存单元中,将其定义为代码段,如果要让这段代码得到执行,可设CS=123BH、IP=0000H。

2.9~2.12 小结

(1)段地址在8086CPU的段寄存器中存放。当8086CPU要访问内存时,由段寄存器提供内存单元的段地址。8086CPU有4个段寄存器,其中CS用来存放指令的段地址。

(2)CS存放指令的段地址,IP存放指令的偏移地址。

8086机中,任意时刻,CPU将CS:IP指向的内容当作指令执行。

(3)8086CPU的工作过程:

⑴ 从CS:IP指向的内存单元读取指令,读取的指令进入指令缓冲器;

⑵ IP指向下一条指令;

⑶ 执行指令。(转到步骤⑴,重复这个过程。)

(4)8086CPU提供转移指令修改CS、IP的内容。

检测点2.3

下面的3条指令执行后,CPU几次修改IP?都是在什么时候?最后IP中的值是多少?

mov ax, bx

sub ax, ax

jmp ax

每次执行一次语句IP都会修改一次,最后一次相当于mov IP, 0000H,最后IP中的值为0000H

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?