UBOOT的PHYCHIP配置

PHYCHIP的配置位于 include/configs/XXX_config.h中

#define CONFIG_YYY_ETH

#define CONFIG_YYY_ETH_SPI_BUS 0

#define CONFIG_YYY_ETH_SPI_CS 0

代码流程

Uboot下PHYCHIP的驱动代码由一些函数构成,这些函数包含在文件PHYCHIP.c中,位于drivers/net/目录下,具体包含的函数以及含义如下:

eth_init()

eth_send() //链路层数据包发送

eth_rx() //链路层数据包接收

eth_halt()

encReceiverReset()

encReceiverResetCallbask()

encPoll()

encRx()

encInit()

encPhyRead()

encPhyWrite()

PHYCHIP编程

要对PHYCHIP进行编程,首先要熟悉PHYCHIP内部寄存器的功能及配置。

PHYCHIP内部寄存器

PHYCHIP有三种类别的静态RAM,控制寄存器(Control Register)、网络缓存(Ethernet Buffer)、PHY寄存器(PHY Register)。

Ethernet Buffer共8K字节,分为独立的发送缓存和接收缓存,发送和接收缓存的位置和大小可以完全由host通过spi接口控制。DMA通道课直接读写Ethernet Buffer。

PHY Register提供PHY模块的控制和配置以及PHY模块的操作状态,PHY Register共有32个寄存器,只有9个是可操作的。不像ETH、MAC、MII控制寄存器或者Buffer缓存,PHY Register不是通过SPI接口直接访问的,而是通过MII寄存器MIREGADR访问。

读取PHY寄存器的步骤:

1、写想读取的PHY寄存器地址到MIREGADR寄存器

2、设置MICMD.MIIRD bit

3、等待10.24uS,轮训poll MISTAT.BUSY bit来确认操作已经完成,若busy不能启动任何MIISCAN操作或写MIWRH寄存器。当MAC获取到了寄存器内容,BUSY bit自动清空

4、清空MICMD.MIIRD bit

5、从MIRDL和MIRDH寄存器读取想要读取的数据。

写PHY寄存器的步骤:

1、写想修改的PHY寄存器地址到MIREGADR寄存器

2、写低8位数据到MIWRL

3、写高8位数据到MIWRH,MISTAT.BUSY bit被置位,需等待10.24uS。

scan PHY寄存器的步骤:

1、写想修改的PHY寄存器地址到MIREGADR寄存器

2、设置MICMD.MIISCAN bit,scan操作开始了,MISTAT.BUSY bit被置位,第一个读取操作在10.24uS之后完成,然后会以相同的间隔执行连续的操作,直到操作被取消,MISTAT.NVALID bit会被轮训poll来决定何时第一个操作完成。

3、设置了MIISCAN之后,MIRDL和MIRDH会每10.24uS自动更新。

MII控制寄存器有:MICON、MICMD、MISTAT。

PHYCHIP的命令格式

PHYCHIP的工作方式完全依赖于host通过spi接口送过来的命令。通过这些命令进入PHYCHIP的控制内存(control memory)和(ethernet buffer空间)。

命令格式如下:

3bit操作码+5bit参数(指定寄存器地址或数据常量)[+数据]

本PHYCHIP共使用7个命令:

RCR(读取PHY的控制寄存器)、RBM(读取PHY的缓存空间)、WCR(写PHY的控制寄存器)、WBM(写PHY的缓存空间)、BFS(Bit域设置)、BFC(Bit域清空)、SC(软件复位)

1、RCR命令

RCR命令允许host以任意顺序读取ETH、MAC和MII寄存器,其中PHY寄存器的读取通过一个特殊的MII寄存器接口。

2、RBM命令

RBM命令允许host从8K字节的接收缓存读取字节。

3、WCR命令

RCR命令允许host以任意顺序修改ETH、MAC和MII寄存器

4、WBM命令

WBM命令允许host向8K字节的发送缓存写入数据。

5、BFS命令

6、BFC命令

7、SC系统命令

以太网概观

Ethernet Packet Format:目的MAC、源MAC、类型/长度域、数据负载、可选的PAD域、CRC。

PHYCHIP初始化步骤

1、初始化接收缓存

2、初始化发送缓存

3、收包滤波器

4、等待复位完成

5、MAC初始化配置(MACON2.MARST清空使MAC脱离复位状态,MACON1.MARXEN置1使能MAC接收frame,配置MACON3.PADCFG/TXCRCEN/FRMLNEN/FULDPX、MACON4使用默认、MAMXFL限制最大fram长度、MABBIPG背to背、MAIPGL非背to背、MAADR0:MAADR5配置本地MAC地址)

6、PHY初始化配置(根据应用必须配置三个PHY寄存器,PHCON1.PDPXMD控制设备的半双工/全双工,PHCON1.PDPXMD与MACON3.FULDPX必须匹配,PHCON2.HDLDIS用来阻止半双工时原子的自环,PHLCON用于配置输出的LEDA和LEDB)

发送和接收数据包

发送数据包:

PHYCHIP的MAC会自动产生帧头,另外若配置了MAC可以产生PAD和CRC。

host必须产生和写入其他的frame域到buffer。

PHYCHIP需要一个单独的每个数据包的控制byte,防止packet之前。

发送packet步骤:

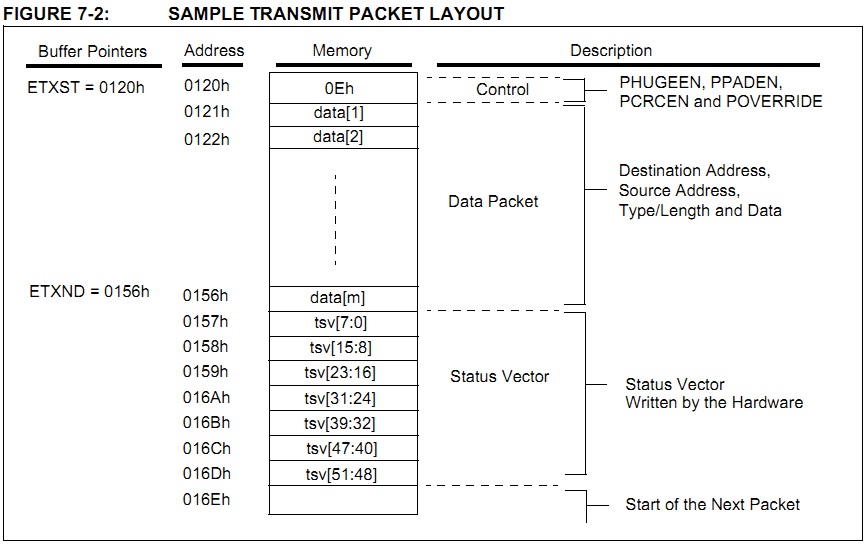

1、适当编程ETXST指针指向内存中一个不用的区域;

2、使用WBM命令写每个packet的控制byte、目的MAC、源MAC、Type/Len、数据负载;

3、适当编程EXTND指针;

4、清除EIR.TXIF、EIE.TXIE,设置EIE.INTIE来使能一个中断;

5、设置ECON1.TXRTS开始传输。

若DMA正在执行,则等待DMA完成之后再开启发送;

发送完成之后,ECON1.TXRTS清空,7个字节的发送状态矢量被填写到相应位置,ETXST、ETXND被修改。

要检查发送是否正常完成,ESTAT.TXABRT能显示。

接收数据包:

使能收包

假定接收缓冲已经初始化、MAC被正确配置、接收滤波器已经配置,要接收网络数据包,host需要:

1、如果接收到数据包时需要产生一个中断,设置EIE.PKTIE和EIE.INTIE;

2、如果在接收缓冲满时丢弃数据包时需要产生一个中断,清除EIR.RXERIF,设置EIE.RXERIE、EIE.INTIE。

3、设置ECON1.RXEN来使能接收。

为了阻止不需要的数据包,建议在修改接收滤波器配置ERXFCON和MAC地址之前,将RXEN清空。

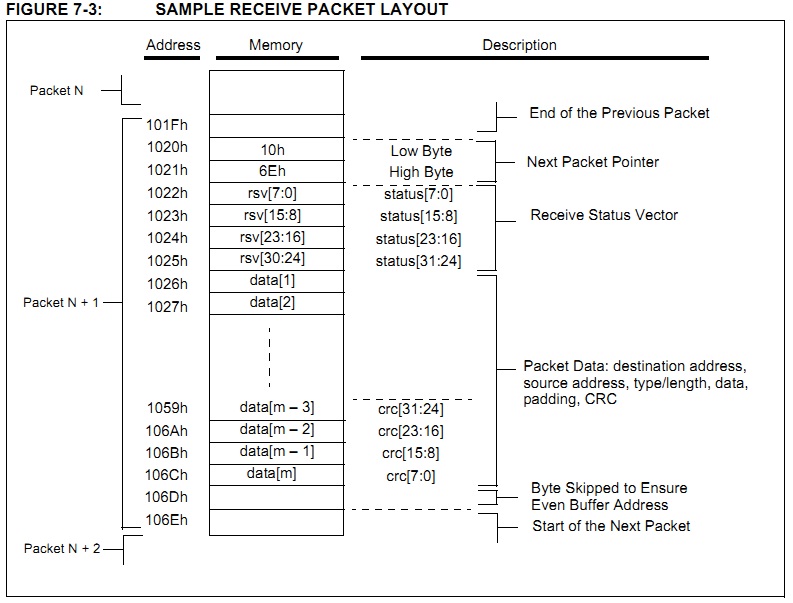

接收使能之后,未被滤掉的数据包会被写入到唤醒接收缓冲区,EPKTCNT会增加,EIR.PKTIF被设置,产生一个中断,硬件写指针ERXWRPT会自动增加。

读取接收的数据包

利用RBM命令

释放接收缓存

当出现异常时,采用Next Packet Pointer

获取接收缓存的剩余空间

下表列出了PHYCHIP内部重要寄存器的功能及偏移地址。

ECON 网络控制寄存器

ESTAT 网络状态寄存器

发送控制寄存器

发送状态寄存器

MAC地址寄存器(共6个)

制造商ID号

产品ID号

内部SRAM数据读指令,内部地址不增加

内部SRAM数据读指令,内部地址增加

发送数据包长度低字节寄存器

发送数据包长度高字节寄存器

2860

2860

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?