|

语言 |

平台 |

简介 |

开源与授权 |

优势 |

劣势 |

可行性 |

|

Python |

Python |

直接使用Python语法编译 |

开源 |

不用安装额外的库,语法简单,自己编写生成HDL代码风格,HDL代码重用性强 |

只适合通用性的模块 / 总线接口规范的模块,比如amba读写寄存器、memory等。版本经常更新。 |

Linux自带Python,上手简单,可能性强,推荐和总线相关的模块使用Python |

|

Myhdl |

比利时ASIC工程师Jan Decaluwe 2009年基于python设计硬件描述库 |

开源 |

可以设计更复杂(复杂的算法实现)的代码,加减乘除,逻辑运算等可以直接转化成HDL |

设计流程复杂,HDL代码可读性性差,需要学习相关库函数,文档少,未见其他公司使用,14年后 |

使用Python PIP安装,安装后按照教程做即可 | |

|

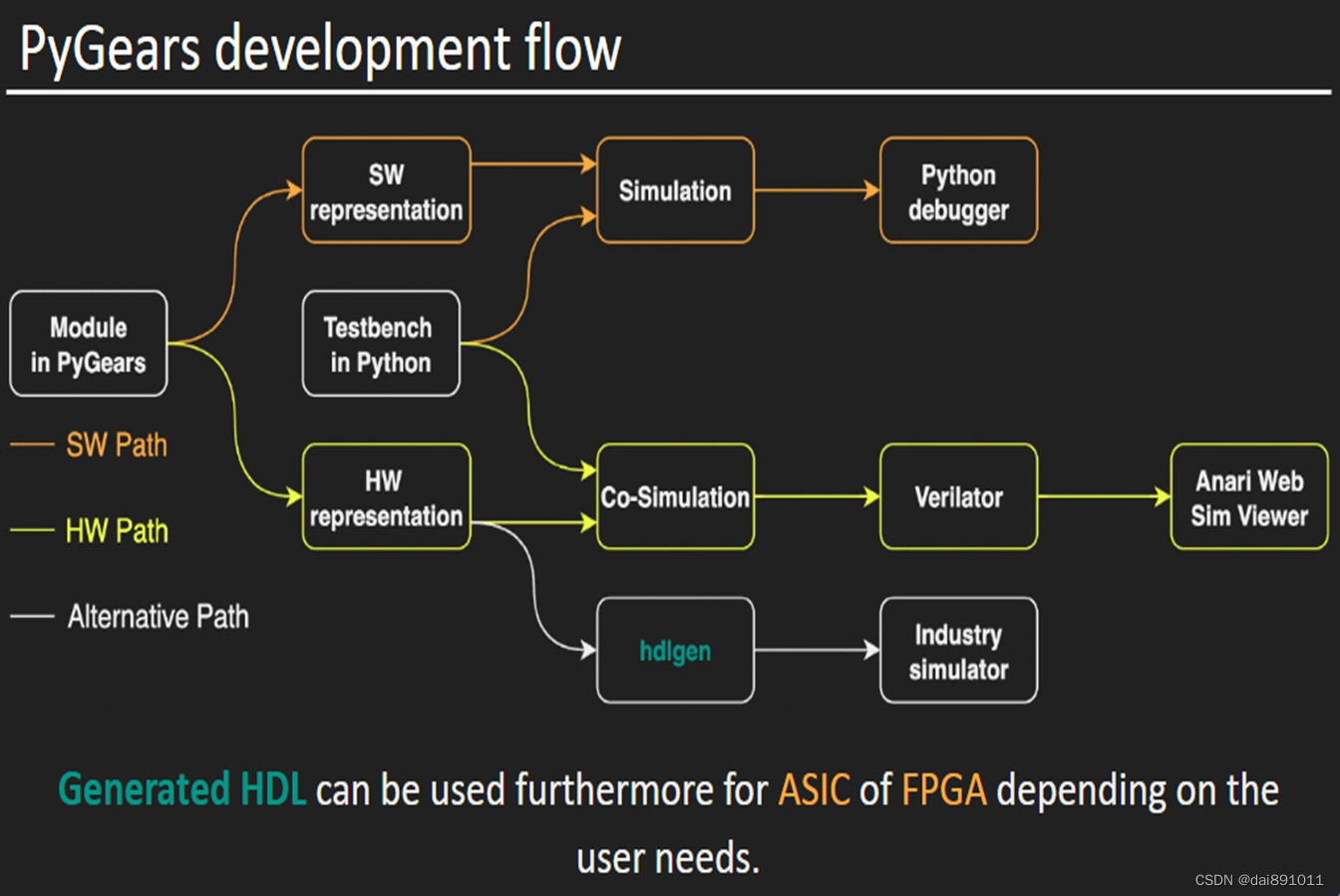

PyGears |

2022年3月加州大学,在Python的基础上封装成更高层次抽象的HDL库 |

开源 |

可以设计更复杂(复杂的算法实现)的代码,设计方法类似MyHDL |

设计流程复杂,HDL代码可读性性差,需要学习相关库函数,文档少,未见其他公司使用 |

使用Python PIP安装,安装后按照教程做即可 | |

|

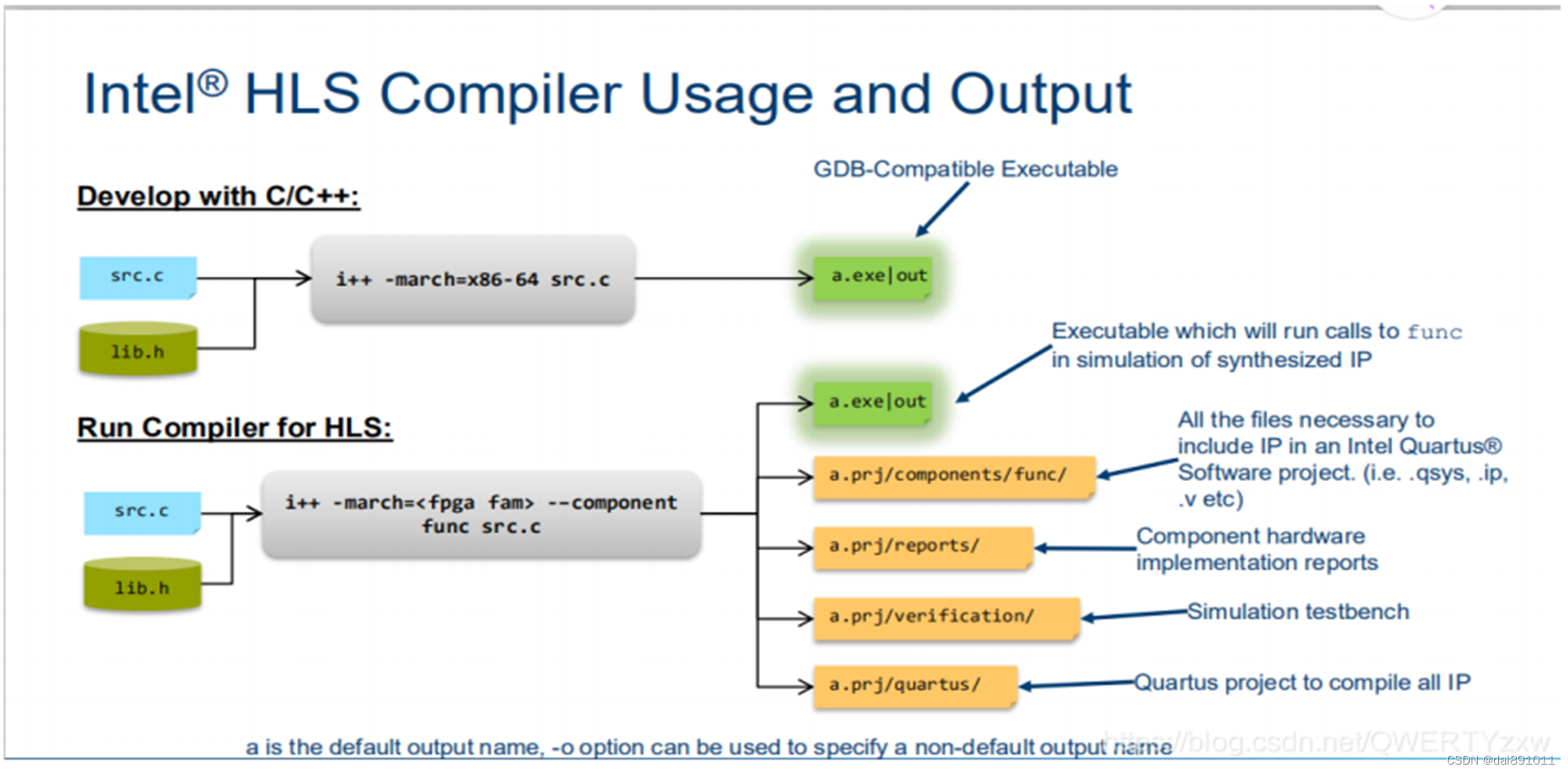

C/C++ |

HLS(C/C++) |

Xilinx Vivado HLS Intel Quartus HLS, 将C/C++转成适合FPGA的HDL代码 |

需要授权 |

HLS 能帮助软件和算法工程师参与、甚至主导芯片或 FPGA 设计 |

HDL代码可读性性差,使用HLS转化的代码比直接用HDL资源多出14%~40%(来自CSDN) 字长分析和优化需要 HLS 的使用者对综合的算法、数据集、C/C++、HDL有深入的了解,这也是限制这种优化方式广泛使用的主要因素 |

需使用安装Vivado和License授权,例程丰富,按照教程使用即可,转化的HDL代码是 FPGA代码风格,需微调成ASIC代码风格 |

|

System C |

Synopsys 公司, CoWare 公司和Frontier Design公司1999年合作开发 |

OPEN SOURCE LICENSE 2.3 |

同时开发软件和硬件,适合复杂算法和Soc 在RTL设计完成之前开始编写软件驱动程序, 在RTL之后替换成DUT交叉验证,适合大型芯片并行开发 |

对开发人员的要求极高,要求能从系统级,事务级、行为级建模,要求精通SystemC硬件库 |

下载安装安装SystemC的工具即可,仿真tb 同样使用SystemC完成 | |

|

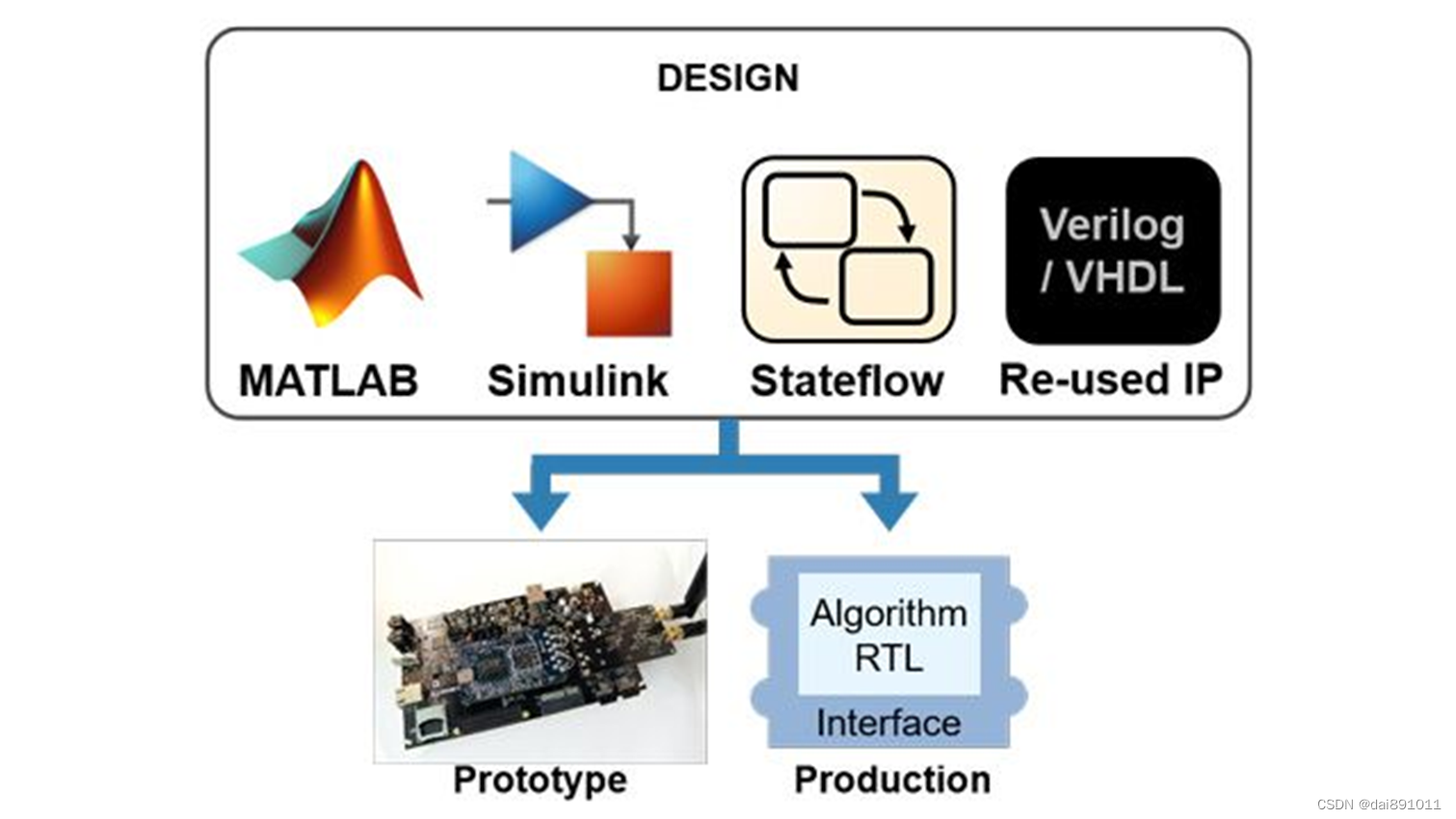

Matlab |

HDL Coder |

HDL Coder 从 MATLAB® 函数、Simulink® 模型和 Stateflow® 图表生成可移植、可合成的 HDL 代码。 |

需要授权 |

System Generater的增强版,可以生成FPGA/ASIC风格代码规范,同时有ISO26262规范HDL代码的部署方案,适合算法仿真研究 |

生成的HDL代码可读性差 |

安装Matlab HDL Coder工具,具备丰富的例程和视频教程 |

|

Scala |

SpinalHDL |

Spinal HDL是来自瑞士的Charles Papon发起的新一代开源硬件描述语言 |

开源 |

设计CPU设,模块化设计,语法清晰易懂 |

在CPU 设计上有优势,不适合算法设计,同时需要掌握 Scala语言 |

需先安装Java虚拟机和Scala的开发环境,需学习 Scala语法 |

|

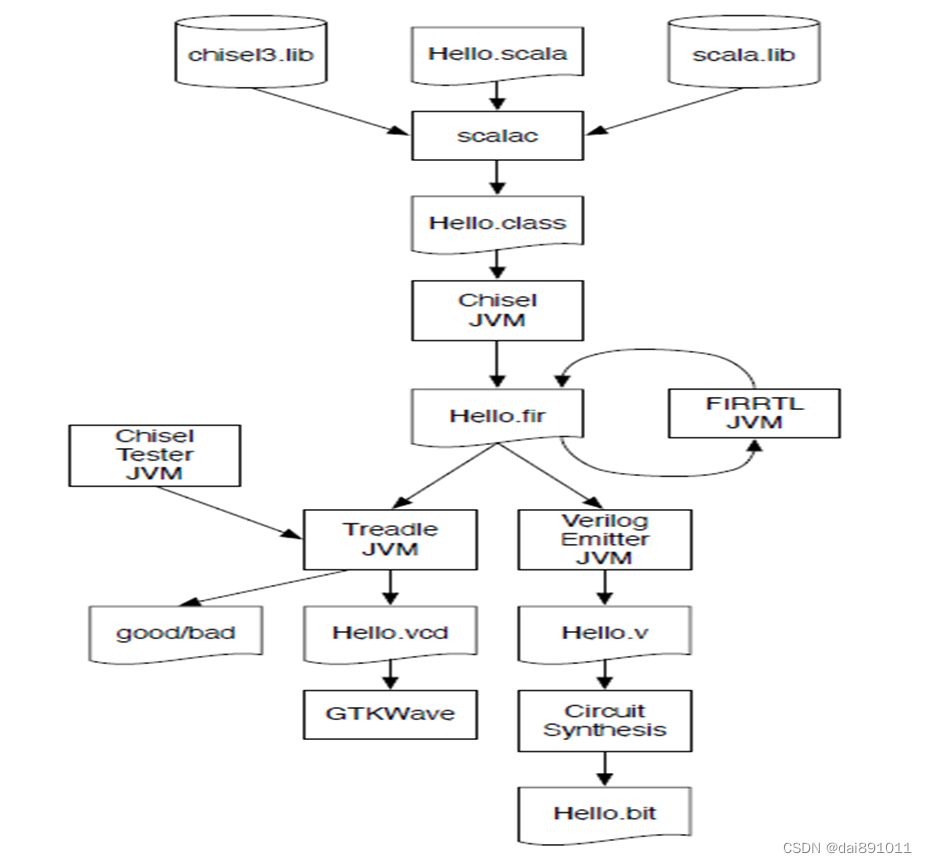

Chisel |

伯克利大学在设计RSIC-V时设计的高级抽象硬件描述语言 |

开源 |

适合设计CPU设计,具备interface描述功能, 可以实例化模块连接,Chisel代码重用性高,自带lint、CDC检查等 |

在CPU 设计上有优势,不适合算法设计,同时需要掌握 Scala语言 |

需先安装Java虚拟机和Scala的开发环境,需学习 Scala语法 | |

|

Other |

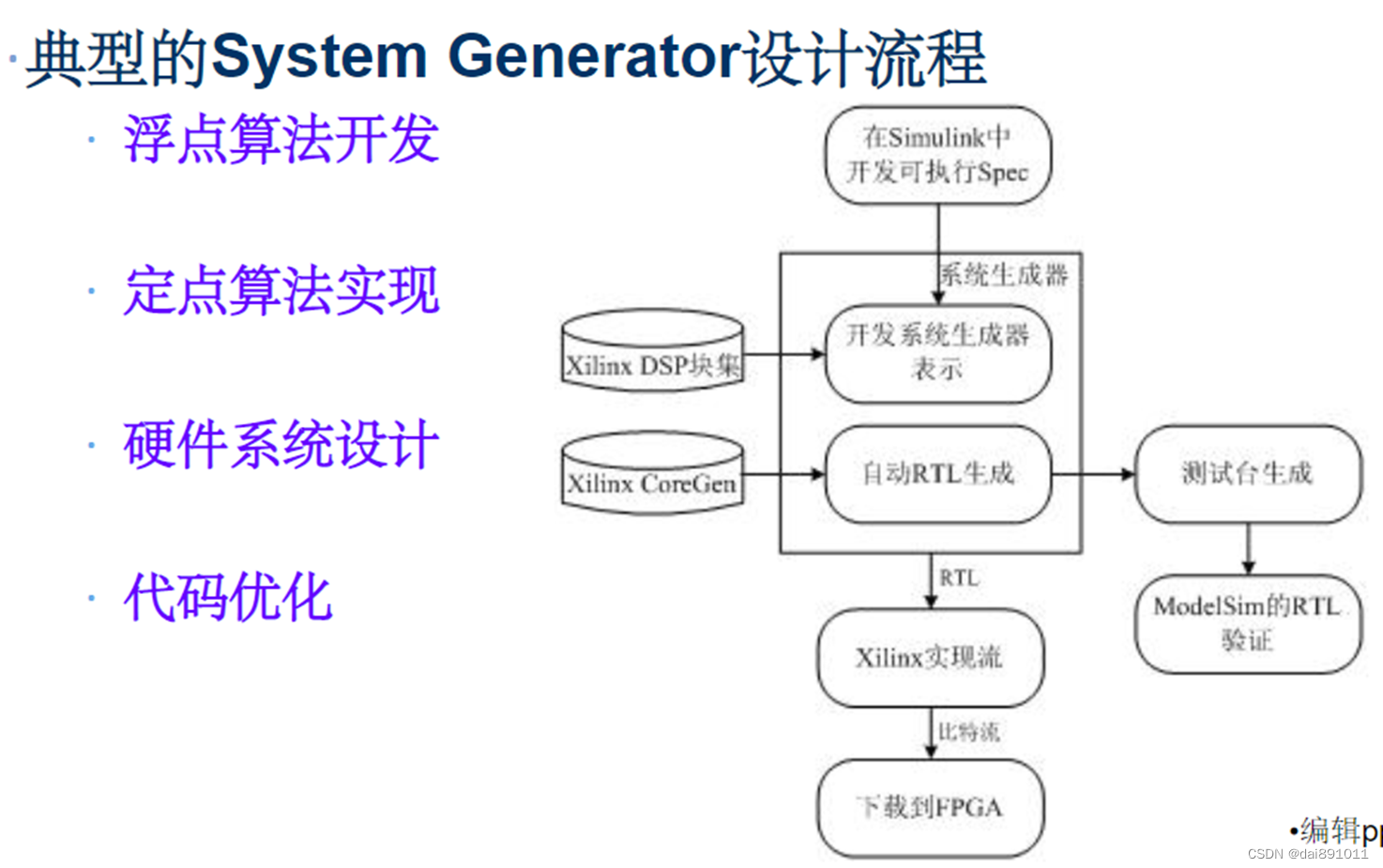

System Generater |

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,嵌入了Xilinx的一些模块,可以在MATLAB中的Simulink中进行定点仿真 |

需要授权 |

具备大量的通信相关的IP,适合通信算法研究和在 FPGA实现 |

Simulink中生成转化HDL代码的IP,配置复杂,且容易出错,在14年ISE时代较流行,后逐渐被Vivado HLS取代,HDL代码不易读 |

需安装matlab和Vivado,上手复杂 |

总结: 1)算法研究 : HDL Coder依靠Matlab强大的算法库整体优于HLS;

2)FPGA AI相关算法:Xilinx提供HLS大量库函数,适合AI算法;

3)验证模型: SystemC适合大型Soc芯片并行开发模型、软件驱动;

4)CPU设计: Chisel是SpinalHDL增强版,二者都可以设计module和实例化模块连接,大量基于RSIC-V处理器的基础组件, Chisel更适合CPU设计;

5)IP开发 : PyGears/ Myhdl基于Python易于上手开发小规模IP, Chisel/ SpinalHDL 更适合大规模总线互联IP开发和集成

本文对比了多种硬件描述语言(HDL)的特点,包括Python、MyHdl、PyGears、C/C++ HLS、SystemC、Matlab HDL Coder、SpinalHDL及Chisel等。针对不同应用场景如算法研究、FPGA AI算法、验证模型、CPU设计和IP开发进行了总结。

本文对比了多种硬件描述语言(HDL)的特点,包括Python、MyHdl、PyGears、C/C++ HLS、SystemC、Matlab HDL Coder、SpinalHDL及Chisel等。针对不同应用场景如算法研究、FPGA AI算法、验证模型、CPU设计和IP开发进行了总结。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?