基于S3C2440的系统时钟配置

1、系统时钟概念

S3C2440分为三种不同时钟:

(1)FCLK:开发板最快的时钟频率CPU的频率

(2)HCLK:一般是开发板内存的运行频率:SDRAM,FLASH

(3)PCLK:串口和定时器的一般外设的运行频率(详见官方的英文手册)

2、如何设置S3C2440的系统时钟?

外部的系统时钟的晶振仅仅只有12M,是的没有错就是跟51单片机的晶振差不多快。

有些人会有问题,为什么2440能运行这么快(理论上最快400MHZ)?

数字电子技术基础里面有一种东西叫做分频器。可以把频率变化。

2440芯片里面也有一种类似的东西叫做PLL锁相环

完成目标:12M---》400Mhz或者200Mhz

3、配置寄存器

公式:

MPLL Control Register

Mpll = (2 * m * Fin) / (p * 2 S )

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

200Mhz:

16进制:5C 十进制:92

带入公式: MPLL = ((92+8)*2 *12Mhz)/ ((1+2) * 2 ^(2)) = 200Mhz

400Mhz:

16进制:7f 十进制:127

带入公式: MPLL = ((127+8)*2 *12Mhz)/ ((2+2) * 2 ^(1)) = 405Mhz~~400Hhz

#define S3C2440_MPLL_200MHZ ((0x5c<<12)|(0x01<<4)|(0x02))

#define S3C2440_MPLL_400MHZ ((0x7f<<12)|(0x02<<4)|(0x01))

/* 2 设置时钟 */

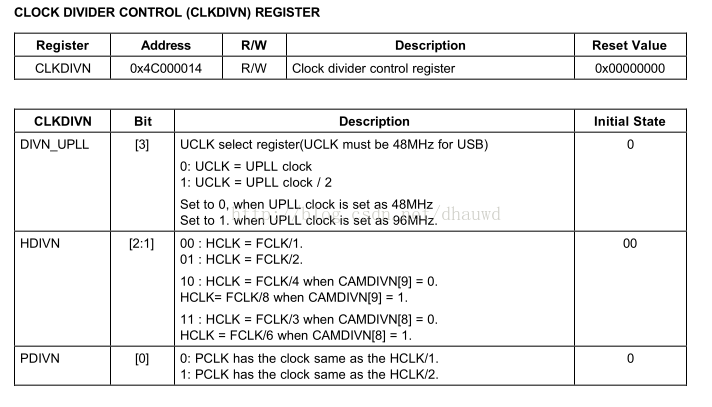

ldr r0,=0x4c000014 //这个仅仅只是设置分频的系数,就是把其设置为芯片

mov r1,#0x03 //FCLK:HCLK:PCLK=1:2:4

str r1,[r0]

/* 如果HDIVN非0,CPU的总线模式应该从“fast bus mode”变为“asynchronous bus mode” */

mrc p15, 0, r1, c1, c0, 0 /* 读出控制寄存器 */

orr r1, r1, #0xc0000000 /* 设置为“asynchronous bus mode” */

mcr p15, 0, r1, c1, c0, 0 /* 写入控制寄存器 */

//S3C2440_MPLL_200MHz

ldr r0, =0x4c000004

ldr r1, =S3C2440_MPLL_200MHZ //根据芯片手册来设置其的时钟频率

str r1,[r0]为什么要向这个地址

0x4c000014 写0x03

首先这个寄存器的作用就是合理的分频FCLK,PCLK,HCLK的频率的大小。

这个寄存器的地址是0x4C000014,所以向这个寄存器写入3的时候

PDIVN:置1;也就是2PCLK = HCLK

HDIVN:[0]置1:(要注意到相当于整个寄存器的第1位置1):2HCLK = FCLK

综上所述:

4PCLK = 2HCLK = FCLK

FCLK= 200MHZ时,

HCLK=100MHZ

PCLK= 50MHZ

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?