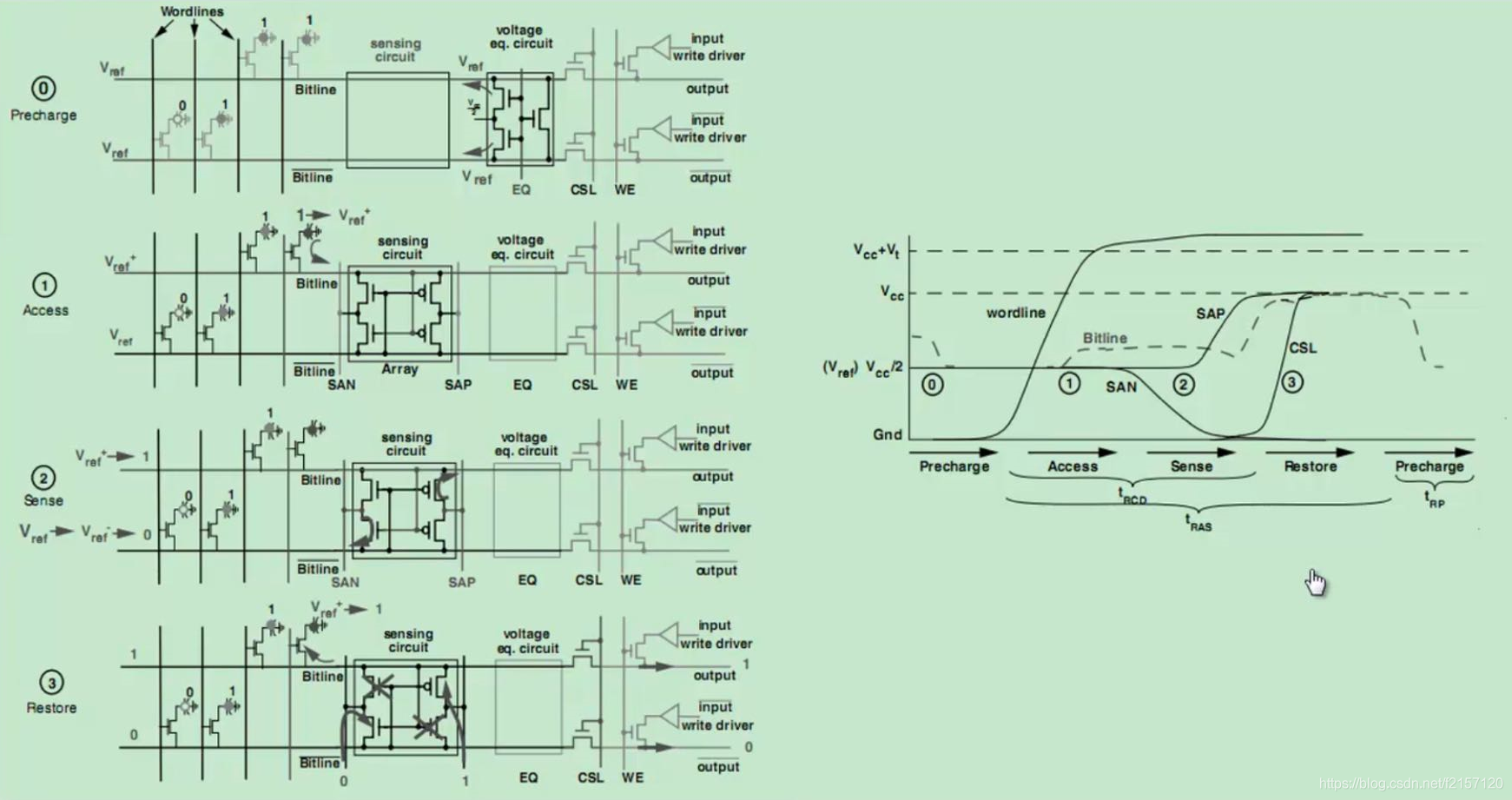

此处,从时序的角度再次分析这个电路,这里主要是这些t参数

第一步:Precharge,先要把bitline,bitline反,SAN,SAP全都置成1/2Vcc,此时sense电路不公正,电压均衡电路工作

第二步:Access,Prechage完成之后,wordline开始打开,这一列选通,列选通以后,进入Bank Access的阶段,Bank开始数据输出,输出到Vref。此阶段,电压均衡电路不工作。该阶段/access,位里面的少量的电容被加到bitline,bitline电压开始升高,变成Vref+,这样会导致Sensing电路不平衡,从而导致SAN有1/2Vcc向负的方向偏移,SAP向正的方向偏移。

第三步:sense,由于Vref+升高了一点点,导致sense电路的两个场效应管不平衡,SAN有1/2Vcc向负的方向偏移,SAP向正的方向偏移,正式进入sense阶段。

与前一阶段access过程合起来,称为tRCD。

在SAN下降,SAP升高的同时,bitline这根线也在升高,到第三步结束的时候,bitline的Vref+的电位维持在很高的水平,1,Vref-维持在0,很低的水平,然后CSL列这根信号线被选通

第四步,CSL升高

本文详细解析DDR2内存的工作流程,包括Precharge、Access、Sense步骤,涉及tRCD、tRAS、tRP等关键时序参数。讨论了读取过程中bitline的电压变化与Sense电路的作用。同时对比了DDR1和普通SDRAM,阐述了DDR2如何通过增加突发长度和时钟利用率提高数据传输速率,而内部电路变化不大。

本文详细解析DDR2内存的工作流程,包括Precharge、Access、Sense步骤,涉及tRCD、tRAS、tRP等关键时序参数。讨论了读取过程中bitline的电压变化与Sense电路的作用。同时对比了DDR1和普通SDRAM,阐述了DDR2如何通过增加突发长度和时钟利用率提高数据传输速率,而内部电路变化不大。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?