AMD K8 之前的系统总线介绍,请参考:《

PC架构系列:CPU/RAM/IO总线的发展历史!

》

对于AMD发布的K8处理器,有一个最大的改变,就是CPU的核心中集成了内存控制器 ( Memory-Controller )。这就意味着

CPU可以直接访问内存(RAM),而不用像之前那样需要通过系统总线连接到北桥芯片了,或者说北桥芯片中已经可以不再需

要内存控制器的功能了。那么,随着“经典”的系统总线 结构 的逝去,FSB的概念也不复存在了,对于其它工作部件的时钟频率

的发生也随之有了新的方法,这就是AMD K8中的“分频”或是“除频” ( the Clock Divider )机制!

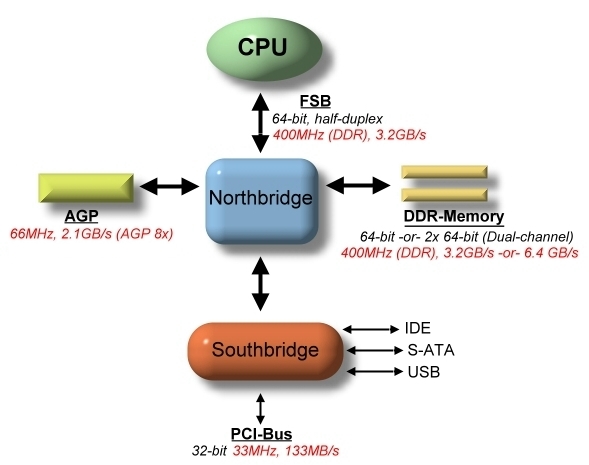

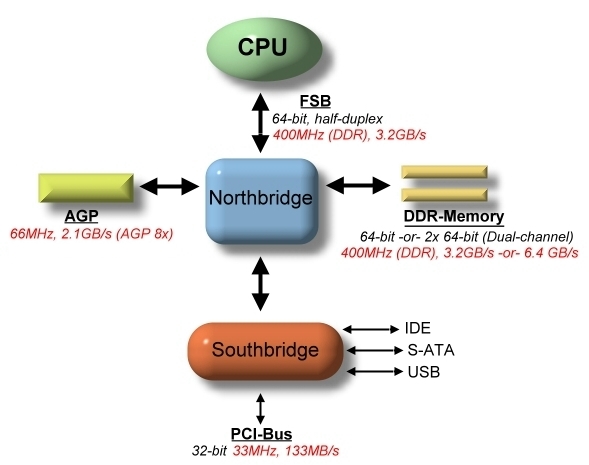

在开始详细说明K8的分频机制之前,我们来回顾一下K8之前的系统结构,拿K7来说,系统结构从整体来说与Intel系列的结构

没有什么区别,都是FSB的模式:

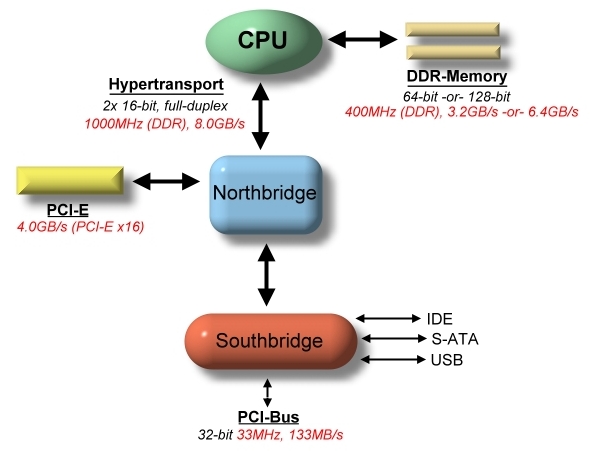

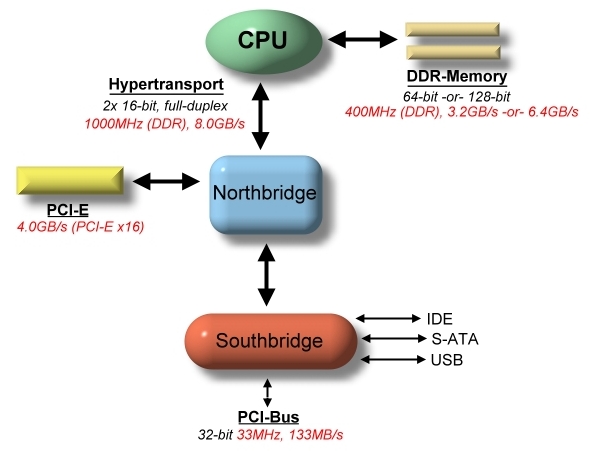

而我们纵观K8的系统结构图,可以看到最大的不同是CPU与RAM直接连接,另外又多出来了一个新鲜的面孔,

就是HyperTransport总线规格,替换了传统意义上的FSB技术!

面对此时北桥芯片可有可无的尴尬局面,很多主板厂商推出了单芯主板,传统概念中的南北桥结构的概念已经模糊,单芯片中

整合了除内存控制器功能以外的所有功能,甚至整合了显卡功能!

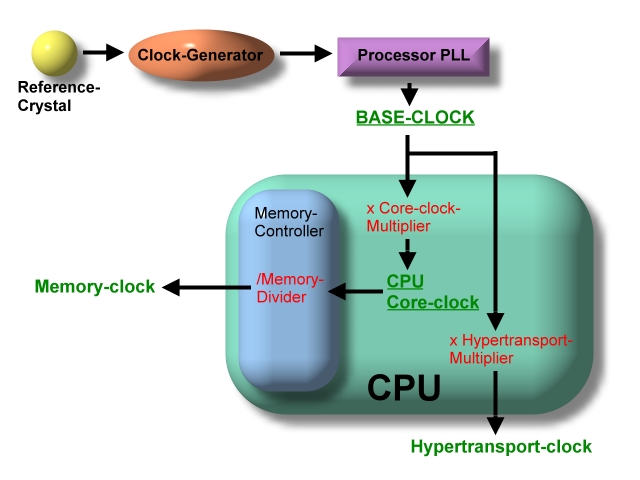

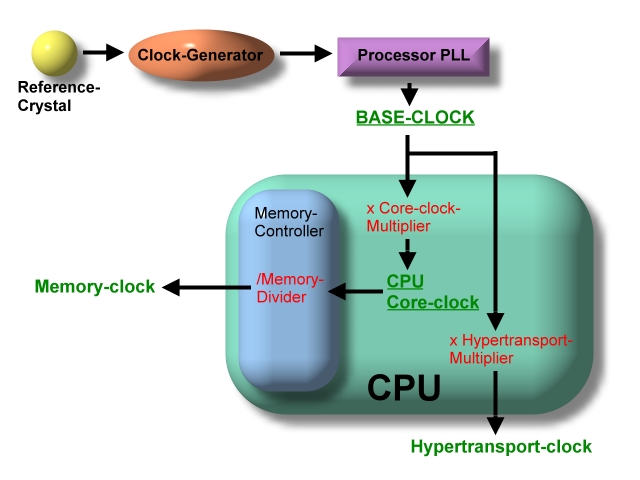

问题来了,既然FSB的概念没有了,那么原本以FSB工作频率(注意不是等效频率)作为参考的CPU的外频由谁来提供呢?

请先参考下图:

首先解释一下什么是PLL ( Phase Locked Loop ),简单说来,就是把晶振的原始输入信号倍频为某一工作频率的输

出信号,我们假设上图中,经过PLL后产生的BASE-CLOCK为200MHz。

接下来有问题出来了:原来K8的架构中,内存频率和HyperTransport的时钟频率都是基于CPU的频率来的!

我们终于看到了期待已久的Memory Divider,内存如何与CPU搭配呢,我们有下面的公式:

CPU频率/ Memory Divider = DDR/DDR2 内存总线频率 = DDR/DDR2 内存工作频率 * 2

* 注:如果Memory Divider不是整数,比如说是4.6,需要将Memory Divider设定为5,以免出现内存超频工作的情况。

拿AMD AM2 Athlon 64 3200+来说,它的CPU频率是200MHz*10=2000MHz

如果我们使用的是DDR2 667的内存

--> 其数据传输率为667MHz,内存总线频率为333MHz,内存工作频率为166MHz

--> 所以需要设定Memory Divider为6,即:2000MHz/6 = 333MHz = 166MHz * 2。

如果是使用DDR2 800内存

--> 其数据传输率为800MHz,内存总线频率为400MHz,内存工作频率为200MHz

--> 则Memory Divider为5,即 2000MHz/5 = 400MHz = 200MHz * 2

但如果是AMD AM2 Athlon 64 3500+,它的CPU频率是200MHz*11=2200MHz

如果我们使用DDR2 667的内存,

--> Memory Divider则是:2200MHz/333 = 6.6 ,需要设定为7。

所以实际上DDR2 667的内存总线频率为2200MHz/7,其实际的传输速率为:(2200MHz/7)*2 = 629MHz < 667MHz,

内存实际上未完全发挥最大的功能,但是这也没有办法!

最后总结一下,选AMD的CPU最好还是看CPU主频来选DDR2内存,最好是:

1. Memory Divider越小越好

2. 内存的实际工作频率越接近其额定值越好!

对于AMD发布的K8处理器,有一个最大的改变,就是CPU的核心中集成了内存控制器 ( Memory-Controller )。这就意味着

CPU可以直接访问内存(RAM),而不用像之前那样需要通过系统总线连接到北桥芯片了,或者说北桥芯片中已经可以不再需

要内存控制器的功能了。那么,随着“经典”的系统总线 结构 的逝去,FSB的概念也不复存在了,对于其它工作部件的时钟频率

的发生也随之有了新的方法,这就是AMD K8中的“分频”或是“除频” ( the Clock Divider )机制!

在开始详细说明K8的分频机制之前,我们来回顾一下K8之前的系统结构,拿K7来说,系统结构从整体来说与Intel系列的结构

没有什么区别,都是FSB的模式:

而我们纵观K8的系统结构图,可以看到最大的不同是CPU与RAM直接连接,另外又多出来了一个新鲜的面孔,

就是HyperTransport总线规格,替换了传统意义上的FSB技术!

面对此时北桥芯片可有可无的尴尬局面,很多主板厂商推出了单芯主板,传统概念中的南北桥结构的概念已经模糊,单芯片中

整合了除内存控制器功能以外的所有功能,甚至整合了显卡功能!

问题来了,既然FSB的概念没有了,那么原本以FSB工作频率(注意不是等效频率)作为参考的CPU的外频由谁来提供呢?

请先参考下图:

首先解释一下什么是PLL ( Phase Locked Loop ),简单说来,就是把晶振的原始输入信号倍频为某一工作频率的输

出信号,我们假设上图中,经过PLL后产生的BASE-CLOCK为200MHz。

接下来有问题出来了:原来K8的架构中,内存频率和HyperTransport的时钟频率都是基于CPU的频率来的!

我们终于看到了期待已久的Memory Divider,内存如何与CPU搭配呢,我们有下面的公式:

CPU频率/ Memory Divider = DDR/DDR2 内存总线频率 = DDR/DDR2 内存工作频率 * 2

* 注:如果Memory Divider不是整数,比如说是4.6,需要将Memory Divider设定为5,以免出现内存超频工作的情况。

拿AMD AM2 Athlon 64 3200+来说,它的CPU频率是200MHz*10=2000MHz

如果我们使用的是DDR2 667的内存

--> 其数据传输率为667MHz,内存总线频率为333MHz,内存工作频率为166MHz

--> 所以需要设定Memory Divider为6,即:2000MHz/6 = 333MHz = 166MHz * 2。

如果是使用DDR2 800内存

--> 其数据传输率为800MHz,内存总线频率为400MHz,内存工作频率为200MHz

--> 则Memory Divider为5,即 2000MHz/5 = 400MHz = 200MHz * 2

但如果是AMD AM2 Athlon 64 3500+,它的CPU频率是200MHz*11=2200MHz

如果我们使用DDR2 667的内存,

--> Memory Divider则是:2200MHz/333 = 6.6 ,需要设定为7。

所以实际上DDR2 667的内存总线频率为2200MHz/7,其实际的传输速率为:(2200MHz/7)*2 = 629MHz < 667MHz,

内存实际上未完全发挥最大的功能,但是这也没有办法!

最后总结一下,选AMD的CPU最好还是看CPU主频来选DDR2内存,最好是:

1. Memory Divider越小越好

2. 内存的实际工作频率越接近其额定值越好!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?