总结了一些嵌入式学习遇到的知识点,记录在这里,用于以后的查询。

嵌入式系统

以应用为中心、以计算机技术为基础、软硬件可裁剪、适应应用系统对功能、可靠性、体积、成本、功耗严格要求的专用计算机系统。

系统发展的最高形式-片上系统(SOC)

嵌入式处理器

处理器一共分为四类

| 嵌入式处理器 | 说明 |

|---|---|

| 微处理器MCU | 典型代表8位单片机如51单片机 |

| 数字信号处理DSP | 专门用于信号处理的处理器 |

| 片上系统SOC | System on Chip,是一种基于IP(Intellectual Property)核嵌入式系统设计技术。将原先的外围设备集合到处理器片内,如USB端口,蓝牙,TCP/IP通信单元等等。SOC是IC设计的发展趋势。 |

| 可编程片上系统SOPC | 典型的是FPGA |

ARM

ARM版本

- V4架构 : ARM7,ARM9

- V5架构 : 增加了数字信号处理等。ARM10

- V6架构 : 35%代码压缩,DSP加强,Java性能优化提高了8倍,音频视频提升了4倍性能—代表:ARM11

- V7架构 : Cotex-M,R,A—提升了DSP和媒体处理能力提高了近4倍。

命名规范

ARM9TDMI

9表示其是哪个系列的

T:thumb

D:片上调试

M:64位惩罚。

I:支持Embeded-ICE观察硬件

ARM的工作模式

工作模式一共分为7中:usr,sys,fiq,irq,svc,(und)undefined,abort(abt)

详细讲解链接:http://blog.csdn.net/michaelcao1980/article/details/18304683

这里简单介绍几个模式,usr是正常程序运行的模式,svc(管理模式)仅供操作系统运行的模式,sys(系统模式)运行具有特权级的操作系统任务。

ARM状态下的寄存器

37个寄存器用户可见,31个32bit寄存器,6个状态寄存器。

R13在各个模式下都是独立的寄存器。在FIQ模式下多了好些寄存器,所以加快了中断的执行。

R0~R7未分组寄存器,R8~R14分组寄存器,R0~R14通用寄存器。

CPSR

NZCV

I:IRQ

F:FIQ

T:1-thumb 0-ARM state

Mode bits[3:0]:指明在哪个模式

大小端字节序

老版本:只支持小端字节序

注意:Linux网络编程采用大端字节序。

ARM异常

ARM异常在我另一篇文章中有详细的讲解

《异常和中断处理 ARM系统开发者指南 Chapter9-1》链接:http://blog.csdn.net/feather_wch/article/details/50491297

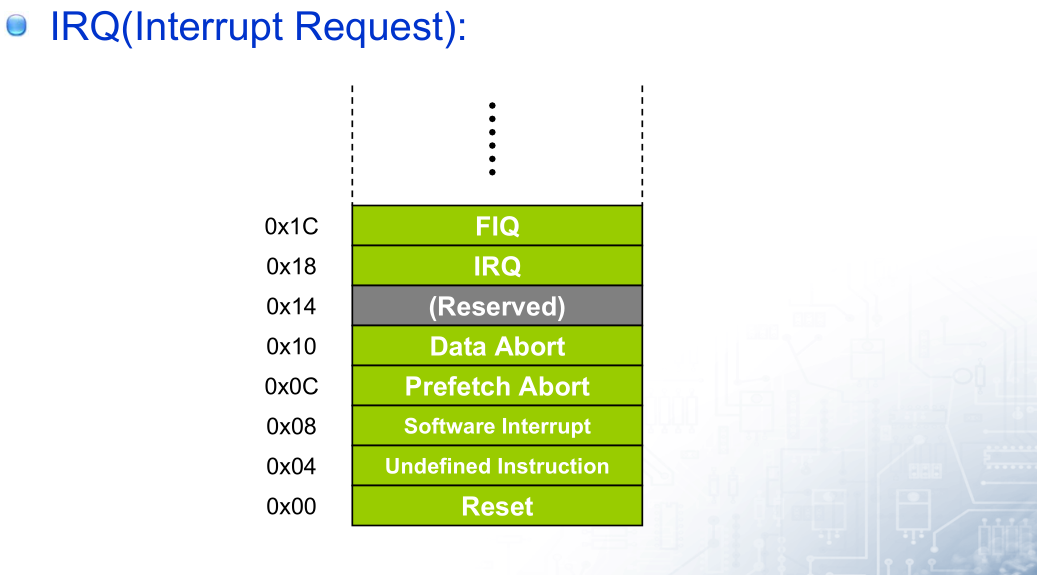

中断向量表

中断执行过程

上面的博客系列文章有详细讲解

ARM指令系统

请参考《ARM 知识汇总与链接 》链接:http://blog.csdn.net/feather_wch/article/details/50429800

其中第二、三节链接分解讲解ARM和Thumb指令集。

ARM可以加上条件进行执行,可以实现高效的逻辑操作。而Thumb指令只有B能进行跳转。

指令条件码表:

ARM具有7中基本寻址方式

ARM汇编代码简略讲解

AREA asm00, CODE, READONLY ;AREA伪指令,表明这为一个段,后面紧跟着段名“asm00”。CODE表明为代码段。READONLY表明只读

ENTRY

start

MOV r0, #10

MOV r1, #3

ADD r0, r0, r1

NOP

END ;文件的结束

322

322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?