vivado版本:Vivado 2019.2

SOC:

本例程实现从串口持续打印"hello_world",只进行PS端的开发,不涉及PL端。

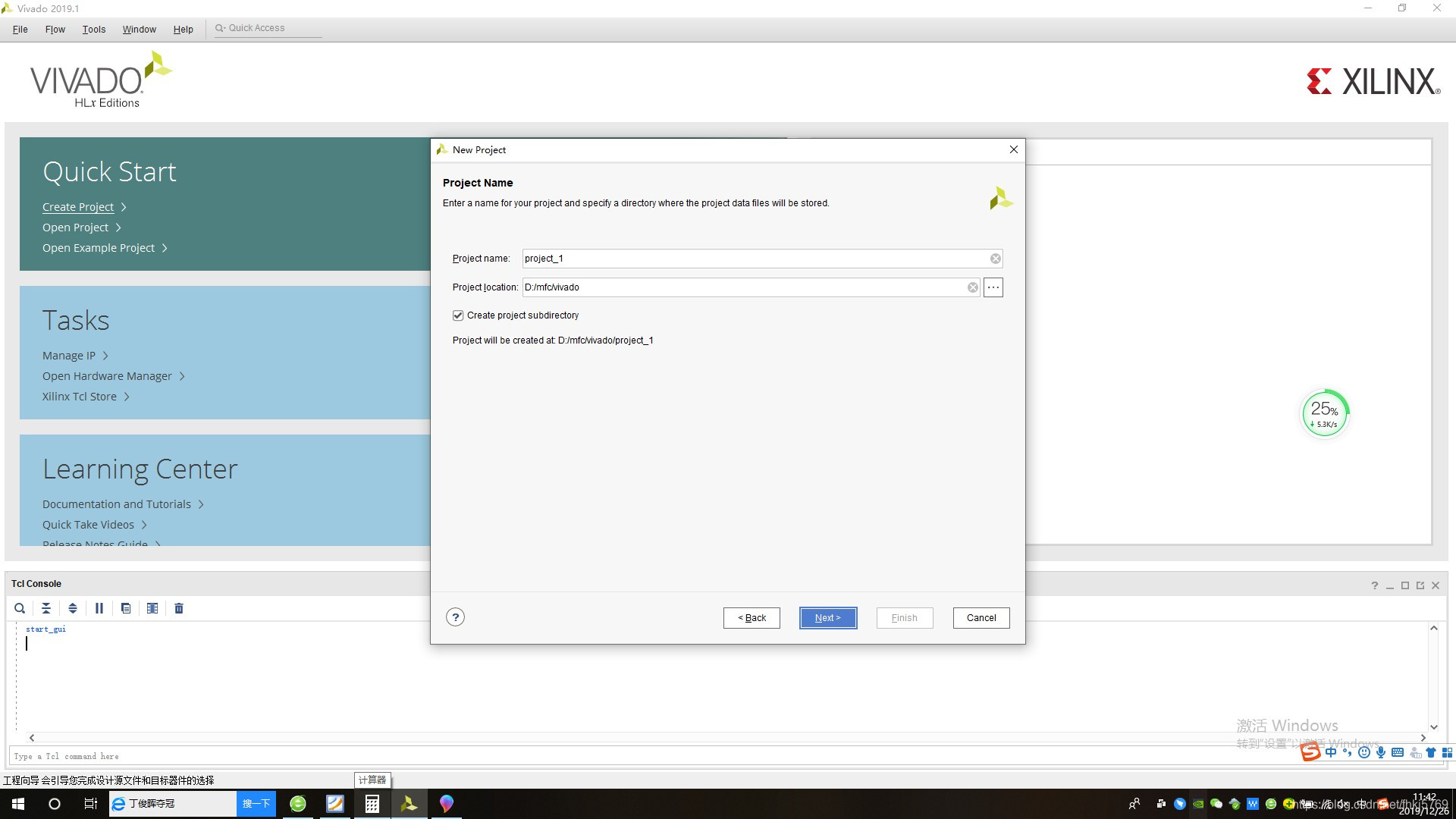

一、新建Vivado工程

打开Vivado软件->Create Project,一路点击Next,遇到项目名称,将项目名称由project_ 1改为hello_world,保存到合适的位置:

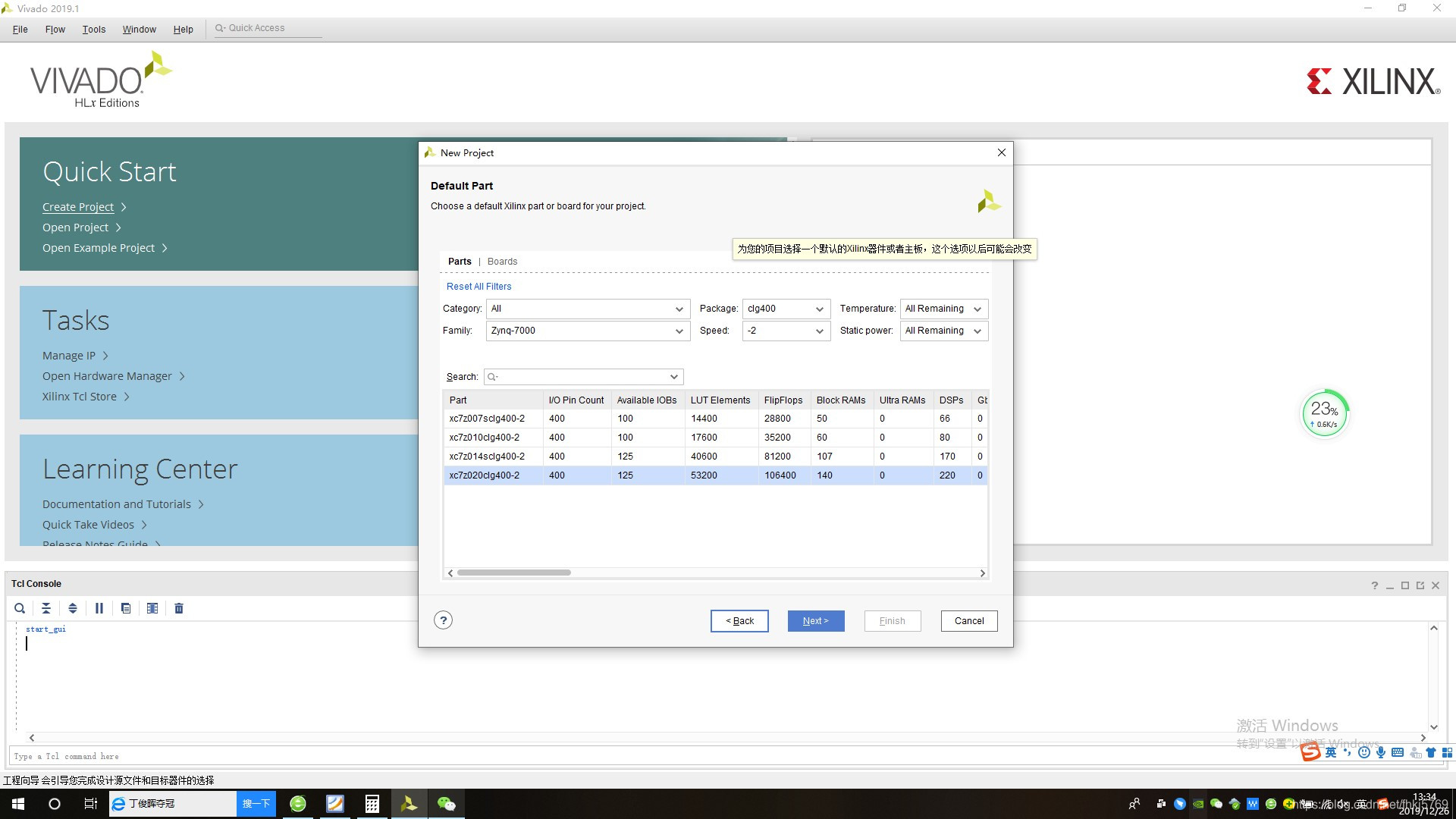

再一路Next,进入器件选型界面,如下图,选择xc7z020clg400-2,然后一路Next,最后Finsh.

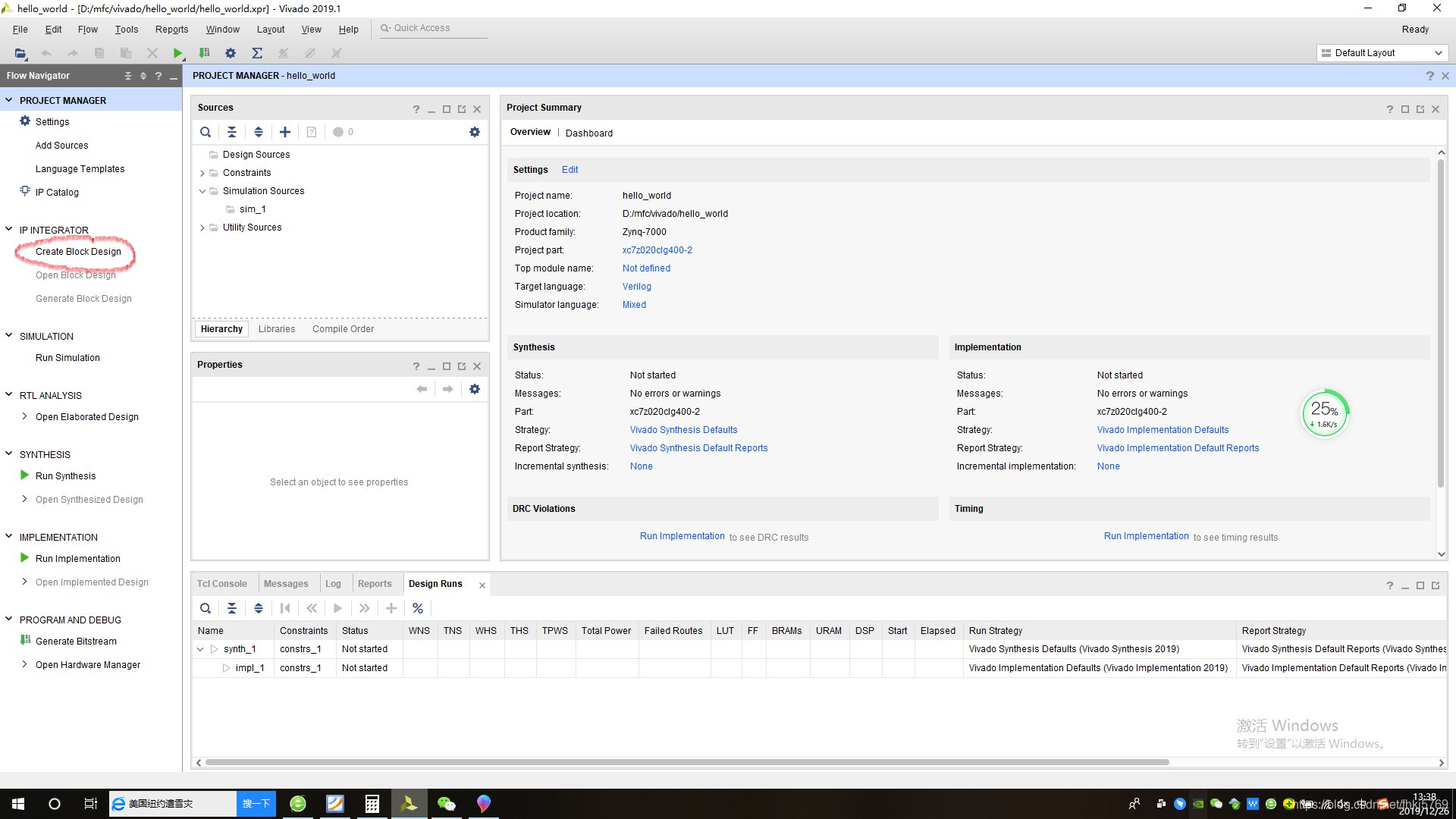

二、新建块设计

点击下图红色圈中的Create Block Design:

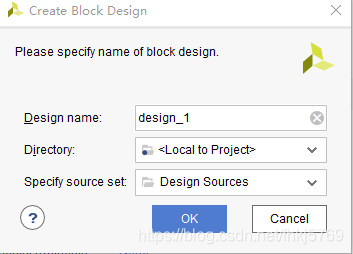

将设计名由design_1,更改为system,点击OK。

三、添加PS端的IP核

点击下图红色圈总的+号,即可列出所有的IP,

本教程详细介绍了如何使用Vivado 2019.2进行ZYNQ 7000 SOC的裸机开发,主要涉及PS端的配置和开发。步骤包括新建Vivado工程、添加ZYNQ Processing System IP核、配置PS-PL接口、生成综合文件、创建SDK工程、建立FSBL和hello_world应用工程,最终实现通过串口每5秒打印一次'Hello World'的功能。

本教程详细介绍了如何使用Vivado 2019.2进行ZYNQ 7000 SOC的裸机开发,主要涉及PS端的配置和开发。步骤包括新建Vivado工程、添加ZYNQ Processing System IP核、配置PS-PL接口、生成综合文件、创建SDK工程、建立FSBL和hello_world应用工程,最终实现通过串口每5秒打印一次'Hello World'的功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1131

1131

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?