中断为异步exception。在介绍中断处理之前,介绍exception通用处理过程。

1 exception分类

ARM架构异常分为同步异常和异步异常。

同步异常是指尝试执行指令时生成的异常,且返回的地址提供造成异常的详细信息。异步异常是指并不是由执行指令产生,且返回的地址不能提供造成异常的详细信息。

通常异步异常源有IRQ,FIQ和SError。

同步异常源有:

- 来自MMU的指令abort。比如,通过读取标记为Execute Never的内存位置的指令

- 来自MMU的数据abort。比如,权限失败或对齐检查

- SP和PC对齐检查

- Synchronous外部abort。比如,当读取转换表时产生abort

- 未分配指令

- 调试异常

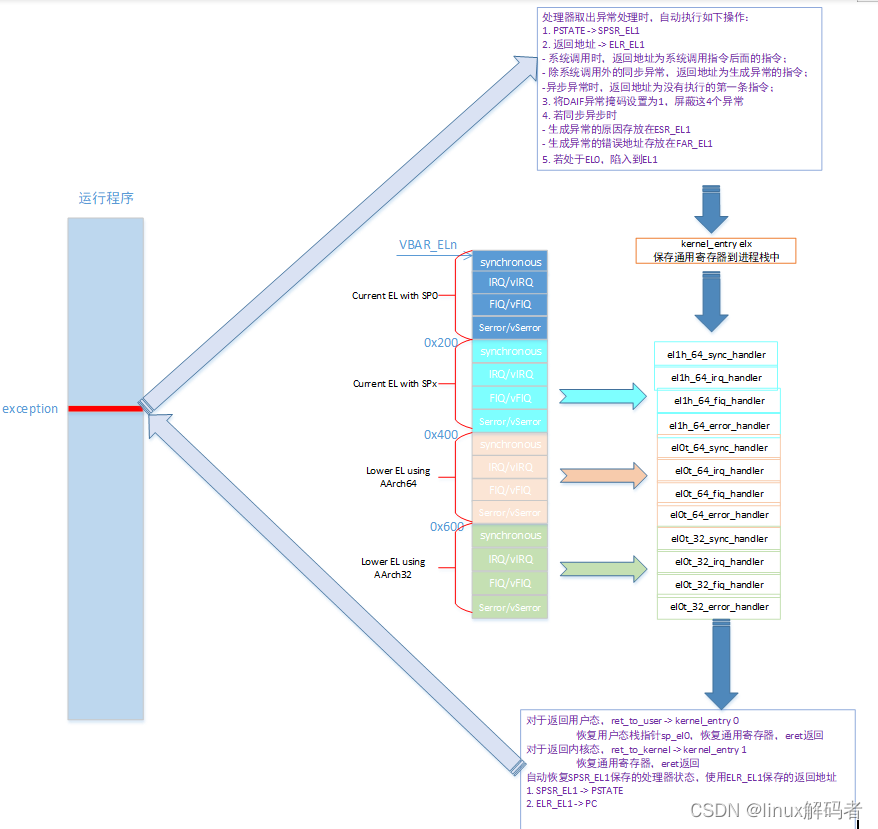

2 exception处理

当一个异常产生时:

(1)处理器自动执行一些操作如下:

- 保存当前处理器状态PSTATE到SPSR_EL1中

- 将返回地址PC保存到ELR_EL1中

其中若是系统调用时,返回地址为系统调用指令后面的指令

若是除了系统调用外的其他同步异常,返回地址为生成异常的指令

若为异步异常,返回地址为没有执行的下一条指令

- 将DAIF异常屏蔽

- 若是同步异常,生成异常的原因存放在ESR_EL1,生成异常的地址存放在FAR_EL1

- 若当前处于EL0,陷入到EL1

(2)kernel_entry elx保存通用寄存器到进程栈下

(3)跳转至异常向量表中对应的entry,执行每个向量entry对应的handler

(4)执行完向量entry对应的handler,若要返回用户态,调用ret_to_user;若要返回内核态,调用ret_to_kernel

- 对于ret_to_user,恢复用户态栈指针sp_el0,恢复通用寄存器,eret返回

- 对于ret_to_kernel,恢复通用寄存器,eret返回

(5)当执行完ERET,处理器自动将保存的处理器状态SPSR_EL1返回到PSTATE,将ELR_EL1保存到PC中

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?