长久以来,我发现我对 buffer 和 cache 以及 buffers 和 cached之间的关系 搞混了;有时 自己都不知道 自己说的是谁了! 某天突然意识到了自己的错误,特来分享一下。

Cache 代表的是高速缓冲存储器,其主要作用是为了协调CPU与主存之间速度不匹配的矛盾,提高cpu与主存之间数据交换的速度;虽说Cache的速度比cpu快,但造价极高,同时又由于在cpu内不能集成太多电路,所以一般Cache比较小;往后intel公司为了进一步提高速度,在一级缓存的基础上,增加了二级缓存和三级缓存;Cache是根据程序的局部性原理(空间局部性和时间局部性)设计的;Cache高速缓冲型存储器 涉及到的知识点 有 Cache命中率 和 程序的局部性原理 以及 Cache与主存之间的映射方式 。

程序的局部性原理:时间局部性是指如果程序中的某条指令一旦执行,则不久之后该指令可能再次被执行;如果某数据被访问,则不久之后该数据可能再次被访问。空间局部性是指一旦程序访问了某个存储单元,则不久之后。其附近的存储单元也将被访问。

影响Cache命中率的因素:Cache容量大小,块的替换策略,Cache与主存之间的映射方式,块的大小

Cache与主存之间的映射方式:全相联映像方式(主存和高速缓存Cache各自划分相同大小的块,主存中的任一一块可以存入Cache中任一一块中)中,主存的块地址存放于Cache的块中,这样地址转换的工作就可以交给相联存储器来完成了。直接映像方式:主存按Cache大小分区,每个区域内块数相同,主存中不同区域中的块和Cache中的块顺序对应;组相联映像方式:组间直接映像,组内全相联。

Cache主要由控制部分和存储器部分组成,其中存储器部分用来存放主存的部分拷贝,控制部分用于判断CPU要访问的信息是否在Cache中;存储器的存取速率由快到慢依次为CPU内部寄存器、高速缓存Cache、主存和大容量磁盘。

主存即RAM,随机高速型缓冲性存储器,分为SRAM和DRAM两种;SRAM用触发器的稳态表示0和1,而DRAM则是靠电容上电荷的多少来表示0和1,考虑到漏电,所以需要定期的供电刷新。buffer就是 主存,即内存条 的一部分; 可以认为buffer 包括了 cached(预先读) 和 buffers(延迟写)。buffer 用于存储速度不同步的设备之间传输数据的区域,通过缓存区,可以使进程之间的相互等待变少,从而使 从速度慢的设备读入数据时,速度快的设备的操作进程不发生间断。总之,主存buffer缓冲区(包含buffers和cached)是为了提高内存和硬盘(或其他慢速I/O设备)之间的数据交换速度而设计的。

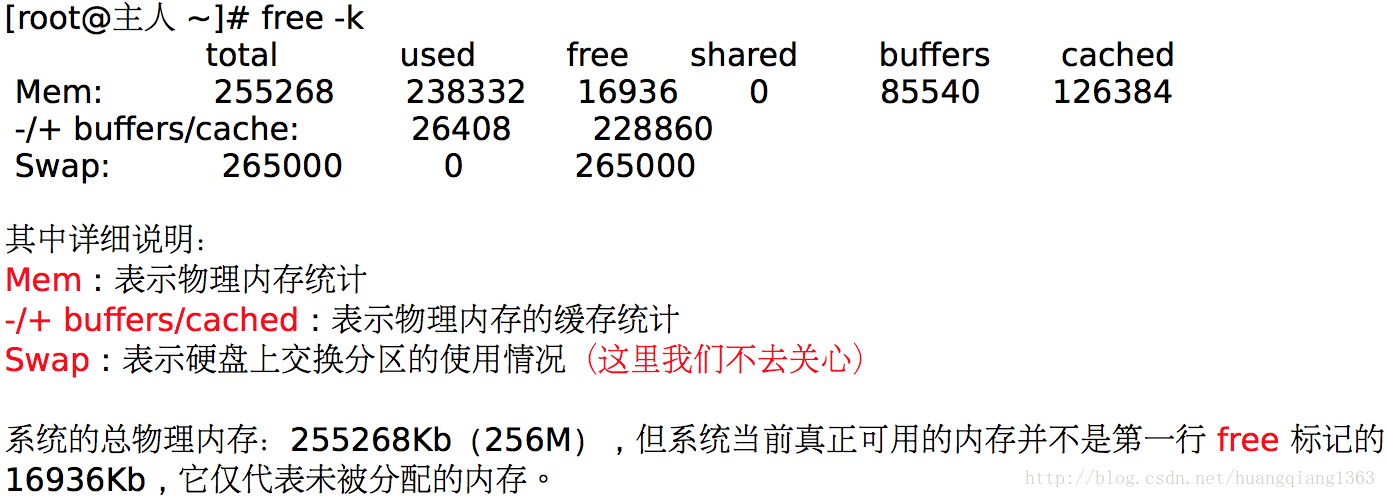

经典的free命令输出:这里引用某个博客的部分讲解 http://blog.csdn.net/hylongsuny/article/details/7742995

used1:

free1:

shared1:

buffers1: 系统分配但未被使用的buffers 数量。

cached1:

free2:

可以整理出如下等式: ---> 要知道公式 是怎么来的,自己能写的出来

total1 = used1 + free1

total1 = used2 + free2

used1

free2

正如上述所说的,buffers 和 cached 都是 物理内存(主存)的一部分(用于buffer的部分);不是 cache 高速缓冲型存储器的部分。

关于 linux 内存管理的机制: 这里强烈推荐一篇博客 http://blog.csdn.net/huangjin0507/article/details/51178768

2058

2058

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?