FPGA Implementation of White Gaussian Noise

前言

本设计使用开发工具为Quartus prime 18.1和Matlab 2018B

工程连接:

一、方案设计

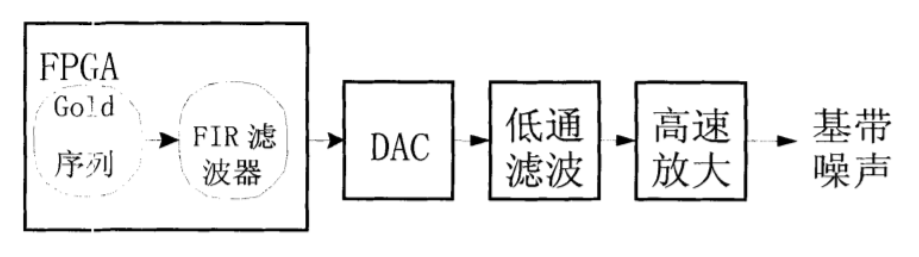

1、系统介绍

一种高斯白噪声发生器及实现方法,涉及噪声发生器技术领域。通过本发明的数字式高斯白噪声发生器实现在获得好的时域高斯噪声信号的同时,得到尽可能大的输出带宽。它包括:伪随机序列生成器,用来产生伪随机序列;FIR滤波器,对伪随机序列滤波,得到带限高斯白噪声序列;数模转换器,将数字信号转为模拟信号;低通滤波器,抑制带外噪声干扰;高速放大器,放大噪声信号。

2、系统流程图

3、模块分析

3.1 m值序列

定义:

如果一个序列,一方面它是可以预先确定的,并且是可以重复地生产和复制的;一方面它又具有某种随机序列的随机特性(即统计特性),我们便称这种序列为伪随机序列(m值序列)。

产生方法:

产生伪随机数的方法最常见的是利用一种线性反馈移位寄存器(LFSR),它是由n个D触发器和若干个异或门组成的。

LFSR:

线性反馈移位寄存器(linear feedback shift register,)

是指给定前一状态的输出,将该输出的线性函数再用作输入的移位寄存器。异或运算是最常见的单比特线性函数:对寄存器的某些位进行异或操作后作为输入,再对寄存器中的各比特进行整体移位。

LFSR产生的两种形式为伽罗瓦(Galois)和斐波那契(Fibonacci)两种形式。也有成为外部(External)执行方式和内部(Internal)执行方式,这里采用的是斐波那契形式。

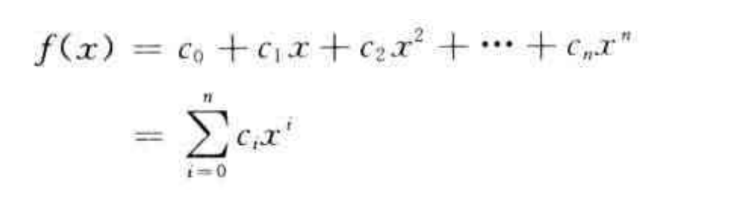

m序列反馈移位寄存器特征多项式:

本原多项式:

本原多项式是近世代数中的一个概念,是唯一分解整环上满足所有系数的最大公因数为1的多项式。本原多项式不等于零,与本原多项式相伴的多项式仍为本原多项式。

m序列是由线性反馈移存器产生的伪随机序列,而线性反馈移存器产生m序列的充要条件为:其特征多项式为本原多项式。只要找到本原多项式,就能由它构成m序列。

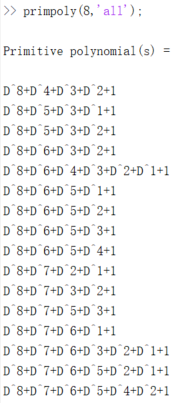

本原多项式的获得:

在matlab中运行如下代码

primpoly(8,'all');

获得全部本原多项式,原则其中一个即可,这里选择D8+D4+D3+D2+1

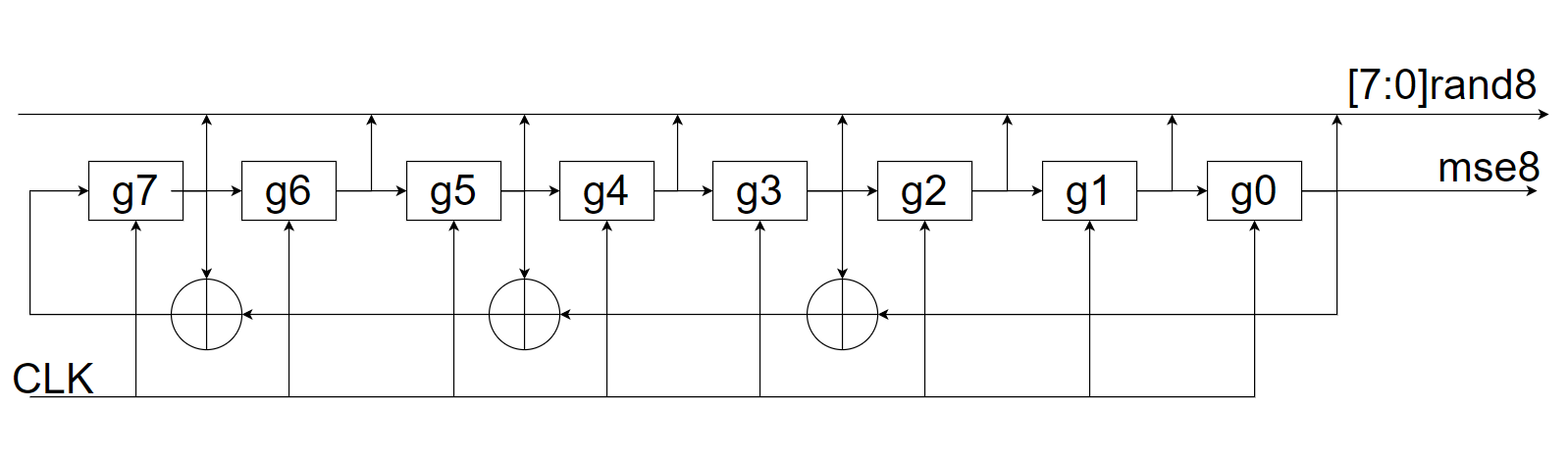

逻辑电路图:

3.2 Gold序列

Gold序列的原理:

m序列虽然具有良好的自相关特性,但是同周期的m序列数量不多,且并非所有的m序列之间互相关特性都好。

R.GOLD于1967年提出了一种基于m序列优选对的码序列,称为gold序列。这种序列具有良好的互相关特性,且生成简单,数量巨大,所以实际应用广泛。

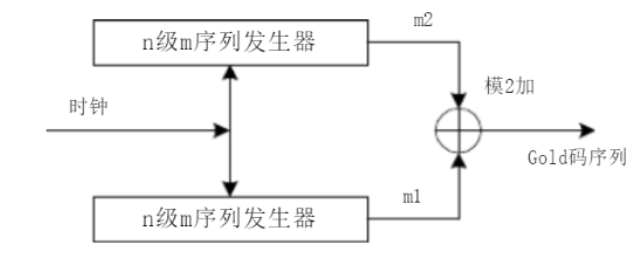

Gold序列的产生:

Gold 序列是m序列的组合码,由优选对的两个m序列逐位模二加得到,当改变其中一个m序列的相位时,可得到一个新的gold序列。也可以通过m序列优选对的两个本原多项式乘积形成的新多项式构成新移位寄存器的反馈系数,从而形成的gold序列。已经证明形成的2"-1长度的gold序列共有2"+1个。

m序列与Gold序列的比较:

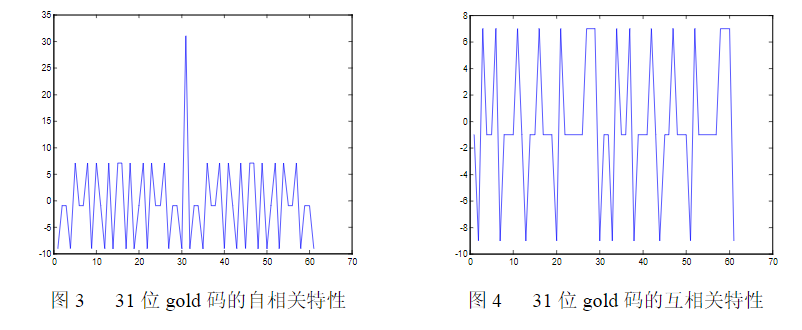

m序列自相关,互相关特性:

Gold序列自相关,互相关特性:

可以看到,m序列居于尖锐的自相关特性,且归一化相关值较小;而Gold序列的指向光特性具有尖锐的相关峰,但是自相关特性具有尖锐的相关峰,但是自相关旁瓣的值不唯一,是三值的,且归一化互相光值较小。

结论:在自相关恶心方面,m序列总体优于Gold序列,但在地址码的数量上,Gold序列具有明显的优势。

Gold序列逻辑电路图:

3.3 FIR滤波器

均匀分布序列转为高斯分布序列:

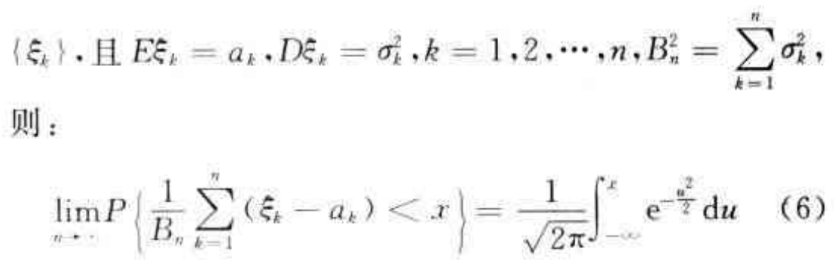

m序列的功率谱是固定的,要生成带宽可调的数字噪声序列需要对m序列进行低通数字滤波,由Lindeberg定理可知,设有独立水机变量序列

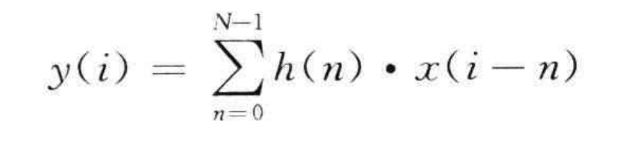

该定理证明了由大量微笑且独立了的随机因素引起,并累积而成的变量,必然是一个正态随机变量,FIR滤波器的单位冲激响应为h(n),0<=n<=N-1,则输入函数为x(i),则输出函数y(i)可以写成

FIR滤波器其输入端接收为Gold序列,该FIR滤波器用于对输入序列进行滤波,获得带限高斯白噪声序列。

3.4 高速DAC

AD9708芯片

本设计采用的AD9708是ADI公司(Analog Devices,Inc.,亚德诺半导体技术有限公司)生产的TxDAC系列数模转换器,具有高性能、低功耗的特点。AD9708的数模转换位数为8位,最大转换速度为125MSPS(每秒采样百万次Million Samples per Second)。

二、matlab实现

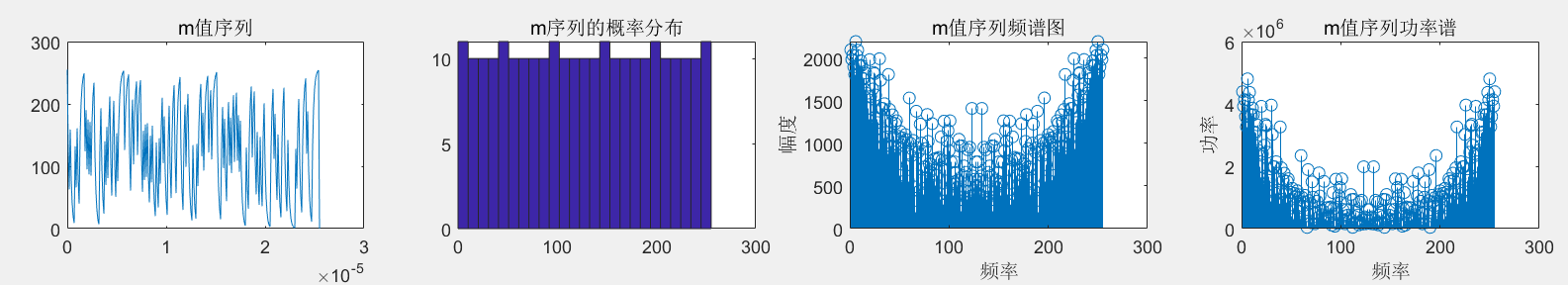

1、m值序列产生

%% m1序列产生

% m=8

% x^8+x^4+x^3+x^2+1

% 435

s1=[1 1 1 1 1 1 1 1];%输入序列

t1=[8 4 3 2];%本原多项式系数

%seg为m值序列线性输出值3,c为m值序列输出矩阵

[seq1 c1]=LFSRv1(s1,t1);%生成m序列矩阵

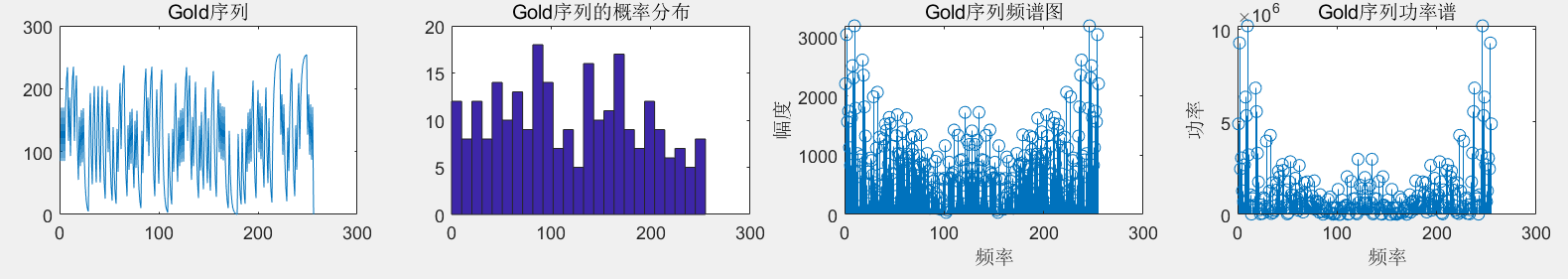

2、Gold序列合成

%% m序列转gold序列

cc = xor(c1,c2); %产生gold序列

for i = 1:N-1

Gold(i) = bit2dex(cc(i,:),8, 0);

end

Gold = [Gold,0];

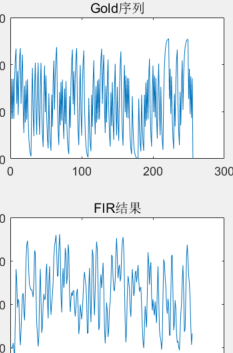

subplot(3,4,9);plot(Gold);title('Gold序列');

subplot(3,4,10); hist(Gold, 25);title('Gold序列的概率分布');

y4 = fft(Gold, N);

ay4 = abs(y4);

subplot(3,4,11);stem(ff(2:N),ay4(2:N));xlabel('频率');ylabel('幅度');title('Gold序列频谱图');

p4 = y4.*conj(y4);

subplot(3,4,12);stem(ff(2:N),p4(2:N));xlabel('频率');ylabel('功率');title('Gold序列功率谱');

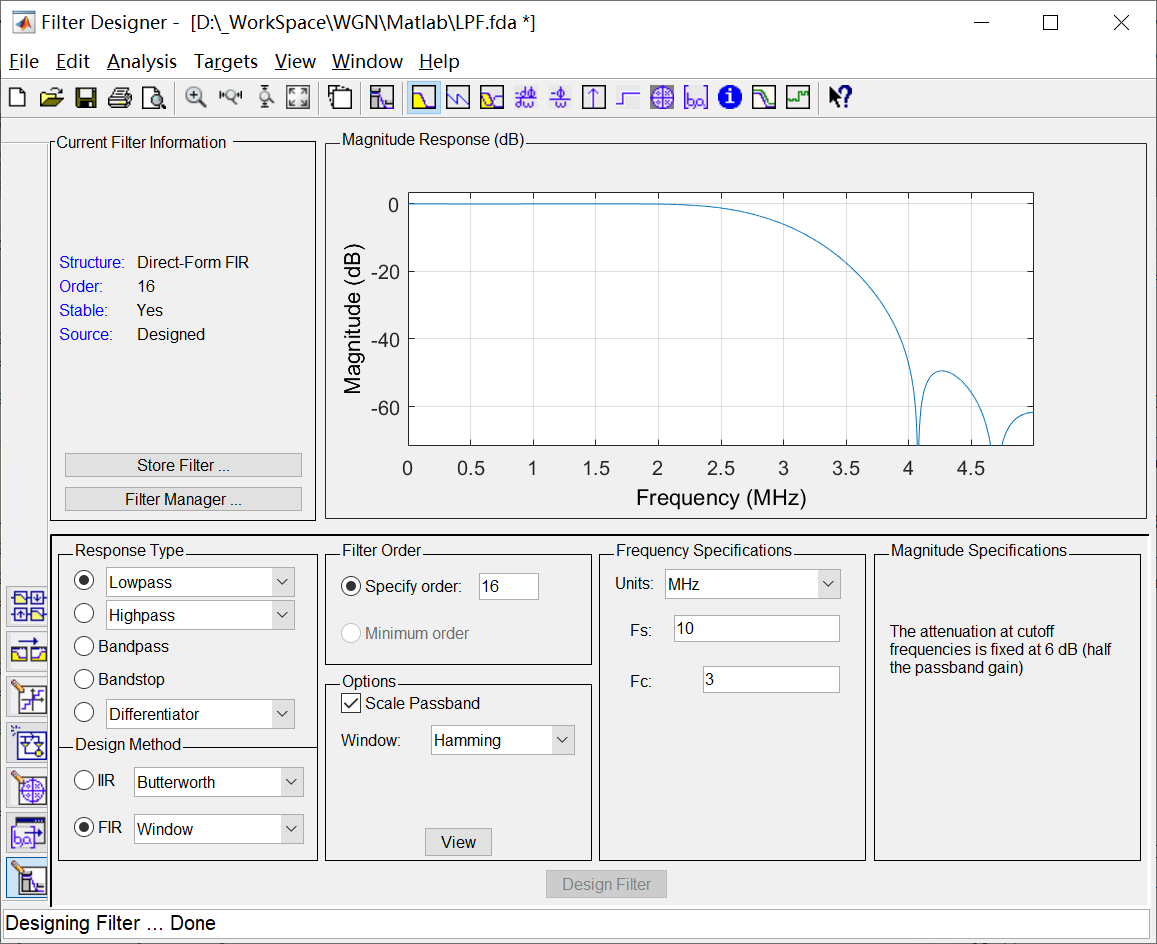

3、FIR滤波器设计

LPF滤波器设计

使用matlab自带fdatool设计所需要的FIR滤波器

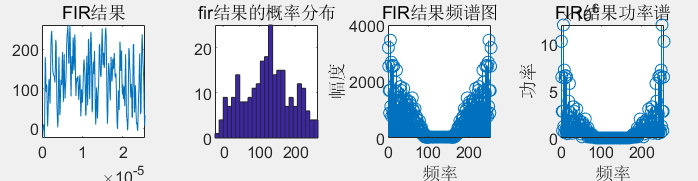

%% FIR滤波

LPF = LPF10M_40_3M;%FIR低通滤波,采样频率10M,15阶,截止频率3M

fir_output = filter(LPF,M1);%fir滤波

subplot(3,4,5);plot(t,fir_output);title('FIR结果');

subplot(3,4,6);hist(fir_output, Pn);title('fir结果的概率分布');

y2 = fft(fir_output, N);

ay2 = abs(y2);

subplot(3,4,7);stem(ff(2:N),ay2(2:N));xlabel('频率');ylabel('幅度');title('FIR结果频谱图');

p2 = y2.*conj(y2);

subplot(3,4,8);stem(ff(2:N),p2(2:N));xlabel('频率');ylabel('功率');title('FIR结果功率谱');

三、FPGA实现

1、m值序列产生

/*

m:x^8+x^4+x^3+x^2+1

*/

module msequence8#(

parameter seed= 8'b1111_1111

)(

input clk,

input rst_n,

input en,

output reg [31:0]num,

output mse8, //m sequence

output reg [7:0]rand8

);

assign mse8 = rand8[0];

always @ (posedge clk or negedge rst_n)begin

if(!rst_n) begin

rand8 <= seed;

num <= 32'd1;

end

else if(en) begin

rand8[0] <= rand8[1];

rand8[1] <= rand8[2];

rand8[2] <= rand8[3];

rand8[3] <= rand8[4];

rand8[4] <= rand8[5];

rand8[5] <= rand8[6];

rand8[6] <= rand8[7];

rand8[7] <= rand8[0] ^ rand8[4] ^ rand8[5] ^ rand8[6];

num <= num + 1'b1;

end

else

rand8 <= rand8;

end

endmodule

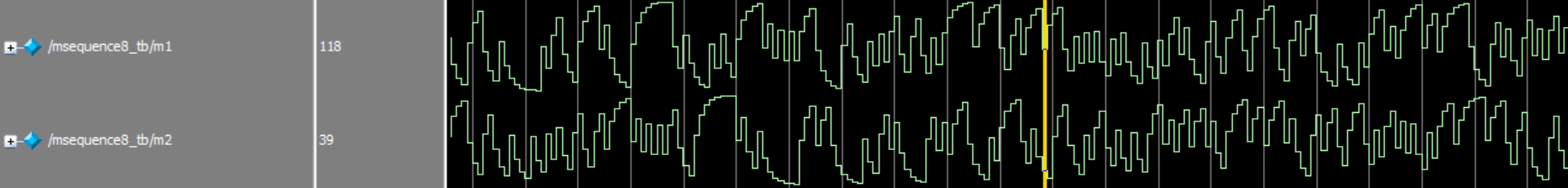

m1,m2序列仿真波形图:

2、Gold序列合成

//Gold序列产生

wire [7:0]Gold;

assign Gold = m1 ^ m2;

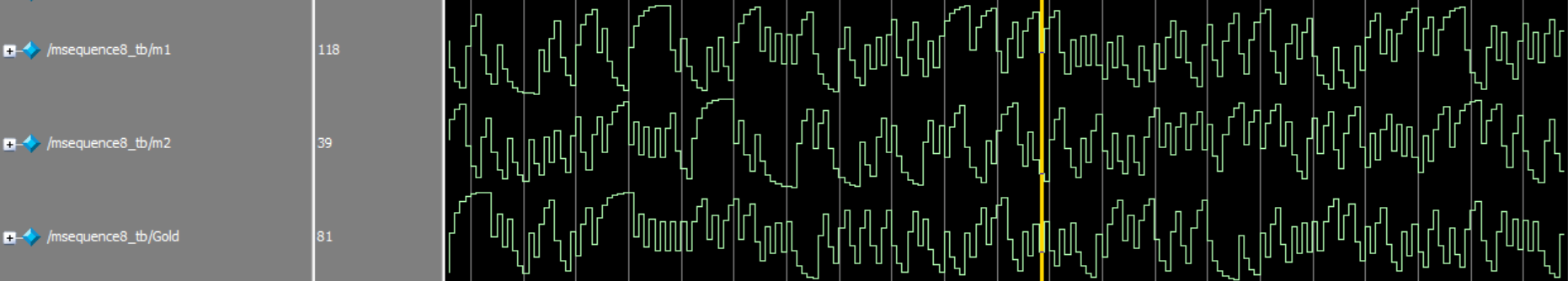

Gold序列仿真波形图:

3、FIR滤波器设计

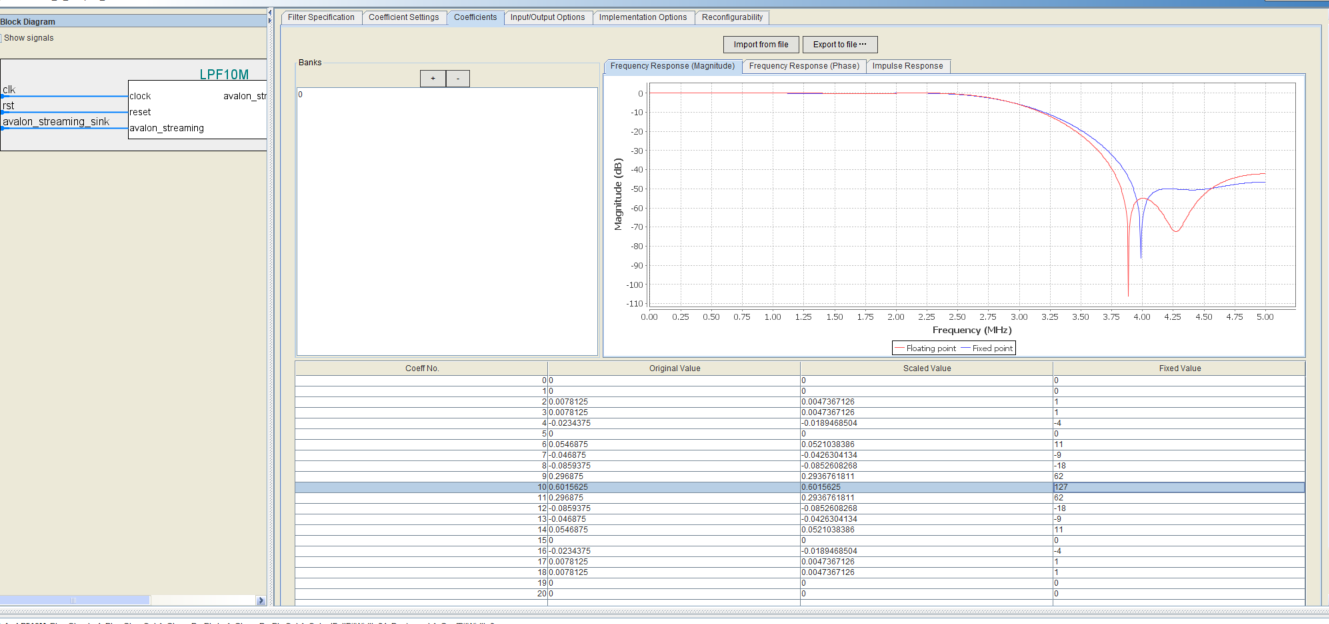

Quartus prime 18.1 FIR IP核调用:

//低通滤波

wire [20:0]fir_out;

wire source_valid;

wire [1:0] source_error;

LPF10M LPF10M(

.clk(clk),

.reset_n(rst_n),

.ast_sink_data(Gold), // data in

.ast_sink_valid(fs_10M), // fs

.ast_sink_error(2'd0), // data in error flag

.ast_source_data(fir_out), // data out

.ast_source_valid(source_valid), // data out valid flag

.ast_source_error(source_error) // data out error flag

);

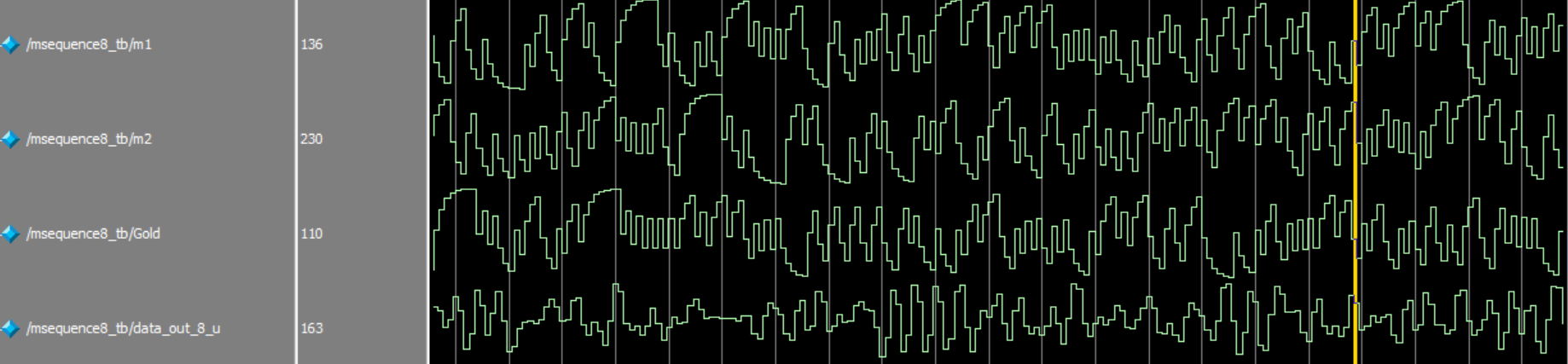

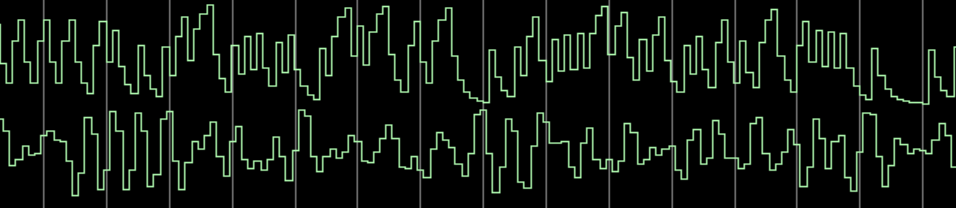

FIR结果仿真波形图:

四、高速DA模块设计

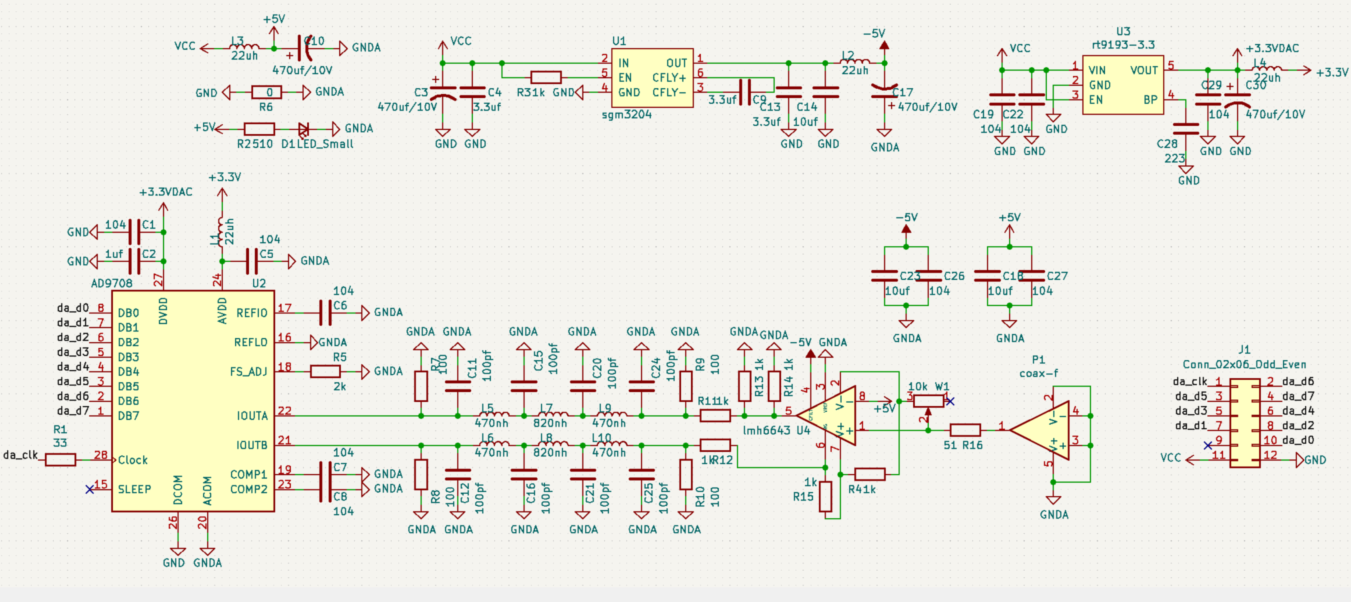

1、原理图设计

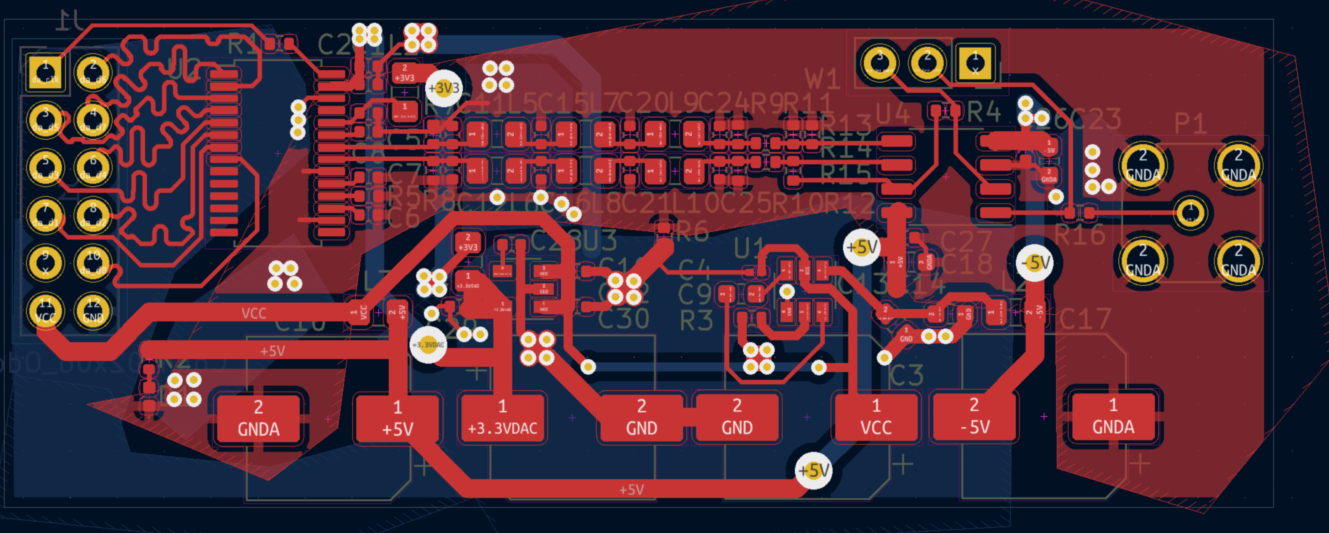

2、PCB设计

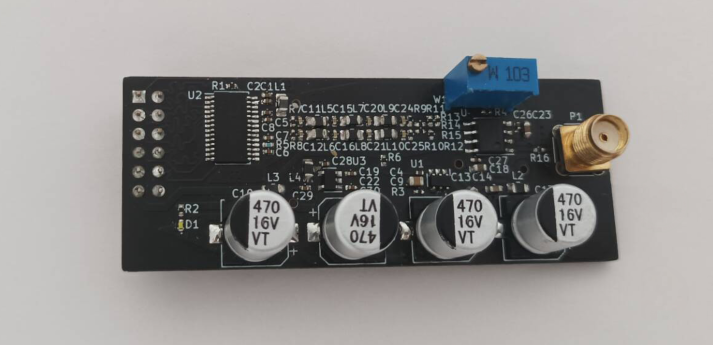

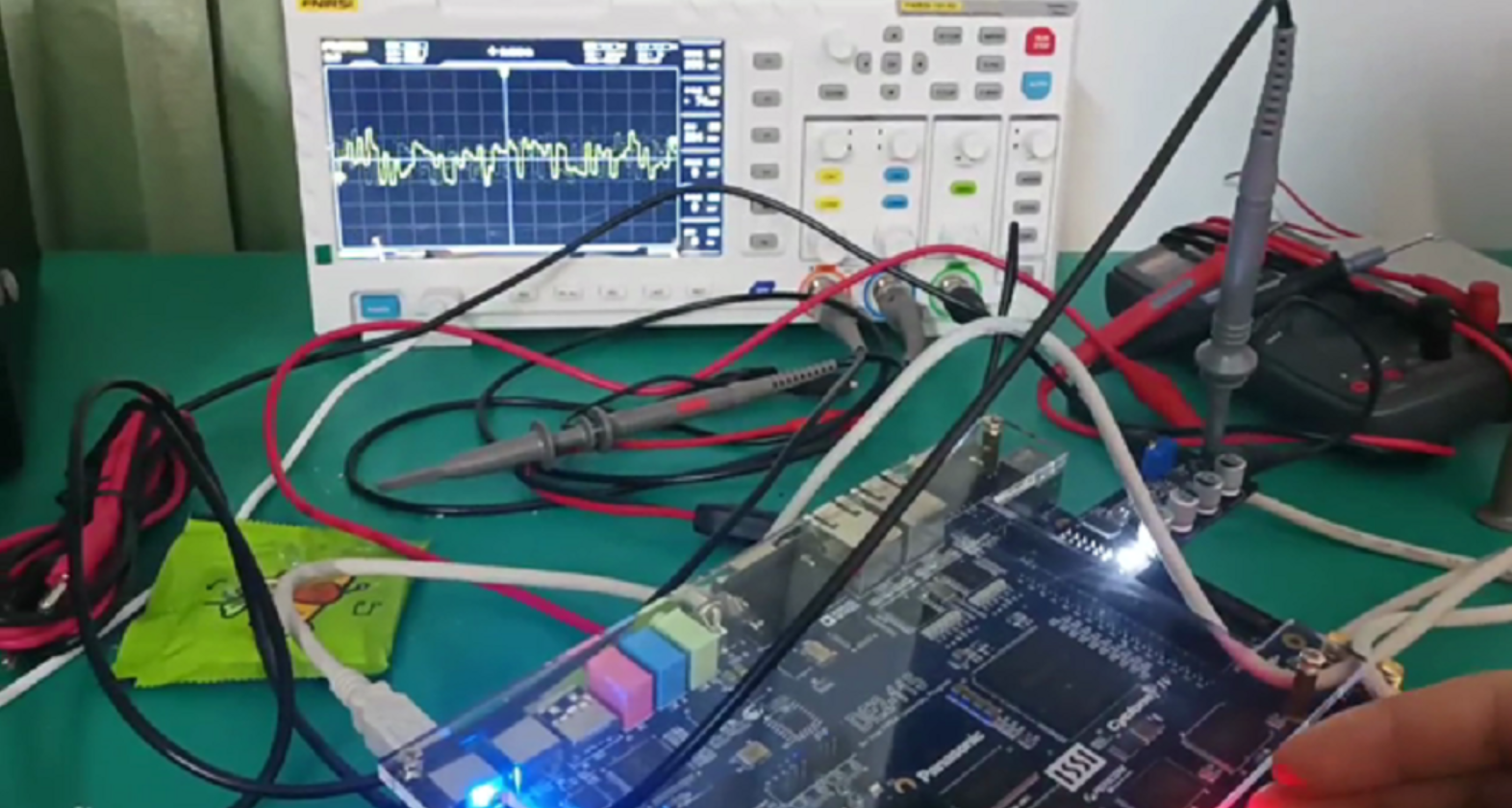

3、实物图

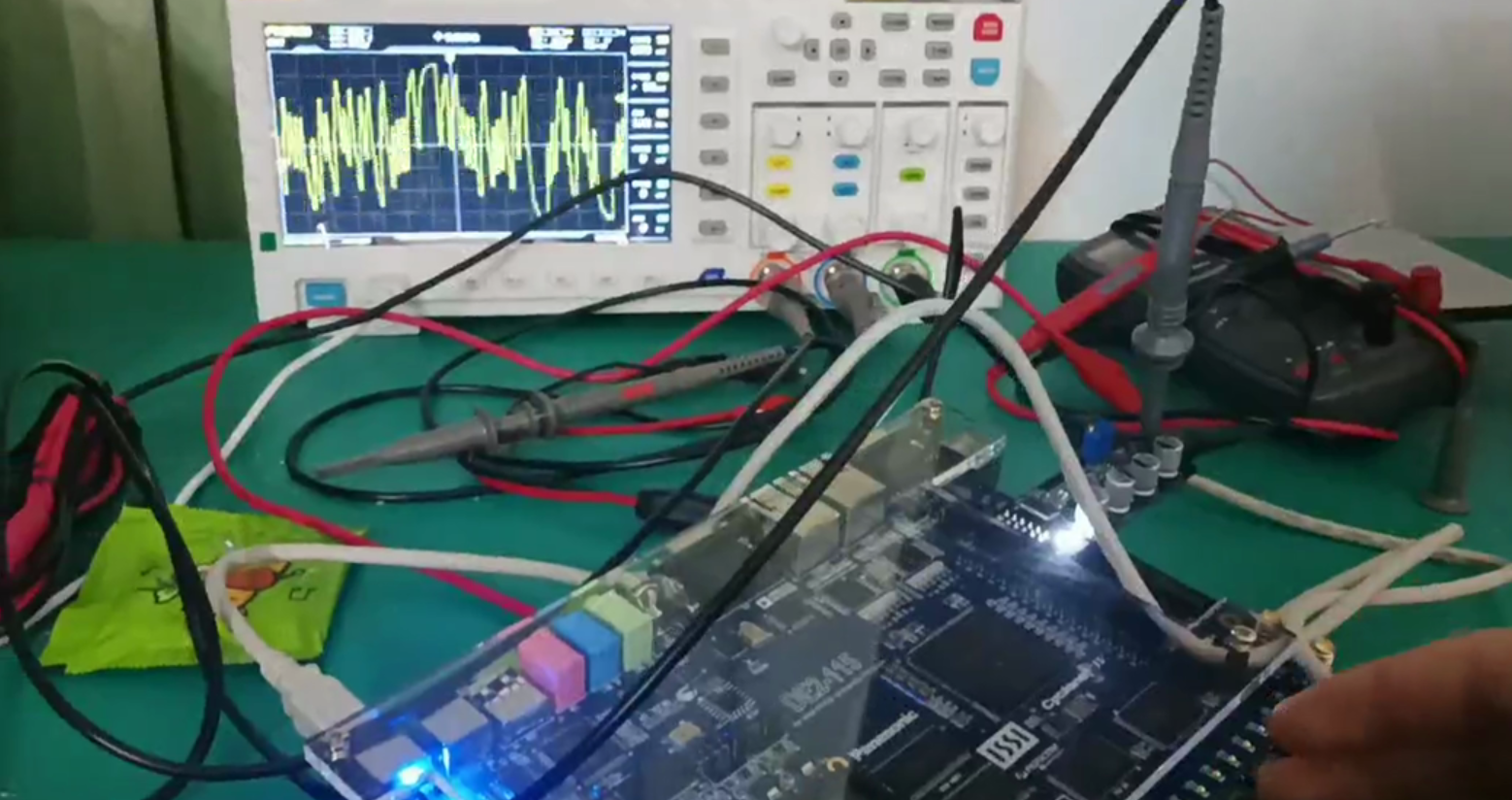

五、结果分析

1、实物

FIR滤波前:

输出序列服从均匀分布

FIR滤波后:

输出序列服从高斯分布

2、总结

本设计的核心思想就是利用m序列发生器产生均匀分布的伪随机序列,然后利用滤波、放大,数模转换等对其进行高斯化变换,得到了性能比较好的高斯白噪声信号。系统设计使用硬件描述语言VHDL实现,全数字化处理,可移植性强。另外,该高斯白噪声产生器的设计充分运用了FPGA内部丰富的布线资源,将噪声产生的过程集中在一个芯片上,从而就节约了电路板面积。FPGA器件本身所内嵌有很多模块,比如RAM模块、特殊功能模块,使本设计得到了进一步的优化,其性能有了很大的提高。同时,由于FPGA可以进行在线调试,这样一来就使调试和设计的周期大大缩短 了,约了宝贵的时间。系统设计采用了VHDL硬件描述语言编写,灵活性和通用性比较强,便于进行系统升级。同时该设计操作简单,容易控制,因此可以作为一个整体嵌入到其它工程领域中去,因而移植效果很好。

浮点定点对比

matlab浮点:

FPGA定点:

对比结果:

浮点结果比定点好

六、产考资料

- https://hal.archives-ouvertes.fr/hal-00347213/document

- https://www.docin.com/p-240171923.html&endPro=true

- http://www.youerw.com/tongxin/lunwen_910.html

- https://patentimages.storage.googleapis.com/37/da/fa/918e5e0d58a153/CN101807880A.pdf

- https://cloud.tencent.com/developer/article/1655498

- https://doc.mbalib.com/view/17a35269d4ca9df565aaacdf5754009f.html

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?