目前理解的一般,内容来自UVM实战

1.如何理解寄存器模型,意义是什么?

寄存器模型的本质就是重新定义了验证平台和DUT的寄存器接口,是验证人员更好的组织及配置寄存器,简化流程,减少工作量。通过这个模型就能读写DUT中寄存器的配置。

假如没有寄存器模型,在参考模型中读取寄存器的值非常麻烦:需要先在参考模型的控制下启动sequence来读取寄存器,随后需要通过config_db传递给参考模型,再在参考模型中通过wait_modified来更新数据。而在大的设计中,寄存器有很多个,为了区分这些寄存器,又需要其它配置。而通过寄存器模型的话,只需要一句程序即可实现。

假如没有寄存器,只能启动sequence通过前门读取寄存器,局限较大,有了寄存器模型后,在耗费时间的phase中可以前门访问读取寄存器的值,在不耗费时间的phase中,使用后门来读取寄存器的值

。

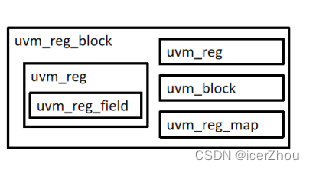

2.寄存器模型的基本概念

每个寄存器在加入寄存器模型时都有地址,这个地址是偏移地址。map就是存储这些地址,然后在前门访问时,将这些偏移地址转换成绝对地址。关于创建和连接,在单个寄存器的build中创建并配置data,在reg_block的build中创建单个寄存器,并通过creat_map创建map。

注意:

- uvm_reg在创建后还要调用 configure( )函数,将 uvm_reg 指定关联到哪个 uvm_reg_block 上;

- 在uvm_reg、uvm_reg_block 中都要定义 build( )函数,由于它们都是 object 类型,所以需要在上一层自己手动调用 build()函数,实现层层递进的寄存器配置。

3.集成adapter后的寄存器模型

前门访问:通过寄存器配置总线来对DUT进行操作。步骤如下:参考模型调用寄存器模型的读任务——寄存器模型产生sequence,并产生uvm_reg_item:rw——产生driver能接受的tranction(reg2bus)—将bus_req交给bus_sequencer——driver得到bus_req,驱动他读取值,放入rsp中,调用item_done——寄存器模型调用bus2reg将rsp中读取的值传递给rw——将re中的读数据返回给参考模型。//如果总线要返回response数据,应当在adapter中使能provides_response = 1;如果总线不支持返回RSP(如没有调用put_response(RSP)或item_done(RSP) ),则不能使能,否则adapter会致使验证环境挂起

后门访问:不通过DUT总线而对DUT内部的寄存器进行存储的操作。

二者比较:

后门优点1:不消耗仿真时间,在大型芯片的验证中,在工作前需要配置很多寄存器,配置时间可能长达几个小时,而通过后门访问时间能够大大缩小。

后门优点2:能完成前门访问操作不能完成的事情。如在实际应用中,有些计数器只读,无法指定非零初值,当测试计数器进位时,DUT中的计数器可能几天才会加1。而后门访问可以直接给只读的寄存器一个初值。

后门缺点1:前门访问可以在波形文件中找到总线信号变化的波形和所有操作的记录。后门访问不可以,增加了调试的难度。

集成:在顶层connect中,将map和bus sequencer和adapter连接,将三者关联在一起。

4.predictor以及镜像值

desired value:期望值、mirrored value:镜像值、actually value :真实值,DUT中寄存器的值是时刻都在变化的,寄存器模型并不能实时知道这种变更,对于任意一个寄存器模型,都会有一个值最大可能的和DUT保持同步,这个值就是镜像值。

一般是先更新软件的期望值,再更新硬件的实际值,再回来更新软件的镜像值。有两种方法,法1是通过write函数将值写入,此时镜像值和期望值都更新。法2时通过set设置期望值,通过update更新镜像值。

而通过前门访问的read和write,通常是显式预测,需要predictor,无论前门还是后门,通过read和write操作完成后,寄存器都会更新期望值和镜像值。如果没有独立的predictor,也可以通过自动预测。前门访问的操作是,monitor捕捉到的有效事物传给predictor,predictor通过bus2reg将数据给reg_map,然后map在更新寄存器模型的值。

peek和poke只能后门访问,通常是自动预测,也是根据结果更新期望值和镜像值

实际应用场景:可以先通过前门访问验证寄存器访问的物理通路工作正常,在前门访问被验证充分的前提下,可以在后续的测试中使用后门访问来节省访问多个寄存器的时间;

先通过后门访问随机化整个寄存器列表(在一定的随机限制),随后再通过前门访问来配置寄存器。好处在于,不再只是通过设置复位之后的寄存器这种更有确定性的场景,而是通过让测试序列一开始的寄存器值都随机化来模拟无法预期的硬件配置场景,可以检查意想不到的边界情况;

5.uvm_mem与uvm_reg的联系与差别

uvm_mem不支持预测和影子存储(即没有镜像值和期望值);

uvm_mem也支持前门访问和后门访问;

uvm_mem不但具有常规的访问方法read( )、write( )、peek( )和poke( ),也提供了burst_read( )

采用burst时,需要考虑目前挂载的总线UVC是否支持BURST访问,例如APB不支持

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?