🌈个人主页:羽晨同学

💫个人格言:“成为自己未来的主人~”

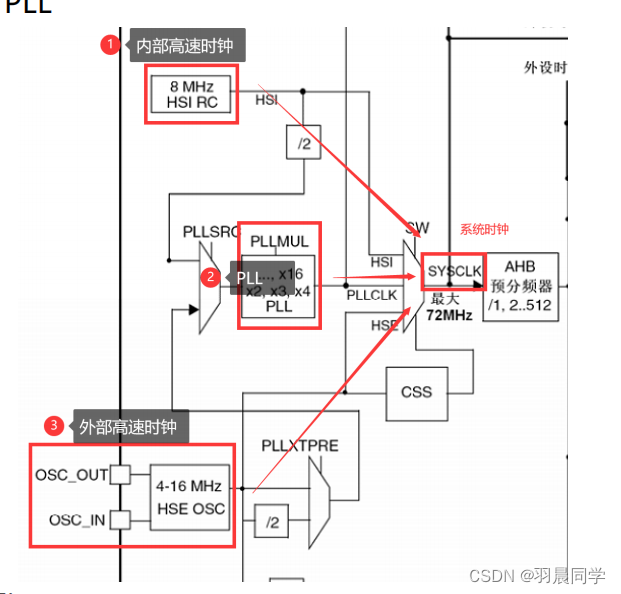

时钟的时钟源

- HSI振荡器时钟

- HSE振荡器时钟

- PLL 时钟

STM32中的系统时钟可被内部高速时钟(HSI),外部高速时钟(HSE)和PLL所驱动。

外部低速时钟(LSE):

可以被选择作为RTC时钟源

内部低速时钟(LSI):

一是作为独立看门狗时钟源。二是可以被选择作为RTC时钟源

系统时钟sysclk:

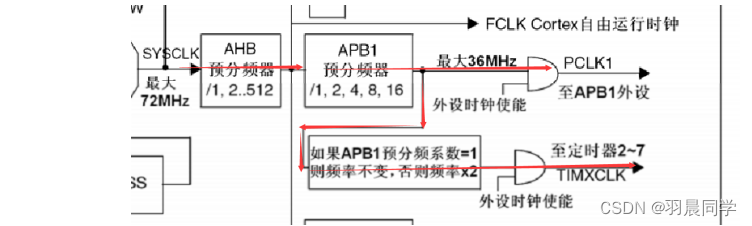

PCLK1&TIM2-7

这里我们可以看到PCLK最大是36MHz

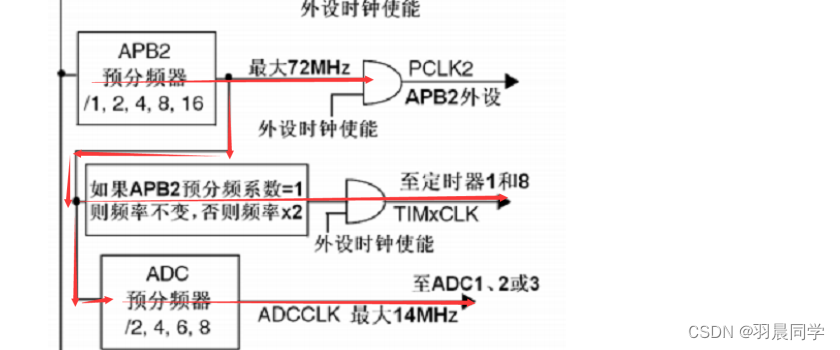

PCLK2&ADC&TIM1&TIM8

系统时钟的初始化

在系统初始化前期开启了内部高速时钟HSI

* Reset the RCC clock configuration to the default reset state(for debug purpose) */

/* Set HSION bit */

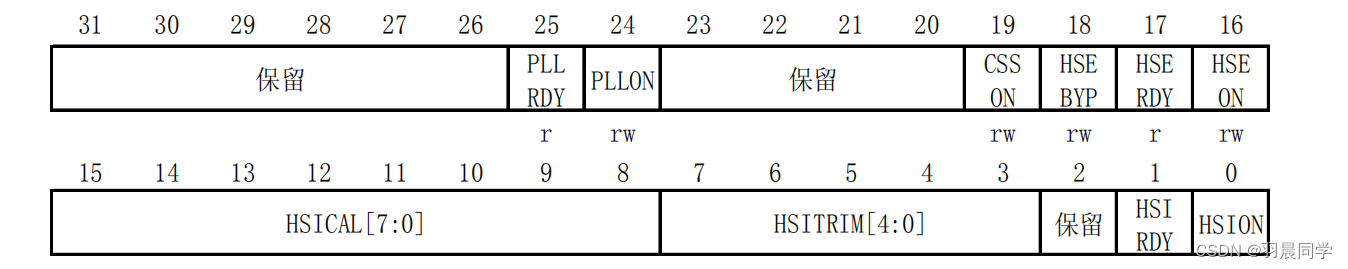

RCC->CR |= (uint32_t)0x00000001;要了解这个代码,我们可以先看看STM32的参考手册:

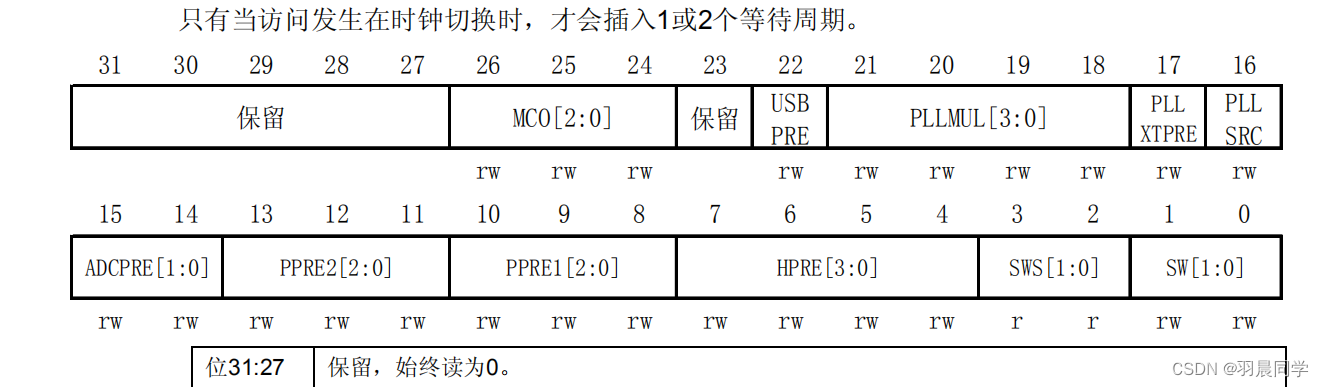

通过这张图我们可以了解到,上面的代码的目的是将RCC中CR的第0位置为1,其余置为0

而这样的做的目的是

开启内部高速时钟

/* Reset SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits */

#ifndef STM32F10X_CL

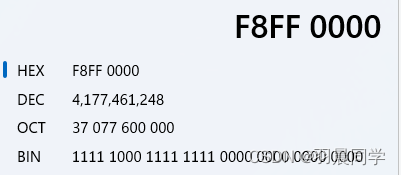

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else

RCC->CFGR &= (uint32_t)0xF0FF0000;接下来,我们来看看这段代码。

[1:0]=00(b)HSI作为系统时钟

[3:2]=00(b)SWS(SW状态标志位)

[7:4]=0000(b)SYSCLK不分频

[10:8]=000(b)SCLK不分频

[26:24]=000(b)MCO:没有时钟输出

设置系统时钟

static void SetSysClock(void)

{

#ifdef SYSCLK_FREQ_HSE

SetSysClockToHSE();

#elif defined SYSCLK_FREQ_24MHz

SetSysClockTo24();

#elif defined SYSCLK_FREQ_36MHz

SetSysClockTo36();

#elif defined SYSCLK_FREQ_48MHz

SetSysClockTo48();

#elif defined SYSCLK_FREQ_56MHz

SetSysClockTo56();

#elif defined SYSCLK_FREQ_72MHz

SetSysClockTo72();

#endif

/* If none of the define above is enabled, the HSI is used as System clock

source (default after reset) */

}分频情况:

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;HCLK和PCLK2没有进行分频

PCLK1进行了一次二分频

/* PLL configuration: PLLCLK = PREDIV1 * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL9);

#else

/* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);系统时钟源:PLL

选择外部高速晶振:8MHz

经过PLL倍频器9倍频后提供给sysclk=8*9=72MHz

HCLK没有对sysclk进行分频,所以HCLK=72MHz

PCLK1对HCLK进行2分频,所以PCLK1=36MHz

PCLK2对HCLK没有进行分频,所以PCLK2=72MHz

TIM2-7:72MHz

TIM1&TIM8:72MHz

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?