实验目的及设备需求

实验目的

(1)学习Quartus、Platform Designer、Nios II SBT的基本操作

(2)初步了解SOPC的开放流程,基本掌握Nios II软核的定制方法

(3)掌握Nios II软件的开发流程,软件的基本调试方法

实验设备

硬件:PC机、DE2-115FPGA实验开发平台

软件:Quartus 13.1、Nios II SBT

实验步骤

1)建立新项目

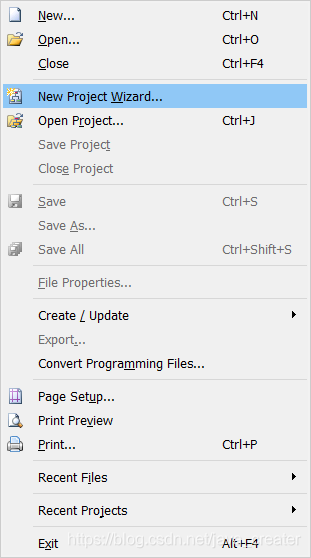

选择“file”–>“new project wizard…”

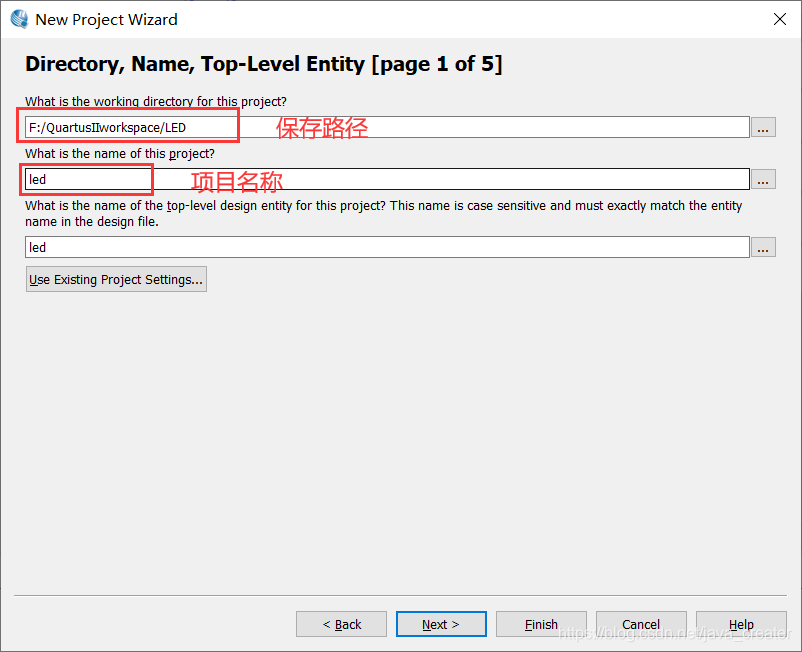

之后的对话框中点击“next”进入以下界面,选择文件保存地址以及项目名称,点击“next”

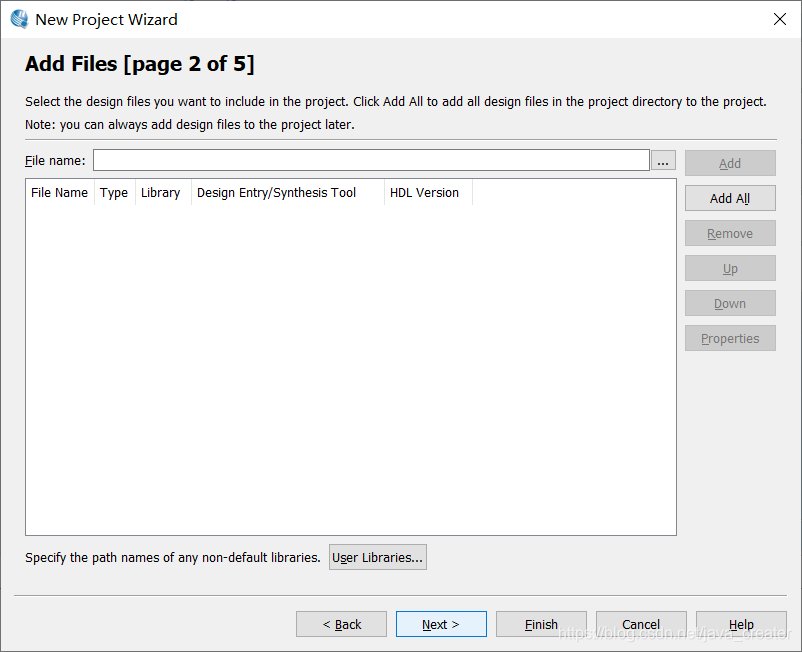

该页面为添加已有工程设计文件,我们这里不需要进行添加,直接点击“next”

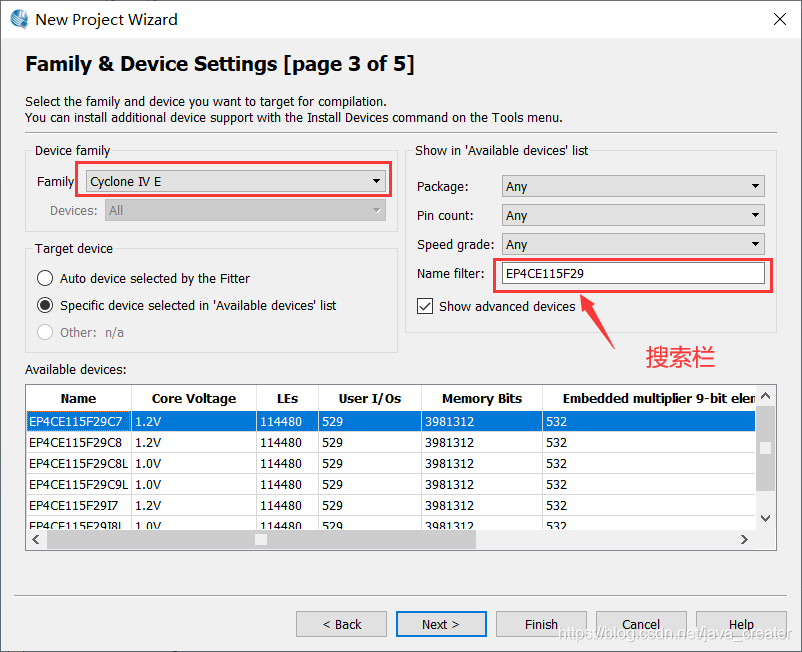

之后选择芯片的型号,目标芯片:cycloneIVE系列的EP4CE115F29C7

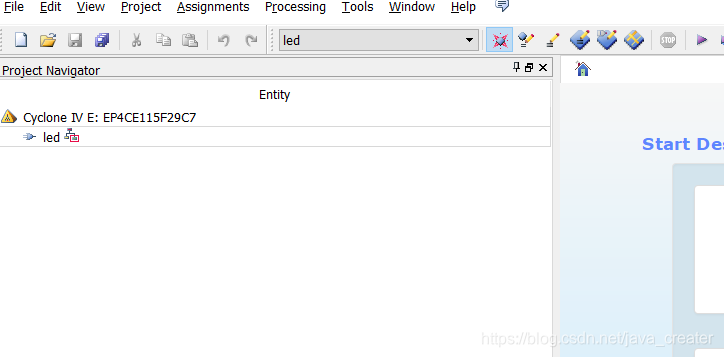

完成后界面会显示项目名和顶层文件名

2)进行Qsys系统设计

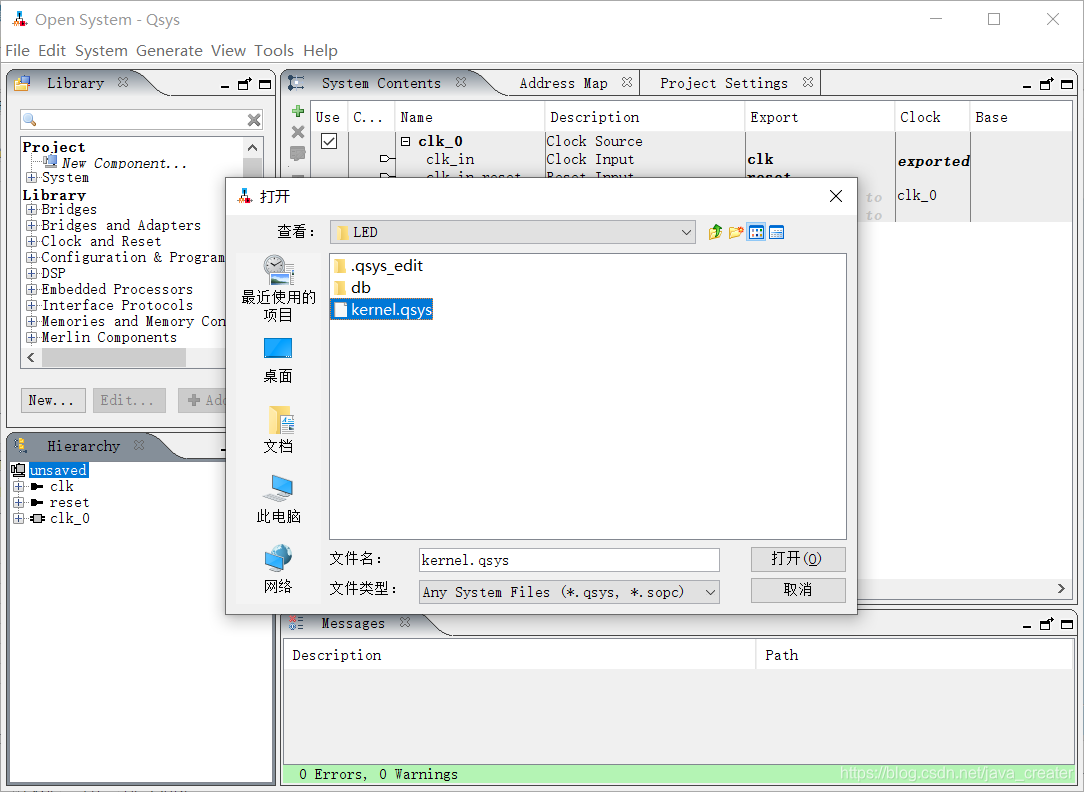

点击“tool”下拉菜单的“Qsys”工具,出现以下对话框

保存为“kernel.qsys”

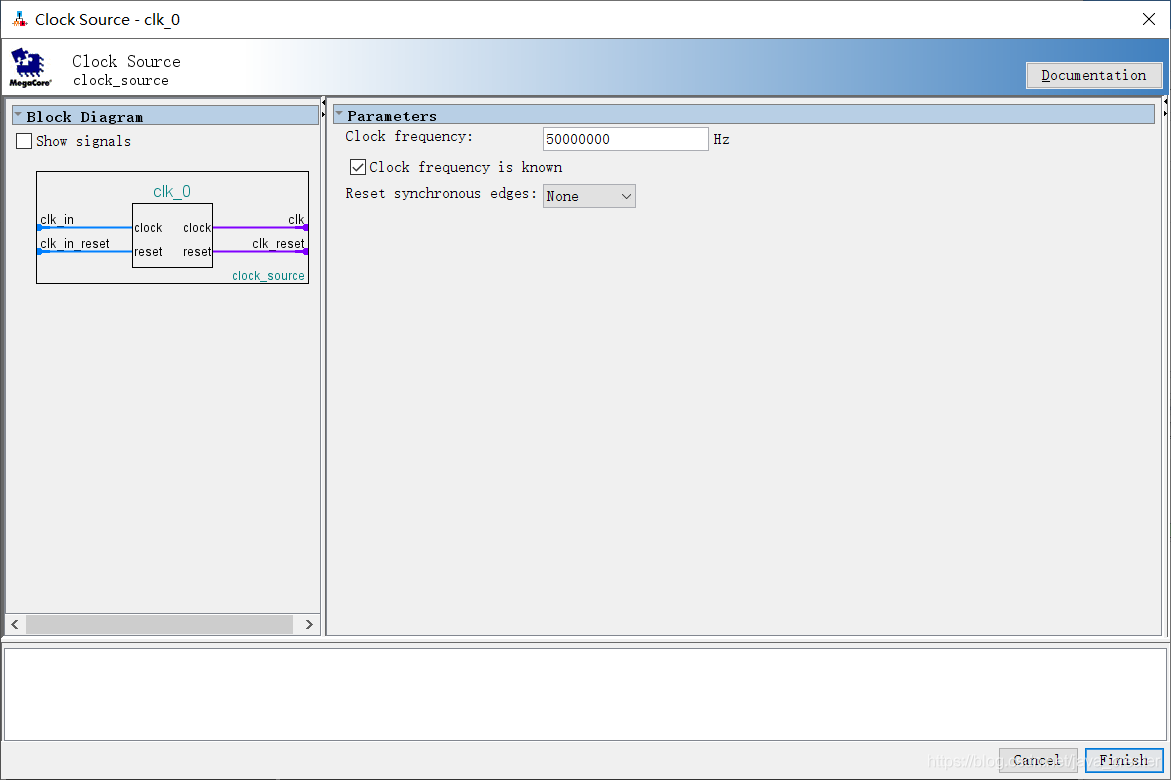

双击“clk_0”,对clock进行时钟设置,设为50m

添加CPU与外围器件,从PD的元件池中选择以下元件加入当前的系统

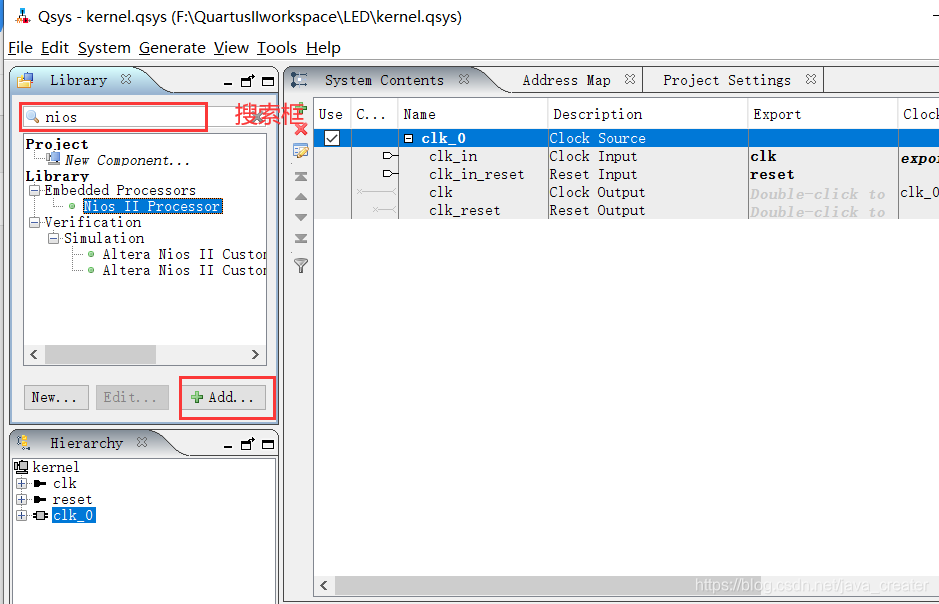

添加Nios II 32-bit CPU

直接在左上角搜索框内输入“nios”即可看到需要添加的内容,之后点击“add”即可

之后的窗口保持默认设置,点击“Finnish”

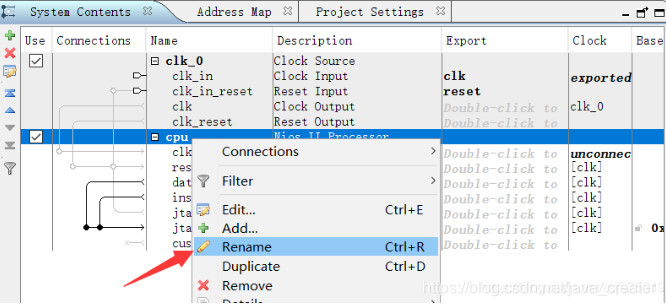

之后更改添加的Nios II 32-bit CPU名称为“CPU”

将 cpu 的 clk 和 reset_n 分别与系统时钟 clk_0 的 clk 和 clk_reset 相连

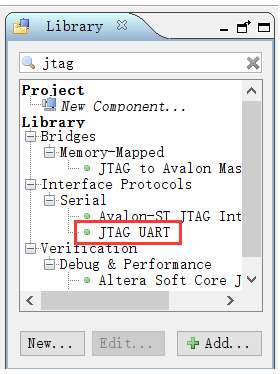

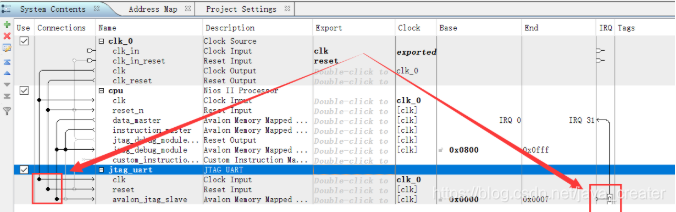

添加 jtag uart 接口

之后的窗口依旧保持默认配置,直接点击“finish”进行下一步,将其重命名为“jtag_uart”,clk、reset、avalon_jtag_slave 的连线,以及中断 irq 连线,中断号设为 0

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?