Linux版本号4.1.15 芯片I.MX6ULL 大叔学Linux 品人间百味 思文短情长

本节笔记的目录如下:

四、I.MX6ULL网络驱动简介

1.I.MX6ULL网络外设设备树

2.I.MX6ULL网络驱动源码简析

3.fec_netdev_ops操作集

4.Linux内核PHY子系统与MDIO总线简析

五、网络驱动实验测试

1.LAN8720 PHY驱动测试

2.通用PHY驱动测试

3.DHCP功能配置

六、单网卡使用

1.只使用ENET2网卡

2.只使用ENET1网卡

四、I.MX6ULL网络驱动简介

1.I.MX6ULL网络外设设备树

①、 必要属性

compatible:

reg:

interrupts

phy-mode

②、 可选属性

phy-reset-gpios

phy-reset-duration:1ms

phy-supply

phy-handle

fsl,num-tx-queues:1

fsl,num-rx-queues:2

fsl,magic-packet:支持硬件魔术帧唤醒。

fsl,wakeup_irq

stop-mode

③、可选子节点

PHY 节点相关属性

interrupts

interrupt-parent:句柄

reg

compatible:ethernet-phy-ieee802.3-c22、ethernet-phy-idAAAA.BBBB

max-speed

I.MX6ULL 的两个网络外设节点,如下所示:

1 &fec1 {//第 1~10 行: ENET1 网口的节点属性

2 pinctrl-names = "default";

3 pinctrl-0 = <&pinctrl_enet1//第 3、 4 行设置 ENET1 所使用的引脚 pinctrl 节点信息

4 &pinctrl_enet1_reset>;

5 phy-mode = "rmii";//第 5 行设置网络对应的 PHY 芯片接口为 RMII,这个要根据实际的硬件来设置。

6 phy-handle = <ðphy0>;//第 6 行设置 PHY 芯片的句柄为 ethphy0, MDIO 节点会设置 PHY 信。

7 phy-reset-gpios = <&gpio5 7 GPIO_ACTIVE_LOW>;

8 phy-reset-duration = <200>;

9 status = "okay";

10 };

11

12 &fec2 {//第 12~36 行: ENET2 网口的节点属性

13 pinctrl-names = "default";

14 pinctrl-0 = <&pinctrl_enet2

15 &pinctrl_enet2_reset>;

16 phy-mode = "rmii";

17 phy-handle = <ðphy1>;

18 phy-reset-gpios = <&gpio5 8 GPIO_ACTIVE_LOW>;

19 phy-reset-duration = <200>;

20 status = "okay";

21

22 mdio {//mido 子节点用于描述 MIDO 总线

23 #address-cells = <1>;

24 #size-cells = <0>;

25

26 ethphy0: ethernet-phy@0 {

27 compatible = "ethernet-phy-ieee802.3-c22";

28 reg = <0>;

29 };

30

31 ethphy1: ethernet-phy@1 {

32 compatible = "ethernet-phy-ieee802.3-c22";

33 reg = <1>;

34 };

35 };

36 };设备树中网络相关引脚的描述

1 pinctrl_enet1: enet1grp {

2 fsl,pins = <

3 MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

4 MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

5 MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

6 MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

7 MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

8 MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

9 MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

10 MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b009

11 >;

12 };

13

14 pinctrl_enet2: enet2grp {

15 fsl,pins = <

16 MX6UL_PAD_GPIO1_IO07__ENET2_MDC 0x1b0b0

17 MX6UL_PAD_GPIO1_IO06__ENET2_MDIO 0x1b0b0

18 MX6UL_PAD_ENET2_RX_EN__ENET2_RX_EN 0x1b0b0

19 MX6UL_PAD_ENET2_RX_ER__ENET2_RX_ER 0x1b0b0

20 MX6UL_PAD_ENET2_RX_DATA0__ENET2_RDATA00 0x1b0b0

21 MX6UL_PAD_ENET2_RX_DATA1__ENET2_RDATA01 0x1b0b0

22 MX6UL_PAD_ENET2_TX_EN__ENET2_TX_EN 0x1b0b0

23 MX6UL_PAD_ENET2_TX_DATA0__ENET2_TDATA00 0x1b0b0

24 MX6UL_PAD_ENET2_TX_DATA1__ENET2_TDATA01 0x1b0b0

25 MX6UL_PAD_ENET2_TX_CLK__ENET2_REF_CLK2 0x4001b009

26 >;

27 };

28

29 /*enet1 reset zuozhongkai*///之所以分两部分主 要 是 因 为 ENET1 的 复 位 引 脚 为 //GPIO5_IO07 , 而 GPIO5_IO07 对 应 的 引 脚 就 是SNVS_TAMPER7,要放到 iomuxc_snvs 节点,

//所以就分成了两部分。

30 pinctrl_enet1_reset: enet1resetgrp {

31 fsl,pins = <

32 /* used for enet1 reset */

33 MX6ULL_PAD_SNVS_TAMPER7__GPIO5_IO07 0x10B0

34 >;

35 };

36

37 /*enet2 reset zuozhongkai*/

38 pinctrl_enet2_reset: enet2resetgrp {

39 fsl,pins = <

40 /* used for enet2 reset */

41 MX6ULL_PAD_SNVS_TAMPER8__GPIO5_IO08 0x10B0

42 >;

43 };2.I.MX6ULL网络驱动源码简析

1)fec_probe 函数简析

外设驱动,芯片驱动

网络控制器部分驱动:

1 static const struct of_device_id fec_dt_ids[] = {

2 { .compatible = "fsl,imx25-fec", .data =

&fec_devtype[IMX25_FEC], },

3 { .compatible = "fsl,imx27-fec", .data =

&fec_devtype[IMX27_FEC], },

4 { .compatible = "fsl,imx28-fec", .data =

&fec_devtype[IMX28_FEC], },

5 { .compatible = "fsl,imx6q-fec", .data =

&fec_devtype[IMX6Q_FEC], },

6 { .compatible = "fsl,mvf600-fec", .data =

&fec_devtype[MVF600_FEC], },

7 { .compatible = "fsl,imx6sx-fec", .data =

&fec_devtype[IMX6SX_FEC], },

8 { .compatible = "fsl,imx6ul-fec", .data =//匹配表包含“fsl,imx6ul-fec”,因此设备树和驱动匹配上,当匹配成功以后第 19 行的 fec_probe 函数就会执行。

&fec_devtype[IMX6UL_FEC], },

9 { /* sentinel */ }

10 };

11

12 static struct platform_driver fec_driver = {

13 .driver = {

14 .name = DRIVER_NAME,

15 .pm = &fec_pm_ops,

16 .of_match_table = fec_dt_ids,

17 },

18 .id_table = fec_devtype,

19 .probe = fec_probe,

20 .remove = fec_drv_remove,

21 };fec_probe 函数:

1 static int fec_probe(struct platform_device *pdev)

2 {

3 struct fec_enet_private *fep;

4 struct fec_platform_data *pdata;

5 struct net_device *ndev;

6 int i, irq, ret = 0;

7 struct resource *r;

8 const struct of_device_id *of_id;

9 static int dev_id;

10 struct device_node *np = pdev->dev.of_node, *phy_node;

11 int num_tx_qs;

12 int num_rx_qs;

13

14 fec_enet_get_queue_num(pdev, &num_tx_qs, &num_rx_qs);

15

16 /* Init network device */

17 ndev = alloc_etherdev_mqs(sizeof(struct fec_enet_private),

18 num_tx_qs, num_rx_qs);

19 if (!ndev)

20 return -ENOMEM;

21

22 SET_NETDEV_DEV(ndev, &pdev->dev);

23

24 /* setup board info structure */

25 fep = netdev_priv(ndev);

26

27 of_id = of_match_device(fec_dt_ids, &pdev->dev);

28 if (of_id)

29 pdev->id_entry = of_id->data;

30 fep->quirks = pdev->id_entry->driver_data;

31

32 fep->netdev = ndev;

33 fep->num_rx_queues = num_rx_qs;

34 fep->num_tx_queues = num_tx_qs;

35

36 #if !defined(CONFIG_M5272)

37 /* default enable pause frame auto negotiation */

38 if (fep->quirks & FEC_QUIRK_HAS_GBIT)

39 fep->pause_flag |= FEC_PAUSE_FLAG_AUTONEG;

40 #endif

41

42 /* Select default pin state */

43 pinctrl_pm_select_default_state(&pdev->dev);

44

45 r = platform_get_resource(pdev, IORESOURCE_MEM, 0);

46 fep->hwp = devm_ioremap_resource(&pdev->dev, r);

47 if (IS_ERR(fep->hwp)) {

48 ret = PTR_ERR(fep->hwp);

49 goto failed_ioremap;

50 }

51

52 fep->pdev = pdev;

53 fep->dev_id = dev_id++;

54

55 platform_set_drvdata(pdev, ndev);

56

57 fec_enet_of_parse_stop_mode(pdev);

58

59 if (of_get_property(np, "fsl,magic-packet", NULL))

60 fep->wol_flag |= FEC_WOL_HAS_MAGIC_PACKET;

61

62 phy_node = of_parse_phandle(np, "phy-handle", 0);

63 if (!phy_node && of_phy_is_fixed_link(np)) {

64 ret = of_phy_register_fixed_link(np);

65 if (ret < 0) {

66 dev_err(&pdev->dev,

67 "broken fixed-link specification\n");

68 goto failed_phy;

69 }

70 phy_node = of_node_get(np);

71 }

72 fep->phy_node = phy_node;

73

74 ret = of_get_phy_mode(pdev->dev.of_node);

75 if (ret < 0) {

76 pdata = dev_get_platdata(&pdev->dev);

77 if (pdata)

78 fep->phy_interface = pdata->phy;

79 else

80 fep->phy_interface = PHY_INTERFACE_MODE_MII;

81 } else {

82 fep->phy_interface = ret;

83 }

84

85 fep->clk_ipg = devm_clk_get(&pdev->dev, "ipg");

86 if (IS_ERR(fep->clk_ipg)) {

87 ret = PTR_ERR(fep->clk_ipg);

88 goto failed_clk;

89 }

90

91 fep->clk_ahb = devm_clk_get(&pdev->dev, "ahb");

92 if (IS_ERR(fep->clk_ahb)) {

93 ret = PTR_ERR(fep->clk_ahb);

94 goto failed_clk;

95 }

96

97 fep->itr_clk_rate = clk_get_rate(fep->clk_ahb);

98

99 /* enet_out is optional, depends on board */

100 fep->clk_enet_out = devm_clk_get(&pdev->dev, "enet_out");

101 if (IS_ERR(fep->clk_enet_out))

102 fep->clk_enet_out = NULL;

103

104 fep->ptp_clk_on = false;

105 mutex_init(&fep->ptp_clk_mutex);

106

107 /* clk_ref is optional, depends on board */

108 fep->clk_ref = devm_clk_get(&pdev->dev, "enet_clk_ref");

109 if (IS_ERR(fep->clk_ref))

110 fep->clk_ref = NULL;

111

112 fep->bufdesc_ex = fep->quirks & FEC_QUIRK_HAS_BUFDESC_EX;

113 fep->clk_ptp = devm_clk_get(&pdev->dev, "ptp");

114 if (IS_ERR(fep->clk_ptp)) {

115 fep->clk_ptp = NULL;

116 fep->bufdesc_ex = false;

117 }

118

119 pm_runtime_enable(&pdev->dev);

120 ret = fec_enet_clk_enable(ndev, true);

121 if (ret)

122 goto failed_clk;

123

124 fep->reg_phy = devm_regulator_get(&pdev->dev, "phy");

125 if (!IS_ERR(fep->reg_phy)) {

126 ret = regulator_enable(fep->reg_phy);

127 if (ret) {

128 dev_err(&pdev->dev,

129 "Failed to enable phy regulator: %d\n", ret);

130 goto failed_regulator;

131 }

132 } else {

133 fep->reg_phy = NULL;

134 }

135

136 fec_reset_phy(pdev);

137

138 if (fep->bufdesc_ex)

139 fec_ptp_init(pdev);

140

141 ret = fec_enet_init(ndev);

142 if (ret)

143 goto failed_init;

144

145 for (i = 0; i < FEC_IRQ_NUM; i++) {

146 irq = platform_get_irq(pdev, i);

147 if (irq < 0) {

148 if (i)

149 break;

150 ret = irq;

151 goto failed_irq;

152 }

153 ret = devm_request_irq(&pdev->dev, irq, fec_enet_interrupt,

154 0, pdev->name, ndev);

155 if (ret)

156 goto failed_irq;

157

158 fep->irq[i] = irq;

159 }

160

161 ret = of_property_read_u32(np, "fsl,wakeup_irq", &irq);

162 if (!ret && irq < FEC_IRQ_NUM)

163 fep->wake_irq = fep->irq[irq];

164 else

165 fep->wake_irq = fep->irq[0];

166

167 init_completion(&fep->mdio_done);

168 ret = fec_enet_mii_init(pdev);

169 if (ret)

170 goto failed_mii_init;

171

172 /* Carrier starts down, phylib will bring it up */

173 netif_carrier_off(ndev);

174 fec_enet_clk_enable(ndev, false);

175 pinctrl_pm_select_sleep_state(&pdev->dev);

176

177 ret = register_netdev(ndev);

178 if (ret)

179 goto failed_register;

180

181 device_init_wakeup(&ndev->dev, fep->wol_flag &

182 FEC_WOL_HAS_MAGIC_PACKET);

183

184 if (fep->bufdesc_ex && fep->ptp_clock)

185 netdev_info(ndev, "registered PHC device %d\n", fep->dev_id);

186

187 fep->rx_copybreak = COPYBREAK_DEFAULT;

188 INIT_WORK(&fep->tx_timeout_work, fec_enet_timeout_work);

189 return 0;

......

206 return ret;

207 }通过一个 MDIO 接口可以配置多个 PHY 芯片.

如果我们要更换其他的网络PHY 芯片,第一步就是要修改设备树中的 PHY 地址。

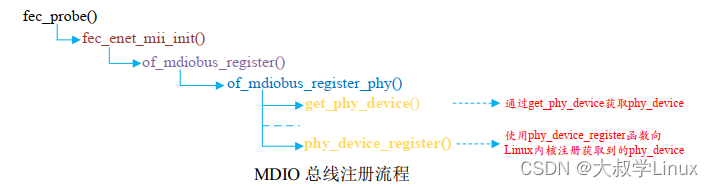

2)MDIO 总线注册

MDIO就是用来管理PHY芯片的,分为MDIO和MDC两根线。

mii_bus 结构体:

1 struct mii_bus {

2 const char *name;

3 char id[MII_BUS_ID_SIZE];

4 void *priv;

5 int (*read)(struct mii_bus *bus, int phy_id, int regnum);//读/些 PHY 芯片的操作函数

6 int (*write)(struct mii_bus *bus, int phy_id, int regnum,

u16 val);

7 int (*reset)(struct mii_bus *bus);

8 9

/*

10 * A lock to ensure that only one thing can read/write

11 * the MDIO bus at a time

12 */

13 struct mutex mdio_lock;

14

15 struct device *parent;

16 enum {

17 MDIOBUS_ALLOCATED = 1,

18 MDIOBUS_REGISTERED,

19 MDIOBUS_UNREGISTERED,

20 MDIOBUS_RELEASED,

21 } state;

22 struct device dev;

23

24 /* list of all PHYs on bus */

25 struct phy_device *phy_map[PHY_MAX_ADDR];

26

27 /* PHY addresses to be ignored when probing */

28 u32 phy_mask;

29

30 /*

31 * Pointer to an array of interrupts, each PHY's

32 * interrupt at the index matching its address

33 */

34 int *irq;

35 }; fec_probe 函数会调用 fec_enet_mii_init 函数完成 MII 接口的初始化,其中就包括初始化 mii_bus 下的 read 和 write 这两个函数。最终通过 of_mdiobus_register或者 mdiobus_register 函数将初始化以后的 mii_bus 注册到 Linux 内核, of_mdiobus_register 函数其实最终也是调用的 mdiobus_register 函数来完成 mii_bus 注册的.

of_mdiobus_register 函数有两个主要的功能,一个是通过 mdiobus_register函数向 Linux 内核注册 mdio 总线,另一个就是通过 of_mdiobus_register_phy 函数向内核注册PHY。

3)fec_drv_remove 函数简析

卸载 I.MX6ULL 网络驱动的时候 fec_drv_remove 函数就会执行,函数内容如下所示:

1 static int fec_drv_remove(struct platform_device *pdev)

2 {

3 struct net_device *ndev = platform_get_drvdata(pdev);

4 struct fec_enet_private *fep = netdev_priv(ndev);

5 6

cancel_delayed_work_sync(&fep->time_keep);

7 cancel_work_sync(&fep->tx_timeout_work);

8 unregister_netdev(ndev);

9 fec_enet_mii_remove(fep);

10 if (fep->reg_phy)

11 regulator_disable(fep->reg_phy);

12 if (fep->ptp_clock)

13 ptp_clock_unregister(fep->ptp_clock);

14 of_node_put(fep->phy_node);

15 free_netdev(ndev);

16

17 return 0;

18 }本章的内容实在是太多了,以下内容在下次笔记中给出:

3.fec_netdev_ops操作集

4.Linux内核PHY子系统与MDIO总线简析

五、网络驱动实验测试

1.LAN8720 PHY驱动测试

2.通用PHY驱动测试

3.DHCP功能配置

六、单网卡使用

1.只使用ENET2网卡

2.只使用ENET1网卡

本笔记为参考正点原子开发板配套教程整理而得,仅用于学习交流使用,不得用于商业用途

6565

6565

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?