目录

(2)SRAM(常用作Cache)、DRAM(常用作主存)的工作原理。

本章总览

一、存储器的简单模型及寻址概念。

(1)存储器芯片的基本结构。

(2)寻址概念、本节总结。

二、半导体存储器。

(1)半导体存储芯片的基本结构。

(2)SRAM(常用作Cache)、DRAM(常用作主存)的工作原理。

SRAM(静态随机存取存储器)、DRAM(动态随机存取存储器)的对比

同步动态随机存取存储器(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。

DRAM的刷新

选通线:行列地址可以减少选通线数量(相比->采用一根线选通一个存储单元)。

SRAM的读写周期

CS表示片选线,上面有“—”的表示低电平有效。

最上面的地址对应的三个二进制数字(有未访问,访问中,已访问的地址),是表示访问的地址。

最下面的数据Dout表示的是数据,那个二进制数据就是访问地址中的数据。

过程分析:地址传过来,地址信号开始有效,过了一会,CS打开开关,开始通过地址来读取数据,有了数据,数据信号开始有效,一会数据稳定后,CS开关关闭,读取数据结束,再过一会,地址信号失效。开始下一次操作。

存取时间:存储器从接收到读写命令到信息被读出或写出所需要的时间。

存取周期:存储器连续读写过程中一次完整的存取操作所需的时间,即CPU连续两次访问存储器的最小时间间隔。

存取周期 = 存取时间 + 恢复时间

恢复时间:CPU每次访问完存储器,有一段时间内CPU不能再次访问存储器,存储器要过一段时间才能再次被访问,这段时间即称为恢复时间,保证存储器数据的准确性)

RAM-易失性存储器

(3)ROM的特点和基本类型。

(4)存储器的分类

(5)存储器性能指标和层次化结构。

(6)本节回顾。

三、主存与CPU的连接。

(1)主存容量扩展-位扩展。

(2)主存容量扩展-字扩展。

(3)主存容量扩展-译码器。

(4)主存容量扩展-字扩展。(译码器使用)

(5)主存容量扩展-字位同时扩展。

(6)本节回顾。

四、主存与CPU的连接的例题。

系统程序工作区和用户程序区都是RAM,系统程序区是ROM

系统程序工作区需要读出和写入程序,选用ram,不能使用rom(只读存储器)

五、双端口RAM和多模块存储器。

(1)双端口RAM

定义:双端口存储器是指同一个存储器具有两组相互独立的读写控制线路,由于进行并行的独立操作,是一种高速工作的存储器,每一个端口都有自己的片选控制和输出驱动控制。

工作原理:当两个端口的地址不相同时,在两个端口上进行读写操作,一定不会发生冲突。

读写控制当两个端口同时存取存储器同一存储单元时,便发生读写冲突。

为解决此问题,特设置了BUSY标志。(由片上的判断逻辑决定对哪个端口优先进行读写操作,而暂时关闭另一个被延迟的端口。)

(2)多模块存储器。

单体多字存储器:

在一个存取周期内,从同一地址取出n条指令,然后逐条将指令送至CPU执行,即每隔1/n存取周期,主存向CPU送一条指令,增大了存储器的带宽,提高了存储器的工作速度。

例如:从同一地址取出4条指令,为单体四字结构,每字W位。按地址在一个存取周期内可读出4*W位的指令或数据,使主存带宽提高到4倍。

缺点:指令和数据在主存内必须是连续存放的,一旦遇到转移指令,或者操作数不能连续存放,这种方法的效果就不明显。

多行并行存储器:

①低位交叉编址:程序连续存放在相邻体中(交叉存储)。低位地址表示体号,高位地址表示体内地址。

优点:相邻地址单元的数据放在不同组,各组可以并行工作,能较好提高存储器的带宽。

缺点:某一组出现故障,会影响整个存储器的正常工作。

②高位交叉编址:按体内地址顺序存放(顺序存储)。高位地址表示体号,低位地址表示体内地址。

优点: 某一组的故障不影响其他组,且容易通过添加模块来扩充容量。

缺点:相邻地址单元的数据放在同一组存储单元,各组间串行工作,不利于提升存储器的带宽。

(3)本节回顾。

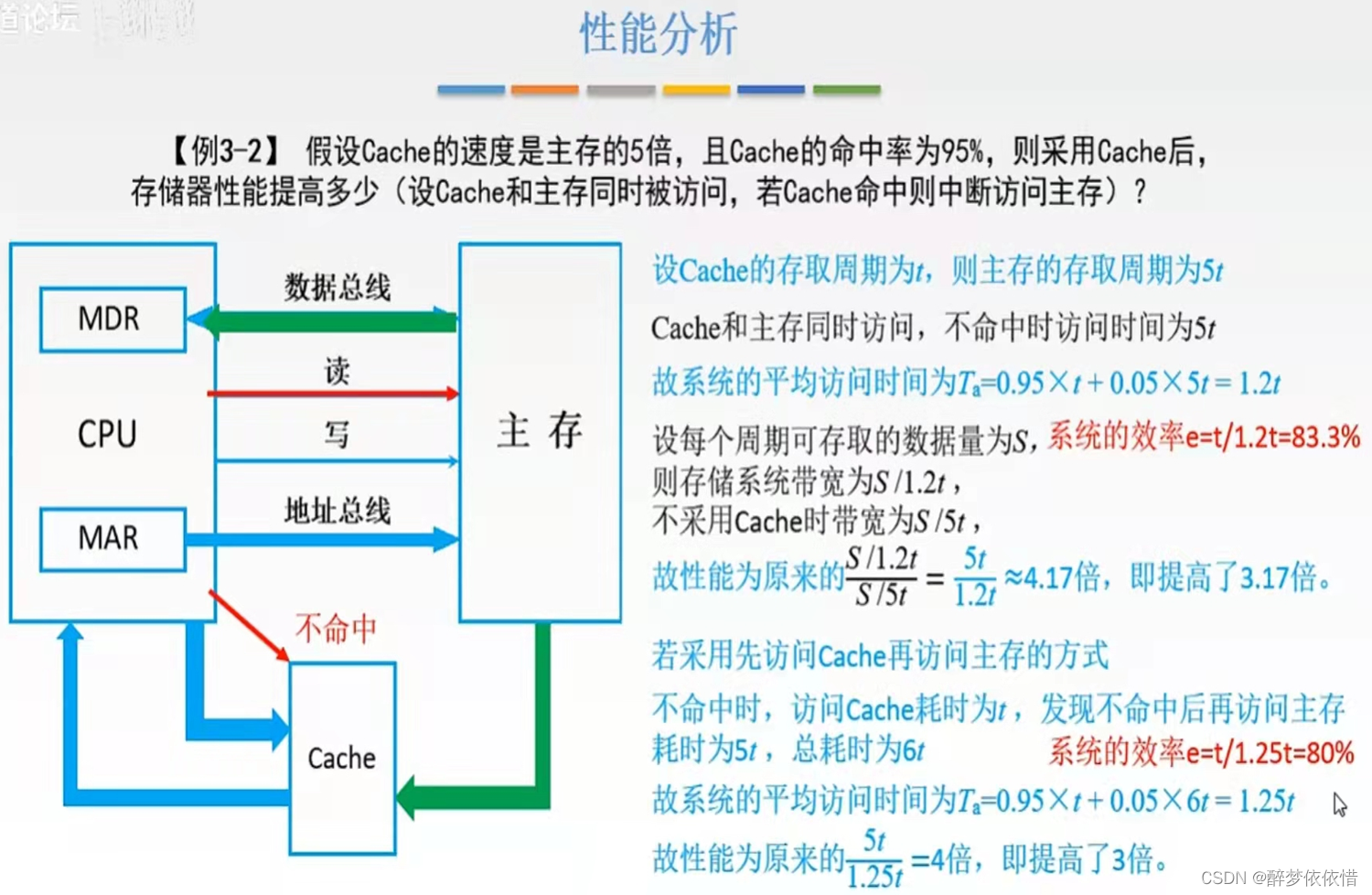

六、高速缓冲存储器。

(1)空间局部性、时间局部性。

(2)地址映射方式。

全相联映射、直接映射、组相联映射

(3)替换算法。

(4)写策略。

(5)cache例题。

(6)cache原理。

七、虚拟存储器。

页式、段式、段页式。慢表、块表。

原理:当进程开始运行时,先将一部分程序装入内存,另一部分暂时留在外存;当要执行的指令不在内存时,由系统自动完成将它们从外存调入内存的工作;当没有足够的内存空间时,系统自动选择部分内存空间,将其中原有的内容交换到磁盘上,并释放这些内存空间供其他进程使用。

页式虚拟存储器:以页为单位的虚拟存储器称为页式虚拟存储器。虚拟空间和主存空间都被划分为同样大小的页,主存的页称为实页,虚存的页称为虚页。

把虚拟地址分为两个字段:虚页号和页内地址。

页表是一张存放在主存中的虚页号和实页号的对照表,记录着程序的虚页调入主存时被安排在主存中的位置。

页表基址寄存器存放当前运行程序的页表的起始地址。

288

288

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?