计算机的诞生与发展:

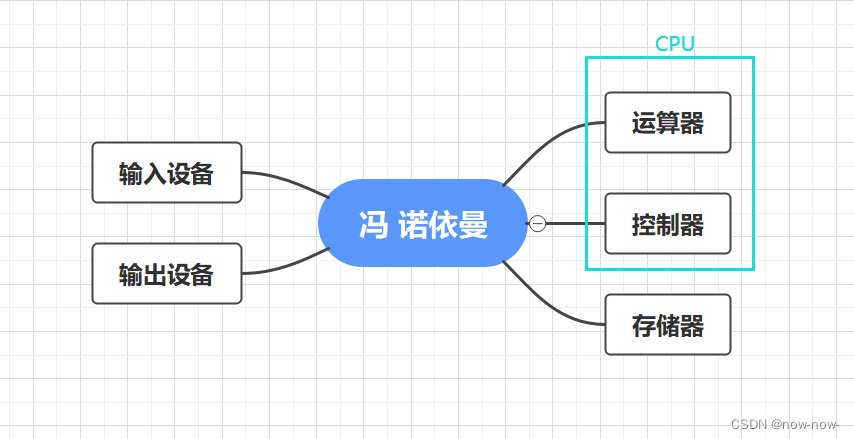

冯 诺伊曼体系:EDVAC(Electronic discrete variable automatic computer)

冯诺依曼机的特点:

1.计算机由运算器,控制器,存储器,输入,输出设备五大部件组成

2.指令和数据以同等地位存放于存储器内,并可按地址寻访

3.指令和数据均用二进制表示

4.指令由操作码和地址码组成

5.指令在存储器中按顺序存放

6.机器以运算器为中心

第一台严格意义上的电子数字计算机-ENVIC(Electronic Numrical intergrator and computer)

电子管时代

晶体管计算机

中小规模集成电路计算机

大规模和超大规模集成电路计算机

计算机的主要性能指标:

1.外频:外部频率或基频,系统时钟频率-主板上振荡器输出的时钟频率

2.CPU主频:CPU的内核工作频率,=外频*倍频系数;决定计算机工作速度的重要因素,GHz。

3.IPS:CPU平均每秒执行的指令条数(instruction per second),也用MIPS或GIPS表示

4.CPI:CPU平均执行每条指令的时钟周期数(Clock cycles per instructions )

数据:

数据:数值型数据--进制表示法;定点数和浮点数

字符型数据--ASCII

数据的运算--原码和补码

CPU:

1.基本组成:

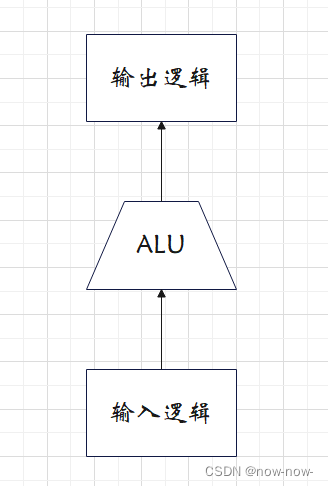

运算器:ALU算数逻辑单元,ACC累加器,MQ乘商存储器,X操作数存储器

控制器:程序计数器PC,指令寄存器IR,控制单元CU

a.运算部件:

ALU:Arithmetic Logic Unit ;主要部件是一个加法器,进行加法操作时有可能产生进位,所以它还具有提供进位信号的传递逻辑(进位链)

b.寄存器组:

通用寄存器:一组可用过程序访问的寄存器,在指令系统中为其分配了编号。没有特定分工,可用于存储各类信息,简单命名为:R0,R1,R2等,早期用D触发器构成寄存器组,小规模集成电路;现在广泛采用中规模基础的RAM构成寄存器组。

暂存器:不能被编程访问,只能在CPU工作时内部专用。

指令暂存器:IR;将其扩充为指令队列(指令栈)。

程序计数器:Program Counter;指令计数器或指令指针。

程序状态字寄存器:Program Statue Words

特征位:

进位位C

溢出位V:

c.控制器:对指令进行译码。(控制信号-指令/数据)

d.内部数据通路结构:

e.时序系统:周期,节拍,脉冲-时序信号,产生时序信号的不见位时序发生器,由一个晶体振荡器(一般位于主板上)和一组计数倍频逻辑组成,能输出频率稳定的基准时钟脉冲,即外频。

2.工作原理:

3.指令集类型

每款CPU在设计之前就定义好了一系列与其硬件电路相适应的指令系统,如指令的格式,类型,数量,寻址方式等;它关系到了计算机系统的硬件结构和基本的硬件功能,是CPU的一个重要指标。

CISC(Complicated Instructionc Set Computer)

指令系统庞大,指令功能复杂,格式多变,寻址方式很多;约有20%的指令高频使用(占程序的80%),另外80%较少使用(占程序的20%)--”指令二-八定律”。

RISC (Reduced Instructionc Set Computer)

指令格式统一,种类少且寻址方法简单,增加了CPU的并行处理能力,处理速度提高很多,更适合高档服务器的操作系统,如window7/8和Linux。

4.发展历程:

指令系统:

A指令格式:一条指令通常包含以下信息:操作码(OP),地址信息(A)

1.地址结构-一条指令中可能包含几个地址码,显地址是指指令中写明地址码,一条指令中给出几个显地址就成为几地址指令;隐地址-在指令中不给出地址码,简化地址结构。

三地址指令: A1(OP)A2->A3

(PC)+n->PC PC-程序计数器

二地址指令: A1(OP)A2->A1

一地址指令: OP(A)->A

零地址指令:a.不需要操作数的指令,达到延时的目的;

b.OP(AC)->AC 隐含约定操作数在AC累加器中

2.操作码结构

3.指令字长

B寻址方式

C指令类型

5.CPU性能的提升技术:

第一方面:CPU的设计技术-流水线,多核,SMT,

流水线

SMT与HT

多核技术

第二方面:CPU的制造工艺技术

第三方面:CPU的散热技术

经典处理器的介绍:

Intel 8086/8088

Intel 80386/80486

Pentium微处理器

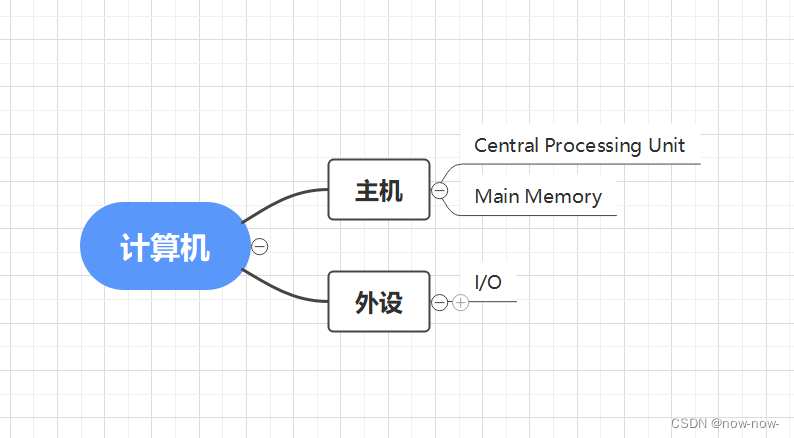

存储系统:

主存储器:

主存包括存储体M,存储器地址寄存器MAR,存储器数据寄存器MDR。

存储体-一串 存储字 位数为存储字长

存储单元-一位

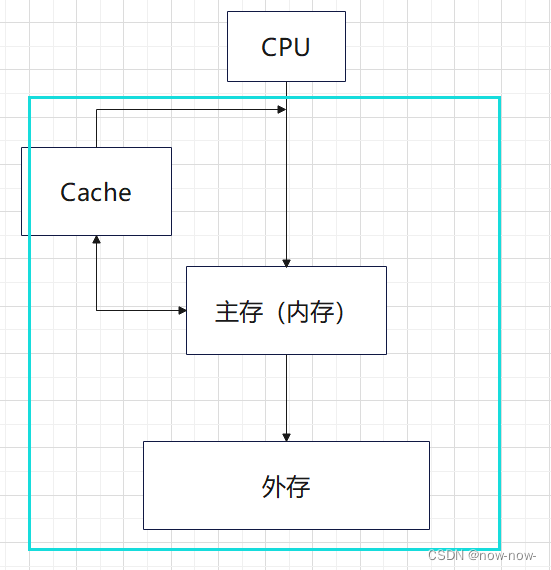

主存是CPU直接访问的存储器,常称为内存。将当前即将运行的程序和数据调入主存,其他暂时不运行的程序和数据放入磁盘等外部存储器中。同时,程序和数据只有进入到主存中才能被运行,而位于外部储存器的则不能被运行。CPU可按照字或字节访问,处理主存。

一般用DRAM(动态随机存储器)组成,除此之外计算机系统中还有少量用来保存固化程序和数据的只读存储器(ROM),这些只读存储器由EPROM,FLASH来充当。

外存储器:

可将频繁调用的文件放入磁盘中,作为主存的直接后援;不太频繁调用的放入u盘或移动硬盘内,构成“主-辅”外部存储体系。

为了提高光盘,磁盘的相应速度,通常会在主存和外存之间添加有高速半导体存储器构成的缓冲存储器。

用户编程往往按照文件名体哦啊用,以文件为一次调用的单位。但在物理存储结构中,常将一个文件分为若干数据块。

高速缓冲存储器:

Cache作为存储子系统的一部分,主要是为了缓解CPU与主存速率不匹配问题,通常由存取速度较高的静态随机访问存储器(SRAM)构成。

Cache中存放的是CPU最近要使用的程序和数据,作为主存中当前活跃信息的副本。

读写方式:

1.可读可写型

2.只读型

存取方式:

1.随机访问存储器(Random Access Memory)

2.顺序访问存储器(Sequential Access Memory)

3.直接访问存储器(Direct Access Memory)

存储器的分类:

1.半导体存储器

2.磁表面存储器

3.光盘存储器

存储器的技术指标:

1.存取时间

存:信息存入存储器-写;取:从存储器中取出存储器-读,两者统称为“访问”。从存储器接收到命令到做出操作成为存取时间,Ta,一般为ns级(纳秒)

2.存取周期

Tm=Ta+复原时间。是一个反应储存器性能的重要参数,常被标记在芯片上,‘-7,-15’分别表示7ns,15ns。数值越小存取速率越高。

3.数据传输率

Date Transfer Rate-DTR;

R=W/Tm(单位为KB/s或MB/s)W为一次读写数据的位数b

I/O设备:

计算机所能处理的信息为电信号形式的数字代码(0,1),输入设备将各种原始信息(数字,字符,声音,图形,文字等)转变为计算机能够识别处理的信息形式,并输入计算机;输出设备将电信号转变成人类或其他系统能够识别的信息,并向外输出。

一般用户的外设成本占到整个计算机系统的50%,而约有80%的故障出在外设上。外设的种类繁多,且构成和工作原理差别甚大。

信息交换:I/O设备与主机之间的信息输入或输出

1.代码格式--ASCII

2.传输格式 a.并行传输-同时用多根传输线,并行的传输一个字节或一个字。传输速率高,相应的硬件代价高,一般用于传输距离近且速率要求高的设备

b.串行传输--速率低,代价低

3.传输速率 bit/s或b/s,启动位是一个单位的低电平,之后为8个位单元,可传输8位代码,停止位为1.5个单位的高电平

常用外设

A.键盘

有触点式,无触点式,虚拟式

虚拟激光键盘(Virtual Laser Keyboard)

B.显示器

显示器(Display Monitor)也叫监视器。显示设备子系统的硬件组成一般包括显示器件(显示器),控制器和接口。后两者通常合为一个整体--显示器适配卡;软件组成包含操作系统中的驱动程序。

分辨率:是指显示器单屏能表示的像素个数,个数越多,越清晰,分辨率越大。

灰度级:黑白显示器中表示为像素点的亮暗差别,彩色显示器中表现为颜色的不同,灰度级越大,图像层次越清楚逼真。

刷新频率:单位Hz,一般刷新频率大于25时,人眼不会感到闪烁。

显存:为了不断刷新图像,每一帧图像对应的数据信息储存在特殊的存储器中-显示存储器,简称显存(VRAM),由随机存储器构成。显存一般占用部分主存空间,在带有独立显卡的显示终端中,显存作为外设存在,与主存分离。目前广泛应用有DDR2,DDR3或更高级的GDDR5。

总线:

总线控制器:判优控制(集中式,分布式)和通信控制

集中式:

链式查询 ( BG总线同意, BR总线请求, BS总线忙 )离总线最近的设备优先级最高,需要很少的线就可以按一定优先次序实现总线控制,易扩充设备,但对故障很敏感,且优先级低

计数器定时查询 与前者相比多了一组设备地址线

独立请求方式

635

635

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?