CPU两大基本组成部件:数据通路、控制器。

数据通路中执行部件专用于数据运算

指令执行用到的两类元件:组合逻辑元件(操作元件)、存储单元(状态元件)

操作元件如:多路选择器MUX、加法器Adder、算术逻辑部件ALU

状态元件如:通用寄存器、暂存寄存器。

现在的计算机已经没有机器周期。只考虑时钟周期

通用寄存器是可编程指定多种功能的寄存器。用于存放操作数和各种地址信息等,位数与机器字长相等,便于操作控制。

条件转移指令执行时所依据的条件来自标志寄存器,对标志寄存器的内容测试,判断是否满足转移条件。

数据总线的位数与处理器的位数相同,表示CPU一次能处理的数据的位数。

间址周期:取操作数的有效地址,间址周期结束后MDR中的内容为操作数地址。

PC程序计数器和IR指令寄存器位数

PC位数看有多少种指令

IR位数看指令字长多少

题目: 一台32位计算机的主存储器容量为4GB,按字节编址,存储字长和指令字长都是32位。若指令按字边界对齐存放,则程序计数器PC的宽度至少:

答案:指令字长32位-->4B,一共4GB/4B=2^32/2^2=2^30种指令,可以用30位地址表示指令地址,所以PC宽度至少30位。

题目:某计算机的主存储器空间为4GB,字长为32位,按字节编址,采用32位字长指令格式。若指令按字边界对齐存放,则程序计数器PC和指令寄存器IR的位数至少分别为:

答案:32位4字节,一个指令4B,4GB可以有2^30条指令,可以用30位地址表示指令地址,PC至少30位。

IR存指令,指令字长32位,所以IR32位。

取值后PC+‘1’,指向下一条指令的地址,1是一个指令长度

指令字长是存储字长的整数倍,方便硬件设计;指令字长与机器字长没有关系。

CPU区分指令和数据的依据是指令周期的不同阶段。

主存通过总线的类型来识别信息是地址还是数据。

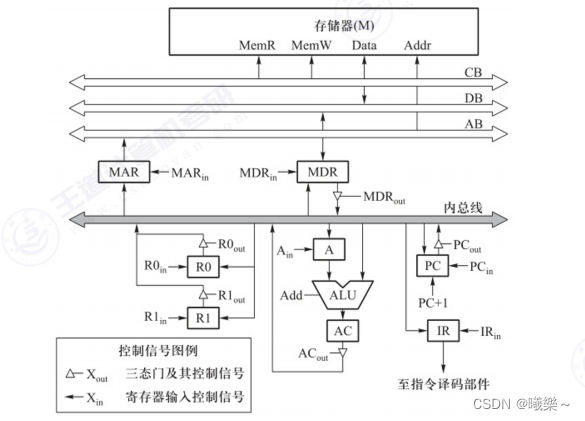

总线连接CPU内部电路:每个时刻只有一个器件发出信息(否则总线冲突),但每个时刻可以有一个或多个器件接收信息。

CPU内部总线方式特点:结构简单,实现容易,性能较低,较多冲突;

不采用CPU内部总线方式的数据通路的特点:结构复杂,硬件量答,不易实现,性能高,基本没冲突。

取指令流程数据通路和控制信号

(PC)-->MAR 找地址

M(MAR)-->MDR 访存找数据

M(MDR)-->IR 主存数据给IR译码

(PC)+1-->PC IP自加一

一个访存独占一个节拍;

使用总线不同也可以在一个节拍,如使用内部总线和使用存储器总线可以在一个节拍。

PC自动加1

对指令R[R1]<--R[R1]+M[R0]

RO数据传给MAR,

MAR访存得到M[RO]放入MDRR1数据传给A,

MDR数据传给ALU

计算MDR+A生成AC

AC数据传给R1

| 时钟 | 微操作 | 控制信号 |

| C1 | MAR<--(RO) | ROout,MARin |

| C2 | MDR<--M (MDR),A<--(R1) | MemR, Rlout, Ain |

| C3 | AC<--(A)+(MDR) | MDRout, ADD |

| C4 | R1<--(AC) | Rlin, ACout |

一条微指令存放在控制器的一个控制存储器单元中

确定下一条微指令地址采用断定方式:通过微指令后继地址字段由设计者指定或转移控制字段控制产生后继微指令地址。

硬布线控制系统要结合各个微操作的节拍安排的时序系统复杂,微程序按照节拍安排顺序执行,比较简单。

时钟周期以相邻状态单元间组合逻辑电路的最大延迟为基准确定。

流水线CPU只有在理想情况下才能实现每个时钟周期执行一条新指令。

汇编程序员可见的寄存器:基址寄存器、状态/标志寄存器,PC,通用寄存器

流水CPU经济且实用。

RISC一定用流水线CPU。

RISC指令长度一致,按边界对齐存放,仅load/store指令访存。

指令译码得到的控制型号需要通过流水寄存器传递到下一个流水线。

时钟信号在各种状态元件上都用。

转发(旁路)技术不能解决load-use数据冒险

看是否发生数据冒险:把每条指令的几个阶段作用写出来,按指令执行过程图画,看是否有冲突

按序流动的流水线只可能出现RAW相关(先写后读)

多核处理器是在一个CPU上集成了多个执行内核。

可以一核多线程。

多核CPU上执行不支持多线程的程序不能发挥多核的作用。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?