1.锁存器/触发器(数电书上讲了)

门电路由晶体管组成;锁存器由门电路组成;触发器由锁存器组成;寄存器由触发器组成;

例如边沿触发的D触发器由两个电平触发的D触发器(也称为D型锁存器)组成。

优缺点比较摘抄别人的:

锁存器优点:

1、面积比ff小

门电路是构建组合逻辑电路的基础,而锁存器和触发器是构建时序逻辑电路的基础。门电路是由晶体管构成的,锁存器是由门电路构成的,而触发器是由锁存器构成的。也就是晶体管-》门电路-》锁存器-》触发器,前一级是后一级的基础。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

2、速度比ff快

用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。

锁存器缺点:

1、电平触发,非同步设计,受布线延迟影响较大,很难保证输出没有毛刺产生

2、latch将静态时序分析变得极为复杂

触发器优点:

1、边沿触发,同步设计,不容易受毛刺的印象

2、时序分析简单

触发器缺点:

1、面积比latch大,消耗的门电路比latch多

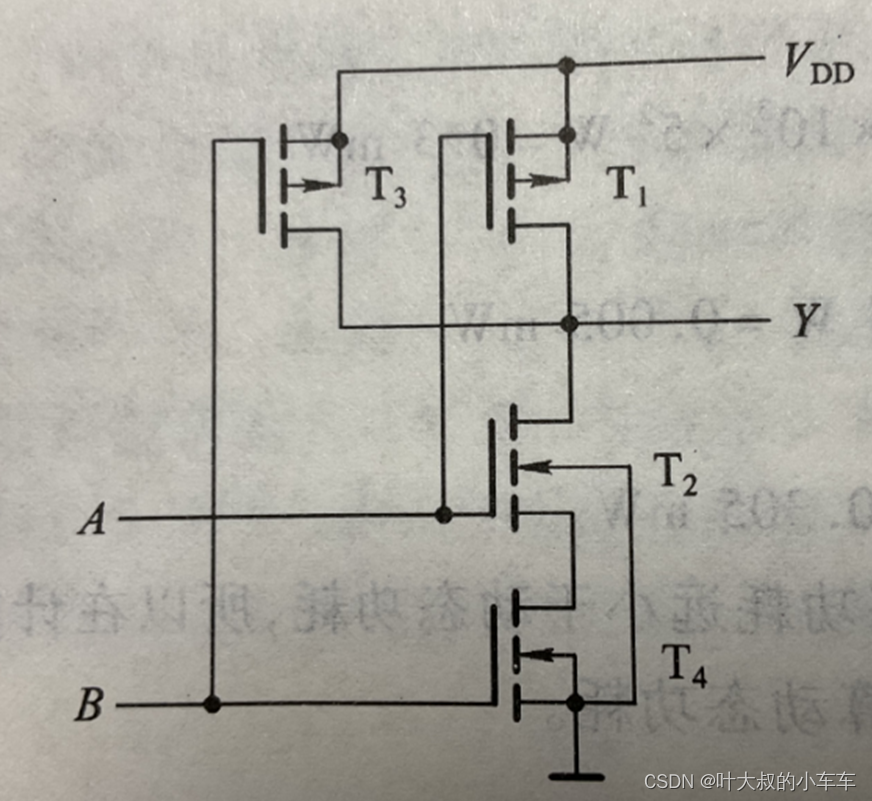

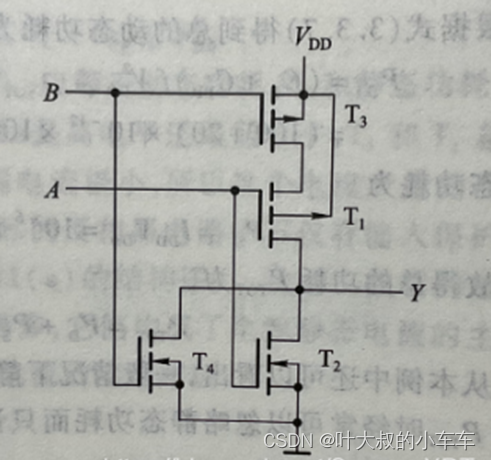

2.与非门/或非门用cmos搭建

与非门:两个并联的p沟道增强型mos管和两个串联的n沟道增强型mos。

或非门:两个串联的p沟道增强型mos和两个并联的n沟道增强型mos管。

3.组合逻辑电路容易产生毛刺

组合逻辑电路各个输入信号的不一致性以及组合逻辑内部路径的延时时间不一样,运算后的信号存在毛刺。

要想采样到稳定的信号,必须要经过触发器敲一下,保证在一个时钟周期内是稳定的信号。

跨时钟域传输的时候,时钟域B的两级同步的寄存器跟时钟域A的输出寄存器之间不能有组合逻辑。否则必须在组合逻辑之后再用一个触发器,用CLKA 敲过,才能保证在一个时钟周期内是稳定的信号。

消除毛刺:

- 调整逻辑路径: 使得信号传播路径的延迟尽可能一致。

- 使用同步时钟: 在组合逻辑之后使用触发器或寄存器同步信号,消除短暂的毛刺对时序电路的影响。

- 引入滤波电路: 使用RC滤波器等技术来消除高频的毛刺信号。

441

441

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?