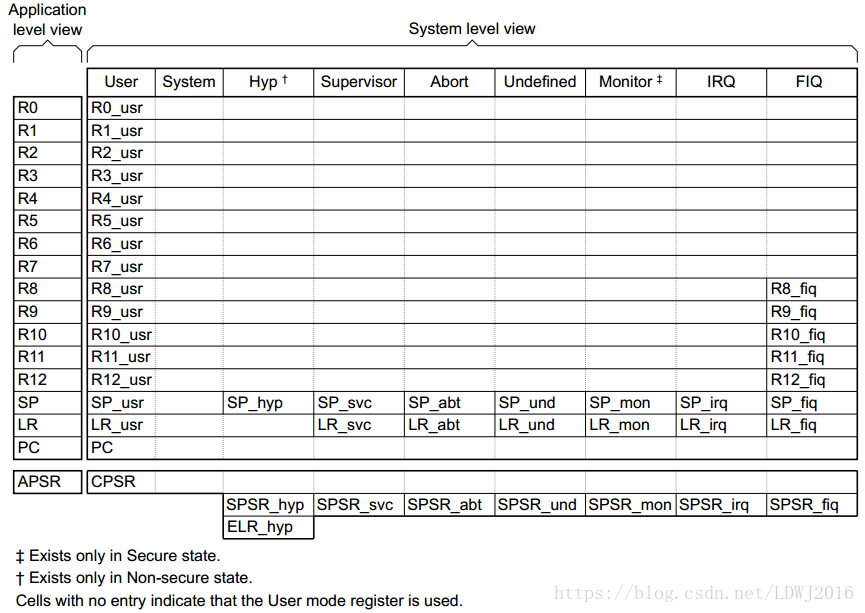

Arm processors provide general-purpose and special-purpose registers. Some additional registers are

available in privileged execution modes.

In all Arm processors in AArch32 state, the following registers are available and accessible in any processor mode:

• 15 general-purpose registers R0-R12, the Stack Pointer (SP), and Link Register (LR).

• 1 Program Counter (PC).

• 1 Application Program Status Register (APSR).

------------------------------ Note ------------------------------

• SP and LR can be used as general-purpose registers, although Arm deprecates using SP other than as

a stack pointer.

--------------------------------------------------------------------

Additional registers are available in privileged software execution. Arm processors have a total of 43

registers. The registers are arranged in partially overlapping banks. There is a different register bank for

each processor mode. The banked registers give rapid context switching for dealing with processor

exceptions and privileged operations.

The additional registers in Arm processors are:

• 2 supervisor mode registers for banked SP and LR.

• 2 abort mode registers for banked SP and LR.

• 2 undefined mode registers for banked SP and LR.

• 2 interrupt mode registers for banked SP and LR.

• 7 FIQ mode registers for banked R8-R12, SP and LR.

• 2 monitor mode registers for banked SP and LR.

• 1 Hyp mode register for banked SP.

• 7 Saved Program Status Register (SPSRs), one for each exception mode.

• 1 Hyp mode register for ELR_Hyp to store the preferred return address from Hyp mode.

--------------------------- Note -----------------------------

In privileged software execution, CPSR is an alias for APSR and gives access to additional bits.

-----------------------------------------------------------------.

The following figure shows how the registers are banked in the Arm architecture.

Figure 3-1 Organization of general-purpose registers and Program Status Registers

In Armv6‑M, Armv7‑M, Armv8‑M Baseline, and Armv8‑M Mainline based processors, SP is an alias

for the two banked stack pointer registers:

• Main stack pointer register, that is only available in privileged software execution.

• Process stack pointer register.

1464

1464

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?