用6410驱动TD043的Panel,按规格书写入屏参数。画面始终会有从上至下的闪动,触摸屏触摸拉动屏幕时还会有类似网络电影卡死的蹦蹦画面,分析是丢了很多帧数据。用示波器测试,果然是场频极低,DCLK也极低,造成的刷新率不够。从写入CLOCK的芯片寄存器开始找原因,因为这是控制Panel的最后一步:

1,配屏:按照PANEL的规格书将行场参数写入调用的屏参文件中。着重的有行场分辨率和DCLK。需注意的是:行和场所谓的Back Porch有的是包括Sync Width,有的是不包括,具体参见规格书。

2,DCLK是最重要的参数,可以通过示波器测试来判断跟最终PANEL所需的值是否一致。

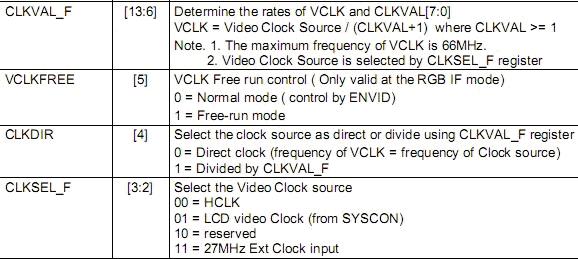

3,最终写入的DCLK是通过寄存器设置频率运算获得,vidcon0寄存器中[13:6] ,从打印信息知该寄存器值0X1D4。代码之前的错误在于程序逻辑错误,没有对vidcon0的以上若干位进行清零,以致后来做或运算时出现的未知值,导致分频参数错误。

要在:s3c_fimd.vidcon0 |= S3C_VIDCON0_CLKVAL_F((int)(((((clk_get_rate(lcd_clock) * 10) / (1*s3c_fimd.pixclock)) % 10) > 4) ? (clk_get_rate(lcd_clock) / (1*s3c_fimd.pixclock)) :((clk_get_rate(lcd_clock) / (1*s3c_fimd.pixclock)) - 1)));

前添加:s3c_fimd.vidcon0 &=~(0x000000ff <<6);

如上: clk_get_rate(lcd_clock)的值是266000000,根据屏规格书运算的PANEL的pixel clock是33264000。266000000/ 33264000= 7.9,所以最终输出给PANEL的clock是266/8=33.25M。

4,补充说明:以上区分四舍五入的原因是:寄存器内部对频率系数还要加1。比如CLKVAL是7.9的话,已经接近于8,那么需要7+1才是最接近真实值。如果是7.2的话,需6+1才接近于7,所以要减1。

=============================================================

对于有的PANEL,它有两种工作模式,一种HSVS(行场同步),另一种DE(DATA ENABLE)。这两种模式工作的采样方式不同,后一种理解成:data enable信号完全可以当作HS信号,其中的间隔差异又可以当作VS信号。

6578

6578

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?