ARM920T clocking

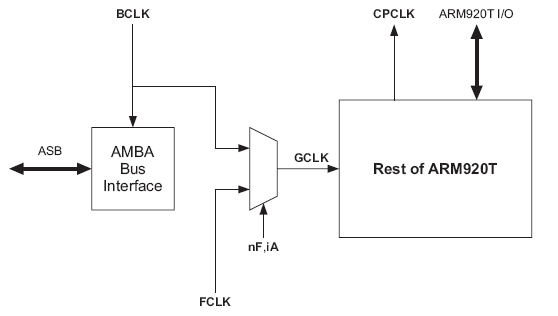

The ARM920T has two functional clock inputs, BCLK and FCLK. Internally, the ARM920T is clocked by GCLK,which can be seen on the CPCLK output as shown in Figure 5-1.GCLK can be sourced from either BCLK or FCLK depending on the clocking mode, selected using nF bit and iA bit in CP15 register 1 (see Register 1: Control register on page 2-12),and external memory access.The three clocking modes are FastBus, synchronous and asynchronous.

ARM920T有2个时钟输入,分别是BCLK和FCLK。从图5-1中GPCLK的输出可以看出,ARM920T内部是由GCLK时钟模式驱动。CP15寄存器1(参见寄存器1:控制寄存器,2-12页)的nF位和iA位决定时钟模式,即决定了GCLK是由FCLK还是BCLK产生。一共有3种时钟模式,分别为快速总线、同步以及异步模式。

The ARM920T is a static design and both clocks can be stopped indefinitely without loss of state. From Figure 5-1 it can be seen that some of the ARM920T macrocell signals will have timing specified with relation to GCLK, which can be either FCLK or BCLK depending on the clocking mode

ARM920T的设计是固定的,两种时钟都可以被无期限的暂停,而不会导致状态丢失。从图5-1这可以看出,有些ARM92的macrocell信号的timing受到GCLK的影响,而GCLK具体是由FCLK是还是BCLK产生,则是由时钟模式决定。

FASTBUS MODE

快速总线模式

In FastBus mode GCLK is sourced from BCLK. The FCLK input is ignored. This

means that BCLK is used to control the AMBA ASB interface and the internal

ARM920T processor core.

On reset, the ARM920T is put into FastBus mode and operates using BCLK. A typical

use for FastBus mode is to execute startup code while configuring a PLL under software

control to produce FCLK at a higher frequency. When the PLL has stabilized and

locked, you can switch the ARM920T to synchronous or asynchronous clocking using

FCLK for normal operation.

在快速总线模式,GCLK来自于BCLK,FCLK输入被忽略。这意味着BCLK被用来控制AMBA ASB接口和内部的ARM920T处理器核。复位时,ARM920T进入快速总线模式,操作使用BCLK。一般快速总线模式在启动代码时执行,然后由软件配置PLL产生高频的FCLK。在PLL稳定后可以切换ARM920T到同步或异步时钟,使用FCLK进行操作。

小结:

- GCLK=BCLK,FCLK被忽略

- 板子reset之后即进入该模式

- 该模式的典型应用是执行启动代码,同时软件配置PLL,使得FCLK更高

- nF=0且iA=0

SYNCHRONOUS MODE

同步模式

In this mode of operation GCLK is sourced from BCLK or FCLK. There are three

restrictions that apply to BCLK and FCLK:

• FCLK must have a higher frequency than BCLK

• FCLK must be an integer multiple of the BCLK frequency

• FCLK must be HIGH whenever there is a BCLK transition.

在这个操作模式GCLK来自于BCLK或FCLK。但是对于BCLK和FCLK要满足3个条件:

1. FCLK必须比BCLK有更高的频率

2. FCLK必须是BCLK频率的整数倍数

3. 无论BCLK怎么转换,FCLK的频率都要高于BCLK

BCLK is used to control the AMBA ASB interface, and FCLK is used to control the

internal ARM920T processor core. When an external memory access is required the

core either continues to clock using FCLK or is switched to BCLK, as shown in

Table 5-1. This is the same as for asynchronous mode.

BCLK被用来控制AMBA ASB总线接口,FCLK用来控制内部的ARM920T处理器核。

- 当访问外部存储地址时,处理器核心要么继续使用FCLK,要么切换到BCLK。见表1。

外部存储访问操作

GCLK=

写缓冲区

FCLK

写非缓冲区

BCLK

页搜寻、读缓冲(占满)、读非缓冲

BCLK

表1

The penalty in switching from FCLK to BCLK and from BCLK to FCLK is

symmetric, from zero to one phase of the clock to which the core is re-synchronizing.

That is, switching from FCLK to BCLK has a penalty of between zero and one BCLK

phase, and switching back from BCLK to FCLK has a penalty of between zero and one

FCLK phase.

从FCLK切换到BCLK与BCLK切换到FCLK的代价是相等的。需要耗费0~1个时钟周期使核重新同步。从FCLK切换到BCLK的代价是0~1个BCLK。从BCLK切换到FCLK的代价是0~1个FCLK。

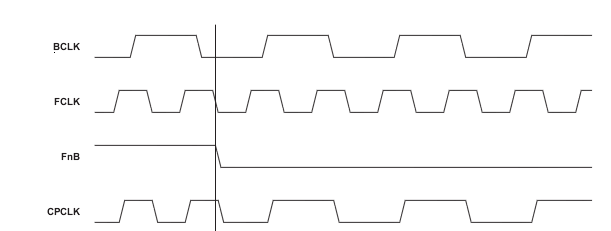

Figure 5-2 on page 5-5 shows an example zero BCLK phase delay when switching

from FCLK to BCLK in synchronous mode.

Figure 5-2 Synchronous mode FCLK to BCLK zero phase delay

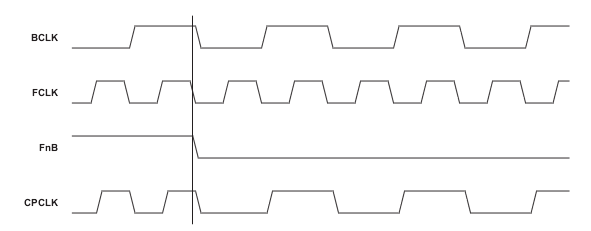

Figure 5-3 shows an example one BCLK phase delay when switching from FCLK to

BCLK in synchronous mode.

Figure 5-3 Synchronous mode FCLK to BCLK one phase delay

小结:

- GCLK=BCLK或者GCLK=FCLK

- FCLK=n*BCLK(n大于1且为整数)

- BCLK用于控制AMBA ASB接口,而FCLK用来控制内部的ARM920T处理器核心。当访问外部存储地址时,处理器核心要么继续使用FCLK,要么切换到BCLK。见表1。

- nF=1且iA=0

Asynchronous mode

异步模式

In this mode of operation GCLK is sourced from BCLK or FCLK. FCLK and BCLK

can be completely asynchronous to one another, with the one restriction that FCLK

must have a higher frequency than BCLK.

BCLK is used to control the AMBA ASB interface, and FCLK is used to control the

internal ARM920T processor core. When an external memory access is required the

core either continues to clock using FCLK or is switched to BCLK. This is the same

as for synchronous mode.The penalty in switching from FCLK to BCLK and from

BCLK to FCLK is symmetric, from zero to one cycle of the clock to which the core is

re-synchronizing. That is, switching from FCLK to BCLK has a penalty of between

zero and one BCLK cycle, and switching back from BCLK to FCLK has a penalty of

between zero and one FCLK cycle.

在这个操作模式GCLK来自于BCLK或FCLK。FCLK和BCLK之间可以完全异步,只有一个要满足的条件是FCLK的频率要高于BCLK。BCLK被用来控制AMBA ASB总线接口,FCLK用来控制内部的ARM920T处理器核。与同步模式时相同,从FCLK切换到BCLK与BCLK切换到FCLK的代价是相等的。需要耗费0~1个时钟周期使核重新同步。从FCLK切换到BCLK的代价是0~1个BCLK。从BCLK切换到FCLK的代价是0~1个FCLK。

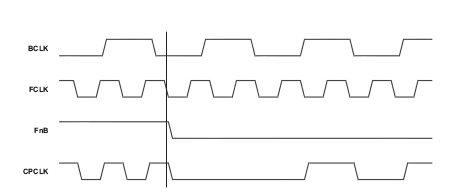

Figure 5-4 shows an example zero BCLK cycle delay when switching from FCLK to

BCLK in asynchronous mode.

Figure 5-4 Asynchronous mode FCLK to BCLK zero cycle delay

Figure 5-5 on page 5-7 shows an example one BCLK cycle delay when switching from

FCLK to BCLK in asynchronous mode.

Figure 5-5 Asynchronous mode FCLK to BCLK one cycle delay

小结:

- GCLK=BCLK或者GCLK=FCLK

- BCLK用于控制AMBA ASB接口,而FCLK用来控制内部ARM920T处理器核心。当访问外部存储地址时,处理器核心要么继续使用FCLK,要么切换到BCLK。见表1。

- nF=1且iA=1

注:

- nF为P15的1号寄存器的第31位

- iA为P15的1号寄存器的第30位

参考资料:

ARM920T手册

http://blog.csdn.net/jerry1089/archive/2009/10/17/4689246.aspx

http://blog.csdn.net/woshixingaaa/archive/2011/03/16/6252337.aspx

http://hi.baidu.com/yk103/blog/item/04849916ca803b52f2de3279.html

1509

1509

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?