最近公司要用到Atsha204a做软件和硬件的绑定加密,于是就调了它的驱动,将使用过程中遇到的坑整理下,也好让各位同仁少加点班;废话少说,直接入正题。

0.加密原理:

主控端和Atsha204a端有相同的16 组密码,用一串明文(一般生成一组32byte随机数),主控端用约定的一组密码使用sha256()加密算法将明文生成Hash值(32 byte),同时主控将明文传递给Atsha204a端,用与主控约定好的一组(SlotNum)密码内部生成sha256 Hash值。然后主控读取Atsha204a生成的hash,与自身生成的hash进行对比,若相同则成功。

注意:通讯线路中(iic)不传递密码,Atsha204a端密码区先烧录好16组密码(根据配置,密码可以设置不可读,就算出来的,也是0xff),只传递加密前的明文和约定密码的组号即可。

1.往Atsha204a里写密钥:

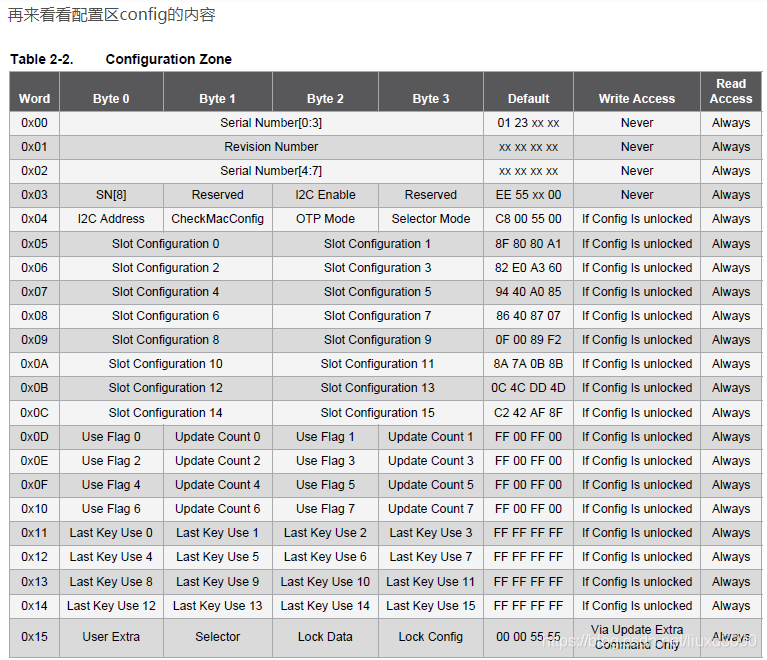

1.1 配置 config zone:

主要是16组密码的属性(如是否明文显示,是否可读,是否可写),如下的几个配置:

int8_t data1[4]={0x80,0x80,0x80,0x80}; //data锁定后不可读,也不可写

uint8_t data2[4]={0x80,0x00,0x80,0x00}; //

uint8_t data3[4]={0x00,0x00,0x00,0x00};//data锁定可明文读,也可写

uint8_t data4[4]={0xC0,0x80,0xC0,0x80};//

uint8_t data5[4]={0xC0,0x00,0xC0,0x00};//

设备16组密码的属性:

Set_Zone_4byte(0,20,data1);

Set_Zone_4byte(0,24,data2);

Set_Zone_4byte(0,28,data3);

Set_Zone_4byte(0,32,data4);

Set_Zone_4byte(0,36,data5);

Set_Zone_4byte(0,40,data3);

Set_Zone_4byte(0,44,data3);

Set_Zone_4byte(0,48,data3);

1.2:lock config zone;一旦lock无法无法解锁;

Lock(0x80);

1.3: write opt zone(我的没有使用);

无

1.4: 确保2后可以进行 slot zone 密码区进行读写;

在zone 3写入16组密码(每组32byte)

1.5: lock slot zone;一旦lock无法无法解锁;

Lock(0x81);

6.操作完成,可以进入2的加密和验证操作。

2.加密和验证:

char ch;

static int slotNum = 0;

unsigned char recBuf[35]={0}; //接收ATSHA204计算结果

unsigned char randomNum[35]={0}; //随机数BUF

CATsha204(); //定义一个类

ch = GenerateRandomNum(randomNum); //产生随机数

if(ch != 0){

printk("==atsha204 iic com failed,exit==\n");

return -1;

}

printk("slotNum =%d\n",slotNum);

if(check_lock() != 1){

printk("\n this is a new atsha204,will fac_lock_atsha204\n");

//fac_lock_atsha204();

}

ch=Mac(slotNum,randomNum+1,recBuf); //进行密码验证

if(ch)

{

printk("-------------mac ok---------------\n");

}

else

{

printk("-------------mac fail---------------\n");

}

slotNum++;

if(slotNum >=16)

slotNum = 0;

return 0;

2379

2379

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?