FROM:http://zh.wikipedia.org/wiki/Itanium

Itanium

| 建议合并IA-64到本条目或章节。(讨论) |

| Itanium 2 | |

|---|---|

Itanium 2 商标 | |

| 生产时间 | 2001年至现在 |

| 制造商 | |

| 处理器速度 | 733 MHz 至1.73 GHz |

| 前端总线速度 | 300 MHz 至667 MHz |

| 指令集架构 | Itanium |

| 接口 |

|

| 核心 |

|

Itanium(官方中文名称为安腾),是 Intel Itanium 架构(通常称之为IA-64)的 64位处理器。Intel 推出了两个 Itanium 的家族:其一是Itanium,另一个是 Itanium 2。在 2007年 11月1日,Itanium 2 的家族又再一次称为 Itanium。该处理器的市场定位是在于企业服务器与高性能运算系统。该架构由 HP 创始,后来则是 HP 与 Intel 共同开发。

Itanium的微架构是彻底的不同于其他 Intel 处理器采用的 x86(包含x86-64)架构。这个架构是建基于显性的指令并发,由编译器来决定哪些指令并发处理。这种方式允许处理器在每个周期最多可以运行 6 个指令。与超标量架构的不同点,Itanium在并发处理中并没有复杂的线路来判断指令依赖性,所以编译器必须要在编译的时候就已经处理妥当。

在一系列的拖延开发进度后,第一款 Itanium 于 2001年推出,性能更强的 Itanium 处理器在之后则是有周期性的持续推出。采用 Itanium 处理器的制造商之中,以 HP 的制造量最多。在 2007年,Itanium 在企业界系统采用的架构之中是位于第四名,而前三名则是x86-64、IBM POWER 与 SPARC。Intel 推出最新的 Itanium 处理器为 Montvale 核心,于 2007年 11月推出。[1]

目录[隐藏] |

[编辑]历史

[编辑]开发:1989 至 2001

在 1989 年,HP 认为 RISC 架构将来会遇到每周期只能运行一个指令的瓶颈。而 HP 的研究员在研究一个称之为显式并发指令运算(EPIC)的新架构,该架构允许处理器在一个周期内运行多条指令。EPIC 是一种超长指令字(VLIW)架构,每个这种指令即包含多条小指令。使用 EPIC 技术后,编译器就能决定让这些小指令同时运行于单一周期,因此处理器能够简单的运行这些指令而不需要很复杂的架构去决定哪些指令能够并发运行。[4]

HP 认为它对个别企业系统公司不具有足够的成本效益来自行开发自己的处理器,所以 HP 在 1994年与 Intel 结为合作伙伴来开发 EPIC 为基础的 IA-64 架构。而 Intel 预测 IA-64 微处理器将会被使用多数的企业系统制造业采用而给予大量的开发资源。在 1998年,HP 与 Intel 发表共同的大规模合作开发的成品,内部代号为 Merced。[4]

在开发期间,Intel、HP 还有工业分析家预测 IA-64 将会支配服务器、工作站、高级电脑,甚至取代 RISC 与 CISC 架构的所有既有产品。此预测导致 Compaq 与 Silicon Graphics 决定放弃 Alpha 与 MIPS 架构的未来开发计划而偏爱转移至 IA-64 架构。[5]

数个集团分别开始为该架构开发操作系统,包含 Microsoft Windows、Linux 与 Unix 的派生版本像是 HP-UX、Solaris、Tru64 UNIX与 Project Monterey[6](后三者在进入市场之前就已被取消)。在 1997 年发现 IA-64 架构与该编译器的开发难度比预期还要高,所以 Merced 的推出时间就一再顺延。[7]该技术困难包含需要非常大量的晶体管才能处理超长指令与大量高速缓存。在该架构的项目还有一些结构性的问题,在两部分的集成团队使用不同的算法而有些微不同的优先度。自从第一颗 EPIC 架构的处理器 Merced 推出后,开发团队也陆续遭遇更多之前未预料到的问题。除此之外,EPIC 的概念依赖于编译器的处理能力,而之前完全没有实现过,所以许多未预测到的研究也出现。

Intel 在 1999年 10月4日发表该处理器的官方名称 Itanium。[8]几小时之后观察家指出该处理器参考 Itanic,[9]源自于 Titanic,在 1912 年沉没的号称“不可能”沉没的远洋邮轮。不少评论媒体暗示 Itanium 像是个大白象耗资亿元的产物却无法达到既定性能与销售量。但此时 RISC 与 CISC 的架构长足的增强超标量的性能,能够不使用 EPIC 的技术来破除单一周期只能运行一个指令的魔咒。

[编辑]第一代 Itanium 处理器:2001 至 2002

| Itanium | |

|---|---|

Itanium 处理器 | |

| 生产时间 | 2001年 6月至2002年 6月 |

| 制造商 | |

| 处理器速度 | 733 MHz 至800 MHz |

| 前端总线速度 | 266 MT/s |

| 制作工艺 | 0.18µm |

| 指令集架构 | Itanium |

| 接口 |

|

| 核心 |

|

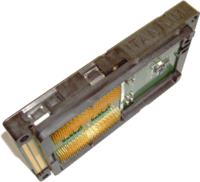

| Itanium 800MHZ L3 4M | |

|---|---|

Itanium 800MHZ L3 4M 处理器 |

| Itanium 800MHZ L3 4M | |

|---|---|

Itanium 800MHZ L3 4M 处理器 |

第一代 Itanium 在 2001年 6月推出,但是却不优于同时代的 RISC 与 CISC 处理器。Itanium 与 x86 的低级服务器(小于4 CPU 的系统)竞争,还有跟高级的 IBM POWER 架构与 SPARC 架构竞争市场。而 Intel 重新定位 Itanium 指向高级商务与高性能运算系统,尝试去复制 x86 架构中非常成功的横向市场发展(单一架构,多个系统制造厂)。不过却被局限在业界不想更换 HP 制造的 PA-RISC 与Alpha,还有 SGI制 MIPS 架构的高性能运算系统。因为当 x86 架构切入商用市场上,POWER 与 SPARC 架构还算是很强健的。以预算为主的考量,x86 在商用运算的横向发展中是非常优秀的选择。HP 与 Intel 此时发现 Itanium 无法与其他系统相提并论,就在一年后就推出 Itanium 2 来取代旧有的 Itanium。由于缺乏足够的产额、差劲的性能,还有高售价,第一代 Itanium 只有售出几千组系统。不过这些系统在开发 Itanium 2 的软件时是相当有用的。不过既使如此,IBM 还是有制造出搭载此处理器的超级电脑。[10]

[编辑]Itanium 2 处理器:2002 至今

Itanium 2 于 2002年推出,它的市场定位改成企业服务器而不是整个高性能运算的范围。最初 Itanium 2 的内部代号为 McKinley。它使用 180 纳米制程,不过它解决了很多前一代性能不彰的问题。[11]

在 2003年,AMD 推出 Opteron,是第一款含 x86-64 技术的处理器。而它在企业服务器的领域中被快速接纳的原因是它能够很容易的从 x86 的架构中升级。而 Intel 则是在 2004年推出有 x86-64 技术的 Xeon 处理器还击。[12] 2003年 Intel 也推出了新的 Madison 核心的 Itanium 2。采用 130 纳米制程制造而成,而更新的 Montecio 则是在 2006年 6月推出。

在 2005年 3月,Intel 宣布它正在运行新的 Itanium 计划,代号为 Tukwila 将于 2007年问世。Tukwila 将配备四颗处理器,而且会用新的通用系统接口取代原有 Itanium 总线,而这种接口也会应用在 Xeon 上面。[13] 之后 Intel 说明 Tukwila 的问世将顺延至 2008年年尾。。[14]

在 2005年 11月,主要几个 Itanium 服务器制造厂商与 Intel 与一些软件开发商成立了 Itanium 解决方案联盟来宣传此架构且加速软件支持度。[15]而该协会发表初协会会员在 2010 年底将投资共 100亿美元为发展 Itanium。[16]

不过 Itanium 并不是 Intel 的主力产品。Intel 并没有说明制造出多少产品,但有一个业界分析家指出在 2007年 Intel 大约生产 20 万颗处理器。[17]

[编辑]架构

Intel 有庞大的 Itanium 指令集与微架构的纪录文件,[18]而且技术文件也提供浏览。[19][7]该微架构在历史上曾几度更名。HP 称之为 EPIC,后来改为PA-WideWord,后来 Intel 称之 IA-64,之后又改为 Itanium 处理器架构 (IPA),[20]在提出 Intel Itanium 架构之前,该架构通常称为 IA-64。这是明确且并发的 64 位暂存器架构。基础的数据长度为 64 个位,并能提供寻址,逻辑寻址空间为 264 字节。该架构并能提供分支预测与预测运行。它使用硬件暂存器更名结构而不是简单的暂存器映射。这相同的结构也用于判断允许并发运行循环。这些能力是可以被编译器控制的:每个指令字包含许多此动作。这就是该架构的特点之一。

此架构提供 128 个整数暂存器、128 个浮点数暂存器、64 个单位预测器与 8 个分支暂存器。而浮点数暂存器的长度高达 82 个位而能够提供精确的运算结果。

[编辑]指令运行

每个 128 位的指令字就包含三个小指令,预读机制可以在每个周期中从 L1 高速缓存中读取两个指令到管线。当编译器能够在这个机制上获得最大优势,处理器就能在每个周期中运行六条指令。该处理器在 11 个组群中有 30 个功能性运行单位。每一个单位能够运行指令集中的特殊子集,除非为了等候数据中止运行,否则每个单位就会每个周期运行一个指令。且并不是在一个组群的所有单位运行指令集的相同子集,而是共同的指令能在多个单位中被运行。这些组群包括:

- 六个一般的 ALU、两个整数单位与一个移位单位

- 四个数据高速缓存单位

- 六个多媒体单位、两个平行移位单位、一个平行乘法器与一个组群计数器

- 两个浮点乘积累加器,两个“杂项的”浮点单位

- 三个分支单位

因此,编译器能时常聚集指令进入同时能运行的六个的组群。因为浮点单位运行一次乘积累加运算,当应用程序需要将相加数值做乘积,一个浮点指令就能运行二个指令的工作:这在科学处理中非常常见。当这种情况发生后,处理器就能在每个周期运行四个指令(4 FLOPS)。比方来说,800 MHz 的 Itanium 理论运算能力为 3.2 GFLOPS,然后最快的 Itanium 2,时钟频率微 1.67 GHz 的运算能力则达 6.67 GFLOPS。

[编辑]存储器架构

Itanium 2 处理器层次结构式的使用共享的高速缓存。等级1(L1)有16KB的指令高速缓存与16KB的数据高速缓存。等级2(L2)是256KB的统一型(指令与数据共用)高速缓存。L3也是统一型的高速缓存,不过大小从1.5MB至24MB不等。在256KB的L2高速缓存中包含了足够的逻辑电路来处理信号量就不需要使用到算术逻辑单元(ALU)。

主存则是通过总线联系至芯片组来访问。Itanium 2 的总线最初称之为 McKinley bus,不过现在通常直接称之为 Itanium 总线。该总线的速度会因为新处理器的发布而显著提升。总线在每个周期传输 2×128 个位,所以 200 MHz 总线的传输率达 6.4 GB/s,而 533 MHz 的总线的传输率则是高达 17.056 GB/s。[21]

[编辑]架构修改

在 2006年之前推出的 Itanium 处理器一概支持 IA-32 架构来支持旧有的服务器应用程序,但是与同世代的本地 x86 来比性能是相当糟糕的。而在 2005 年 Intel 开发出 IA-32 EL 软件模拟器来提供更好的性能。在 Montecito,Intel 移除了 IA-32 的硬件支持。

虽然 Montecito 没有 IA-32 的能力,但是 Intel 也在增强了一些功能在这颗核心上。[22]该架构支持硬件多线程,也就是一颗处理器能够处理两个运行绪。当其中一个运行绪要去读写存储器时,另一个运行绪就运行指令。Intel 为了区分在 x86 处理器的超线程,在 Itanium 称之为“稀疏运行绪”(Coarse multithreading)。稀疏运行绪搭配 Itanium 架构所得的性能增进是显而易见的。Intel 也在该核心上支持硬件的虚拟化技术。虚拟化技术能够在性能损失降到最低时同时运行多个操作系统。除此之外 Montecito 也具备了分离式 L2 高速缓存,新增专用的 1 MB L2 指令高速缓存,原本 256 KB 的 L2 高速缓存则是变成数据高速缓存。

[编辑]硬件支持

[编辑]系统

| 公司 | 最新产品 | |||

|---|---|---|---|---|

| 名称 | 始于 | 直到 | 服务器名 | CPUs |

| 惠普 | 2001 | - | Integrity | 1-128 |

| 康柏 | 2001 | 2001 | Proliant 590 | 1-4 |

| 戴尔 | 2004 | 2005 | PowerEdge 7250 | 1-4 |

| IBM | 2001 | 2005 | x455 | 1-16 |

| 富士通 | 2005 | - | PRIMEQUEST | 1-32 |

| NEC | 2002 | - | Express5800 /1000 | 1-32 |

| SGI | 2001 | now | Altix 4000 | 1-1024 |

| 日立 | 2001 | - | BladeSymphony 1000 | 1-8 |

| Bull | 2002 | - | NovaScale | 1-32 |

| Unisys | 2002 | - | ES7000/one | 1-32 |

在 2007年,部分制造厂商提供搭载 Itanium 2 的系统,包含 HP,SGI、NEC、Fujitsu、Unisys、Hitachi 与 Groupe Bull。除此之外,Intel 也有提供机架[23]提供给系统组装员建造 Itanium 系统。HP 则是目前唯一一家业界中前四大服务器制造厂提供搭载 Itanium 的系统,超过 80% 的 Itanium 2 系统是由 HP 制造出来的。在 2006 年第一季 HP 售出多达 7200 组 Itanium 系统。[24]左右系统的售价是取决于企业服务器与技术性运算的规模,平均一组系统造价约 200,000 美元。一般的 Itanium 系统会搭载 8 颗以上的处理器。

[编辑]芯片组

Itanium 的总线接口是靠芯片组来联系的。企业服务器制造厂区分系统的不同点,是在于开发设计不同的芯片组来连结处理器到存储器、内部连结还有周边控制器。这些芯片组在每个系统架构的设计中是非常重要的。目前而言,Itanium 的芯片组有 HP、Fujitsu、SGI、NEC、Hitachi 与 Unisys 分别开发。IBM 与 Intel 分别于 2003 与 2002 年也有推出芯片组,但是他们并没有支持比较新的技术,像是 DDR2 或是 PCI Express。[25]

[编辑]软件支持

为了让更多的软件可以运行在Itanium上,Intel支持开发Itanium平台的有效的编译器,特别是自身包的编译器Intel Compiler。[26][27] GCC、[28][29]Open64与 MS Visual Studio 2008(及后来版本)[30] 也都能够编译出Itanium的程序。直到2007年,Itanium支持的操作系统有Windows Server 2003、好几种的Linux版本(包括 Debian、Red Hat与SUSE)、FreeBSD[31]、HP-UX、OpenVMS与HP的NonStop。它也支持主机环境的GCOS还有一些IA-32的操作系统也能通过指令集模拟器在Itanium运行。使用QuickTransit就能经由“动态位转换”让IRIX(MIPS架构)与Solaris(SPARC架构)运行于Itanium的Linux 上。根据Itanium解决方案联盟指出,在2007年初有超过一万个应用程序可以运行于Itanium系统上,[32]但是升阳对此数字保持怀疑态度。[33]而该协会也支持Gelato,一个Itanium高性能运算用户组群与开发者社区之园开放源代码的Itanium。[34]

[编辑]竞争对手

Itanium 2 主要是面向大型企业服务器的市场,所以主要竞争对手如下:

- Sun Microsystems

- UltraSPARC IV+

- Fujitsu 的 SPARC64+

- IBM 的 POWER6

- AMD 的 Opteron

- Intel 自家的 Xeon

综观 Itanium 的历史,相较于一般处理器的固定小数点运算性能,它具有相当优秀的浮点运算处理性能。这项优势对高性能运算系统是很有帮助的,但是在大多数的企业服务器的负载上是较不注重这方面的性能。

[编辑]超级电脑

搭载 Itanium 架构的电脑第一次出现在 TOP500 的超级电脑列表是在 2001年 11月。搭载着 Itanium 2 的超级电脑在该列表中最佳纪录是在 2004年 6月的 Thunder 以 Rmax 为 19.94 TFLOPS 获得第二名。在 2004年 11月 Columbia 超级电脑以 51.8 TFLOPS 的运算速度再次获得第二名,而且直到 2007年 6月为止至少有一台超级电脑进入前十名。而在此名单中在 2004年 11月的名单中有高达 16.8% 的电脑是搭载 Itanium 系列,而在 2010年 11月则是降到 1 %。[35]

[编辑]处理器

[编辑]已推出

Itanium 处理器在性能上显现出长足的进步。Merced 是实做对架构的概念。而 McKinley 显著的提升高速缓存的等级而且让 Itanium 能够与其他架构平起平坐。Madison 则是借由转移到 130 纳米制程,能够增加高速缓存大小来克服主要性能的瓶颈。Montecito 使用的是 90 纳米制程,允许实现双核心并且在能源效率上取得进步。Montvale 加入了 3 个新功能:Core-level lockstep、demand-based switching 与前端总线频率提升到 667 MHz。

| 内部代号 制程 | 推出时间 | 时钟频率 | L2 高速缓存/ 每核心 | L3 高速缓存/ 每核心 | 前端总线 | 芯片数/ 每设备 | 核心数/ 每芯片 | 瓦特/ 每设备 | 附注 | |

|---|---|---|---|---|---|---|---|---|---|---|

| Itanium | ||||||||||

| Merced 180 纳米 | 2001-06 | 733 MHz | 96 KB | 2 MB* | 266 MHz | 1 | 1 | 116 | 外部 L3 高速缓存 | |

| 2001-06 | 800 MHz | 96 KB | 4 MB* | 266 MHz | 1 | 1 | 130 | |||

| Itanium 2 | ||||||||||

| McKinley 180 纳米 | 2002-07-08 | 900 MHz | 256 KB | 1.5 MB | 400 MHz | 1 | 1 | 130 | HW branchlong, on-die L3 cache | |

| 2002-07-08 | 1 GHz | 256 KB | 3 MB | 400 MHz | 1 | 1 | 130 | |||

| Madison 130 纳米 | 2003-06-30 | 1.3 GHz | 256 KB | 3 MB | 400 MHz | 1 | 1 | 130 | ||

| 2003-06-30 | 1.4 GHz | 256 KB | 4 MB | 400 MHz | 1 | 1 | 130 | |||

| 2003-06-30 | 1.5 GHz | 256 KB | 6 MB | 400 MHz | 1 | 1 | 130 | |||

| 2003-09-08 | 1.4 GHz | 256 KB | 1.5 MB | 400 MHz | 1 | 1 | 130 | |||

| 2004-04 | 1.4 GHz | 256 KB | 3 MB | 400 MHz | 1 | 1 | 130 | |||

| 2004-04 | 1.6 GHz | 256 KB | 3 MB | 400 MHz | 1 | 1 | 130 | |||

| Deerfield 130 纳米 | 2003-09-08 | 1.0 GHz | 256 KB | 1.5 MB | 400 MHz | 1 | 1 | 62 | 低电压 | |

| Hondo 130 纳米 | 2004-Q1 | 1.1 GHz | 256 KB | 4 MB | 400 MHz | 2 | 1 | 260 | 32 MB L4 高速缓存 | |

| Fanwood 130 纳米 | 2004-11-08 | 1.6 GHz | 256 KB | 3 MB | 533 MHz | 1 | 1 | 130 | ||

| 2004-11-08 | 1.3 GHz | 256 KB | 3 MB | 400 MHz | 1 | 1 | 62? | 低电压 | ||

| Madison 9M 130 纳米 | 2004-11-08 | 1.6 GHz | 256 KB | 9 MB | 400 MHz | 1 | 1 | 130 | ||

| 2005-07-05 | 1.67 GHz | 256 KB | 6 MB | 667 MHz | 1 | 1 | 130 | |||

| 2005-07-18 | 1.67 GHz | 256 KB | 9 MB | 667 MHz | 1 | 1 | 130 | |||

| Montecito 90 纳米 | 2006-07-18 | 1.4 GHz | 256 KB+ 1 MB | 12 MB | 400 MHz | 1 | 2 | 104 | 虚拟化技术、 多线程、 没有硬件 IA-32 支持 | |

| 2006-07-18 | 1.6 GHz | 256 KB+ 1 MB | 12 MB | 533 MHz | 1 | 2 | 104 | |||

| Itanium 2 9000 系列 | ||||||||||

| Montecito 90 纳米 | 2006-07-18 | 1.4 GHz | 256 kB (D)+ 1 MB (I) | 6-24 MB | 400 MHz | 1 | 2 | 104 | Virtualization, Multithread, no HW IA-32 | |

| 1.6 GHz | 533 MHz | |||||||||

| Itanium 2 9100 系列 | ||||||||||

| Montvale 90 纳米 | 2007-10-31 | 1.42–1.66 GHz | 256 kB (D)+ 1 MB (I) | 8-24 MB | 400–667 MHz | 1 | 1–2 | 75–104 | Core-level lockstep, 按需切换技术 | |

| Itanium 9300 系列 | ||||||||||

| Tukwila 65 纳米 | 2010-02-08 | 1.33-1.73 GHz | 256 kB (D)+ 512 kB (I) | 10-24 MB | QPI, 速率为 4.8 GT/s | 1 | 2–4 | 130–185 | 新的内核间通信方式, 快速通道互联, 代替了 前端总线. 睿频加速 | |

[编辑]未来产品

未来的 Itanium 家族基于既有的信息,会趋向多核心芯片的方向前进。已知信息如下:

- Poulson 将会使用 32 纳米制程且具有至少 4 核心在 CPU 内,改良的多线程技术,还有能够在平行处理性能增进的新指令集,特别是在虚拟化技术。预计将在2012年推出。

[编辑]时间线

- 1989:

- HP 开始研究 EPIC。[4]

- 1994:

- 6月:HP 与 Intel 宣布结为合作伙伴。[36]

- 1995:

- 1996:

- 1997:

- 1998:

- 3月:SCO 承认 HP/SCO Unix alliance 研发失败

- 6月:IDC 再度预测在 2001年 IA-64 系统的年销量会达到 300亿美元。[2]

- 6月:Intel 宣布延迟 Merced 的研发计划,从 1999 年中顺延到 2000年初。[41]

- 9月:IBM 宣布将打造搭载 Merced 的电脑。[42]

- 10月:为了让通用 UNIX能够在 IA-64 架构上运行,成立 Project Monterey 团队

- 1999:

- 2月:为了让 Linux 支持 IA-64,成立 Project Trillian 团队

- 8月:IDC 预测在 2002年 IA-64 系统的年销量会达到 250亿美元。[2]

- 10月:Intel 发表该处理器之官方名称 Itanium。

- 10月:首次使用 Itanic 这个词。

- 2000:

- 2月:Project Trillian 推出 IA-64 的 Linux 源码。

- 6月:IDC 预测在 2003年 Itanium 系统的年销量会达到 250亿美元。[2]

- 7月:Sun 与 Intel 放弃 Solaris 在 Itanium 的计划。[43]

- 8月:AMD 推出 x86-64 的规格,是将 Intel 固有的 x86 架构扩充至 64位的一系列指令集,借此与 IA-64 竞争。在市场上以 AMD64 的名称称之。

- 2001:

- 6月:IDC 预测在 2004年 Itanium 系统的年销量达 150亿美元。[2]

- 6月:Project Monterey 团队解散。

- 7月:Itanium 推出。

- 10月:IDC 再次预测在 2004年 Itanium 系统的年销量达 120亿美元。[2]

- 11月: 位于国家超级电脑应用中心的 IBM 制造之 320 颗处理器簇的系统在 TOP500 的列表中名列 34 名。

- 11月:Compaq 因为处理器的问题而延迟发表 Itanium 的产品。[44]

- 12月:创立 Gelato。

- 2002:

- 3月:IDC 再次预测在 2004年 Itanium 系统的年销量为 50亿美元。[2]

- 6月:推出 Itanium 2。

- 2003:

- 2004:

- 2005:

- 2006:

- 2007:

- 10月:Intel 推出 Montvale Itanium 2

- 11月:Intel 将该系列处理器重命名为最初的Itanium。

- 2008:

- 8月: HP放弃AdvFS集成到HP-UX,反而把程序码开源。

- 2009:

- 12月:Red Hat放弃 Itanium软件开发[55]

- 2010

- 2011

1528

1528

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?