原创翻译再创作,原文章地址:https://www.intel.cn/content/dam/www/public/us/en/documents/manuals/64-ia-32-architectures-software-developer-vol-2a-manual.pdf 第三章 3.1

翻译若有勘误,请在下方评论或联系

chenbanghao37@163.com

前言

于intel64 and IA-32 架构完整版中的3-5章中详细描述了所有指令,但是如果不研究透其中的符号约定和缩写,恐怕你很难从中得到或得不到正确的信息。

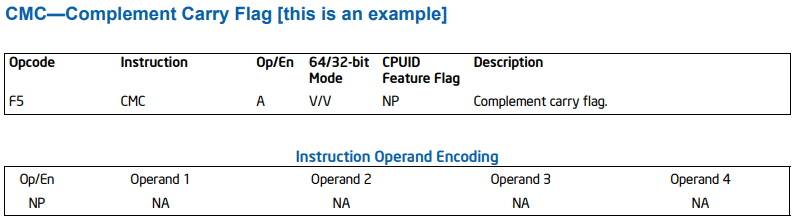

指令描述分为两部分,一部分是主体,由操作码、指令语法、操作数编码、关于64/32位模式的规定、CPUID功能标志和功能描述,另一部分是指令操作数的编码规定,由Op/En和四个操作数的规定组成,以下文章会分类列举各种各样的符号、缩写及其含义。

操作码列

操作码由16进制的目标代码和相关符号组成,其中符号的定义如下:

| 符号名称 | 描述 |

|---|---|

| REX.W | 需要编码REX前缀,使其改变操作数大小完成目的 |

| /r | ModR/M中的reg和r/m都必须是寄存器 |

| cb(1-byte), cw(2-byte), cd(4-byte), cp(6-byte), co(8-byte), ct(10-byte) | 用于指定代码偏移量或代码段寄存器的值 |

| ib(1-byte), iw(2-byte), id(4-byte), io(8-byte) | 指定立即数大小,操作码确定操作数是否为有符号数 |

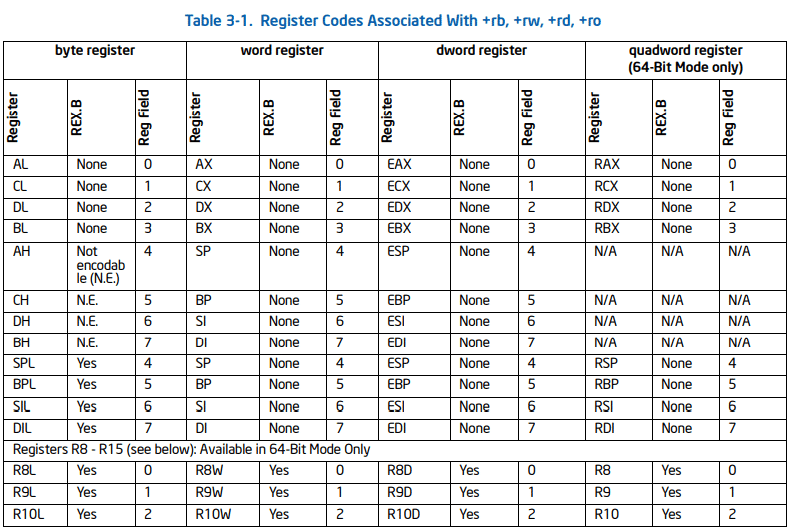

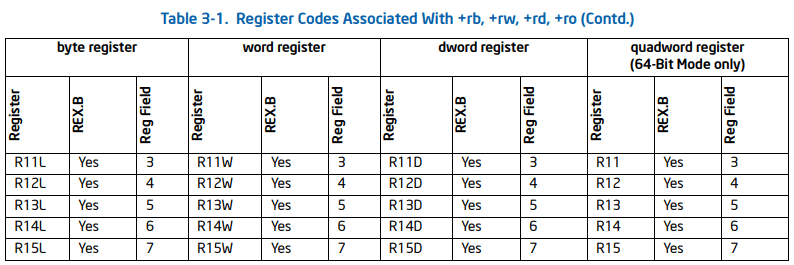

| +rb(1-byte reg), +rw(2-byte reg), +rd(4-byte reg), +ro(8-byte reg) | 编码指令二进制不足一个字节于操作码字节内的低三位的1/ 2/ 4/ 8位寄存器 |

指令语法列

以下是指令操作数的类型描述符号:

| 类型 | 描述 |

|---|---|

| r8, r16, r32, r64 | 使用8/16/32/64位寄存器 |

| imm8, imm16, imm32, imm64 | 使用8/16/32/64位立即数 |

| m8(byte), m16(word), m32(doubleword), m64(quadword), m128(double quadword) | 使用8/16/32/64/128位内存操作数,16/32/64位内存操作数统称为m |

| r/m8, r/m16, r/m32, r/m64 | 使用8/16/32/64位寄存器或内存操作数(r+m) |

| moffs8, moffs16, moffs32, moffs64 | MOV及其变体使用的8/16/32/64位不使用ModR/M字节而使用相对于段基的内存偏移实现的简单内存变量 |

操作数编码(Op/En)

于展示指令各样形式的指令汇总表之后的是编码操作数类型的编码定义表,指令汇总表的Op/En列中的各种字母与编码定义表相对应,其中操作数类型若为存储器类类型,则使用®即read或(w)即write区分访问方式为读还是写

64/32位模式列

此列显示操作码序列在64位模式、兼容模式或其他IA-32模式下的支持情况,其中代表64位模式支持情况的符号如下(斜线左侧/64-Bit Mode列):

| 支持情况 | 描述 |

|---|---|

| V | 支持 |

| I | 不支持 |

| N.E. | 操作码序列仅不支持64位模式 |

| N.S. | 在64位模式下需要使用地址覆盖前缀否则不受支持 |

代表兼容/传统模式支持情况的符号仅有(斜线右侧/Compat/Leg Mode列)表示支持和不支持的V与I和表示在64位模式、兼容模式或IA-32模式下都不支持只有在传统IA-32模式下才有可能支持的N.E.

CPUID列

此列为缩写的CPUID功能标志,表示该指令支持的特殊CPUID处理器功能(如SSE/AVX)

若指令没有支持的CPUID功能,则64/32位模式列将分为64-Bit Mode和Compat/Leg Mode两列占住常见的CPUID列

其他

除了指令汇总表所在节外,还有详细描述功能节(Description)、描述指令操作的代码节(Operation)、对应C/C++函数的Intel® C/C++ Compiler Intrinsics Equivalents节和有关异常节(Exceptions)

本文详细介绍了Intel 64和IA-32架构指令集,包括操作码、指令语法、操作数编码、64/32位模式支持和CPUID功能标志。操作码由十六进制和特定符号组成,指令语法描述了不同类型的寄存器和立即数。64/32位模式列展示了指令在不同模式下的支持情况,CPUID列列出与指令相关的处理器功能。此外,还涵盖了异常处理和其他相关细节。

本文详细介绍了Intel 64和IA-32架构指令集,包括操作码、指令语法、操作数编码、64/32位模式支持和CPUID功能标志。操作码由十六进制和特定符号组成,指令语法描述了不同类型的寄存器和立即数。64/32位模式列展示了指令在不同模式下的支持情况,CPUID列列出与指令相关的处理器功能。此外,还涵盖了异常处理和其他相关细节。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?