一、引入原因

在分页存储系统中,用户作业的地址空间是一维线性的,这破坏了程序内部天然的逻辑结构。页面与源程序之间并不存在逻辑关系。引入分段存储管理方式的主要目的则是满足用户编程的需求,可以更好地体现模块化程序设计的思想。

二、段式程序设计

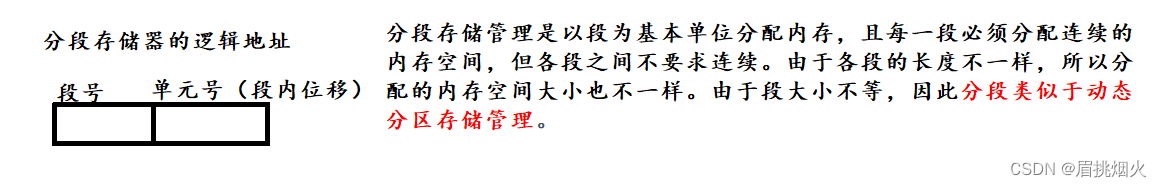

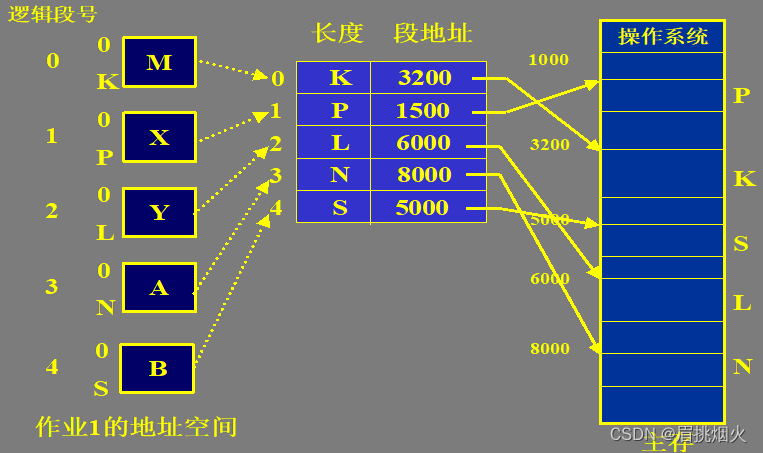

每个程序可由若干段组成,每一段都可以从“0”开始编址,段内的地址是连续的。

三、段式存储管理

1、基本实现思想

(1)基于可变分区存储管理实现,一个进程要占用多个分区。

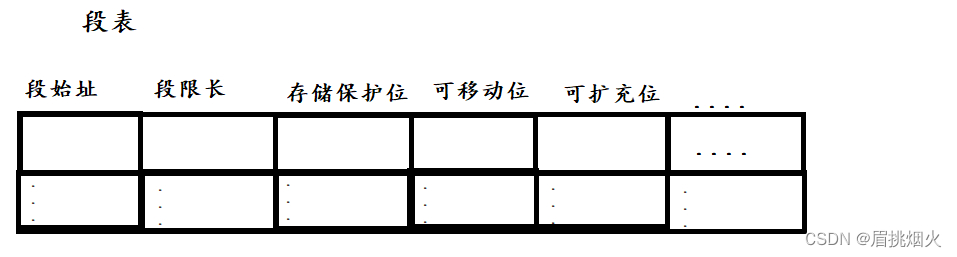

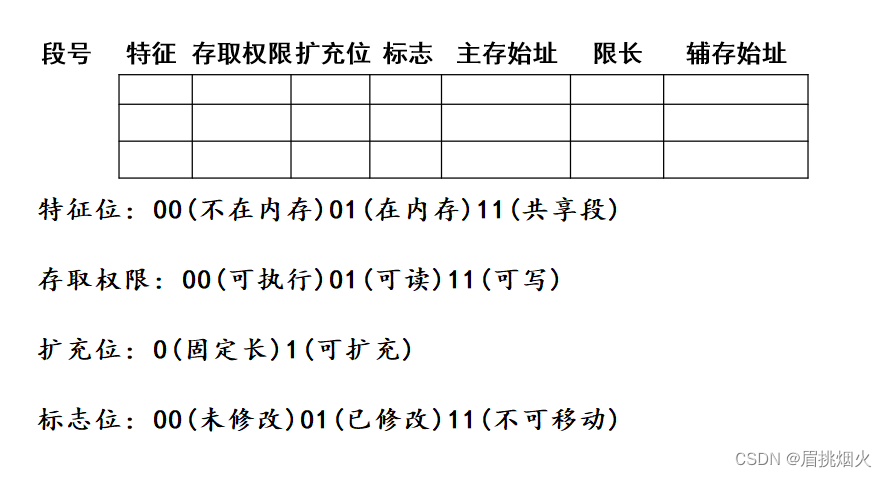

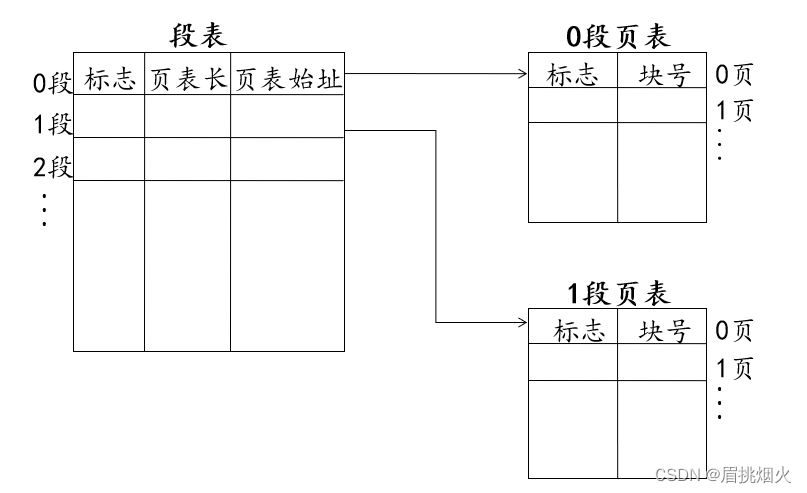

(2)设置一个段表,每个段占用一个段表项,包括:段始址、段限长,以及存储保护、可移动、可扩充等标志位。

(3)硬件需要增加一组用户可见的段地址寄存器(代码段、数据段、堆栈段,附加段),供地址转换使用。

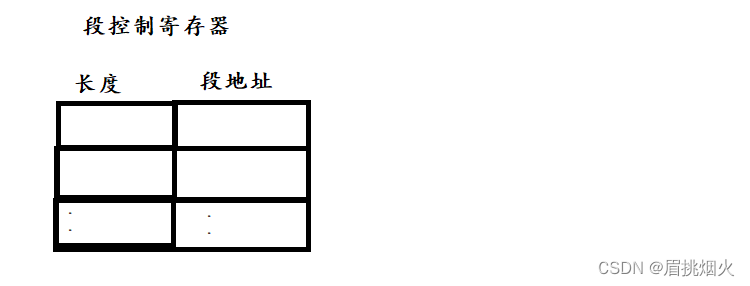

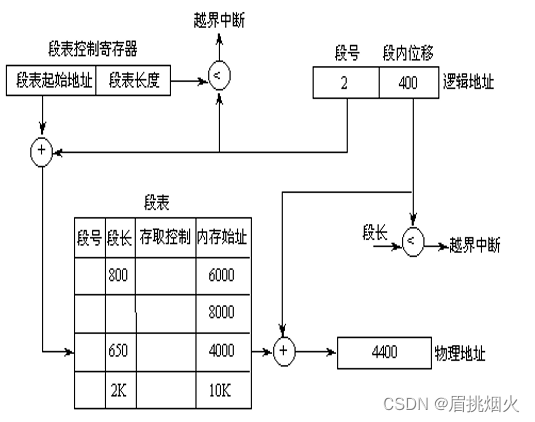

(4)硬件设置段控制寄存器,存放当前占有处理器的用户程序的段表在主存中的起始地址和段表长度。

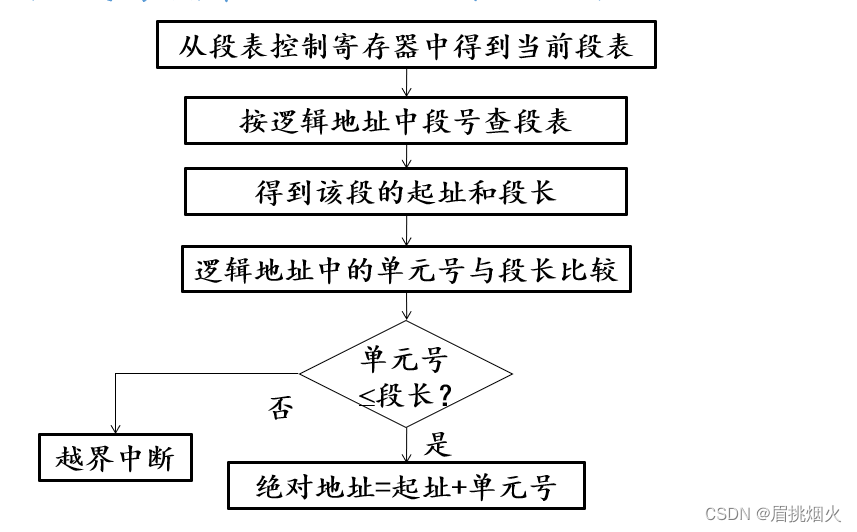

2、地址转换

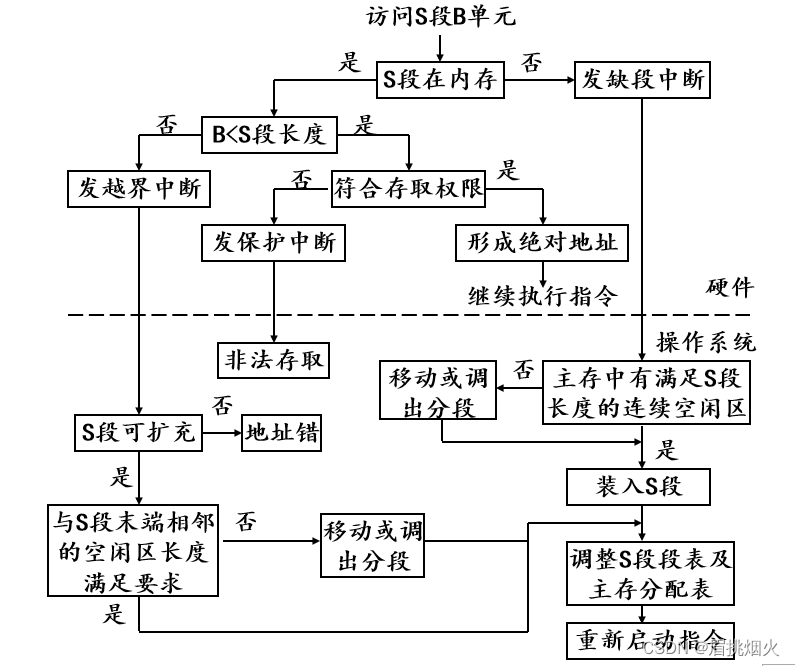

通过段寄存器将逻辑地址转换成物理地址(绝对地址),并进行存储保护。

3、段的共享

可以实现代码段和数据段的共享,只需要多个进程段表中的某段指向主存相同的地址(段基址),由于段是逻辑的概念,共享代码段和数据段都没有段号必须相同的要求。且对共享段的信息必须进行保护,如规定只能读出不能写入,不满足保护条件则产生保护中断。

四、段式虚拟存储管理

1、扩充段表

2、段页式存储管理

(1)每一段不必占据连续的存储空间,可存放在不连续的主存页框中(整体分成逻辑段,段内分为不同页)。

(2)能够扩充为段页式虚拟存储管理。

(3)装入部分段,或者装入段中部分页面。

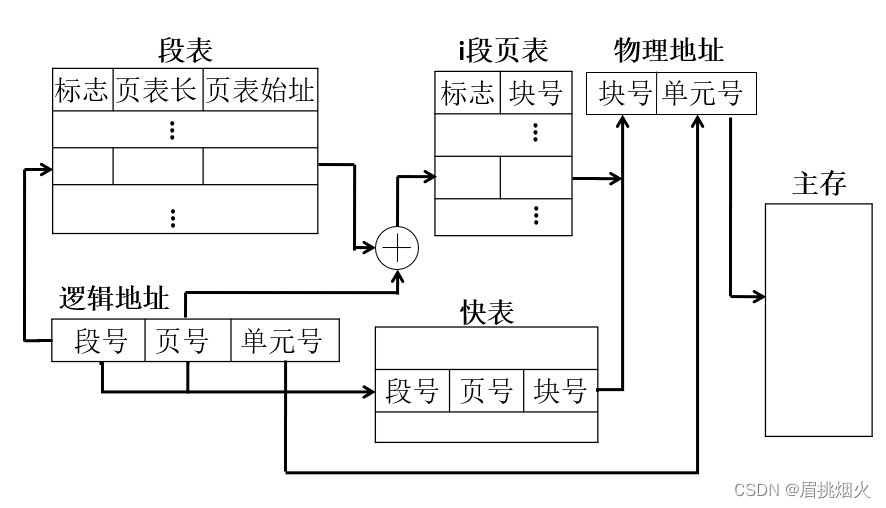

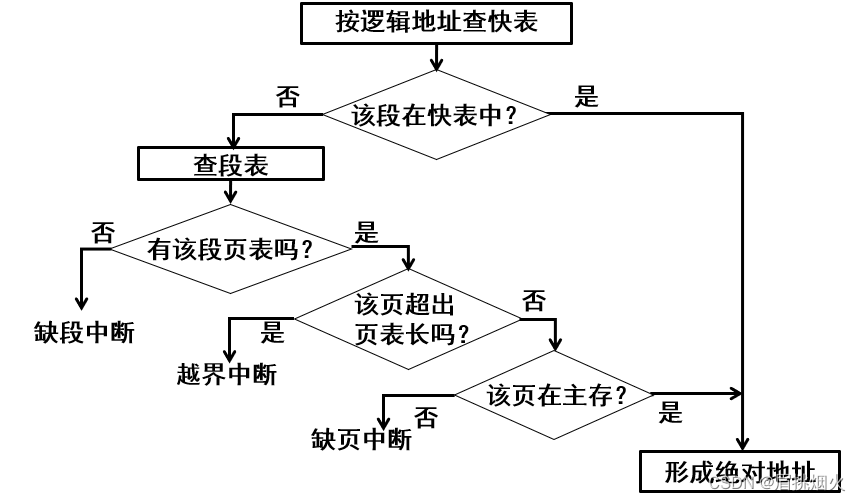

3、地址转换

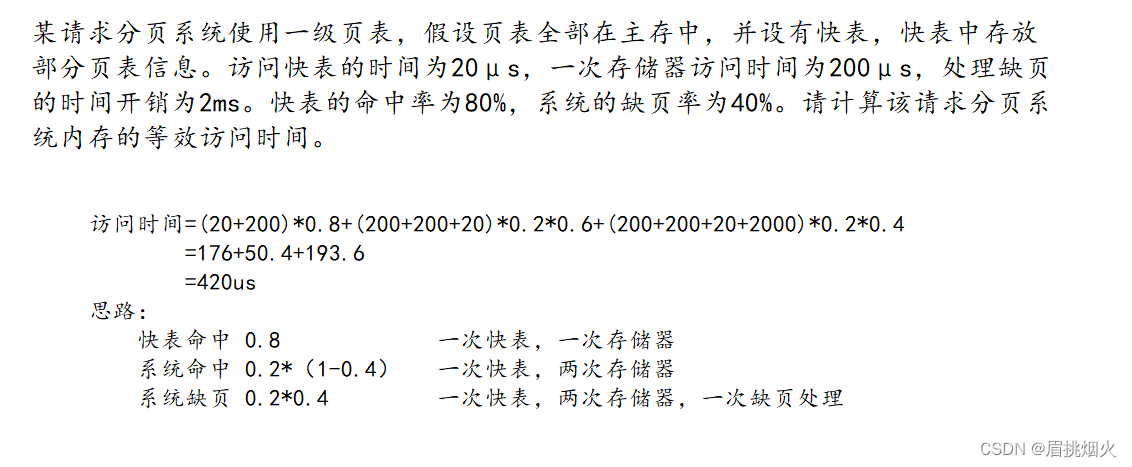

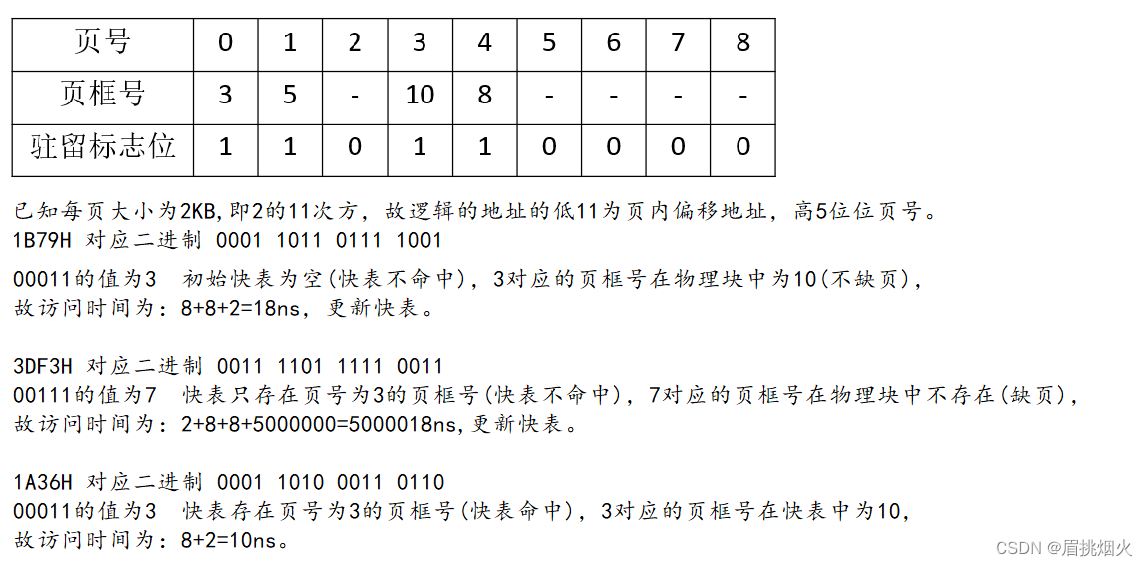

1、某请求分页系统使用一级页表,假设页表全部在主存中,并设有快表,快表中存放部分页表信息。访问快表的时间为20μs,一次存储器访问时间为200μs,处理缺页的时间开销为2ms。快表的命中率为80%,系统的缺页率为40%。请计算该请求分页系统内存的等效访问时间。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?