AD画芯片的原理图和封装

最新推荐文章于 2024-06-21 17:06:00 发布

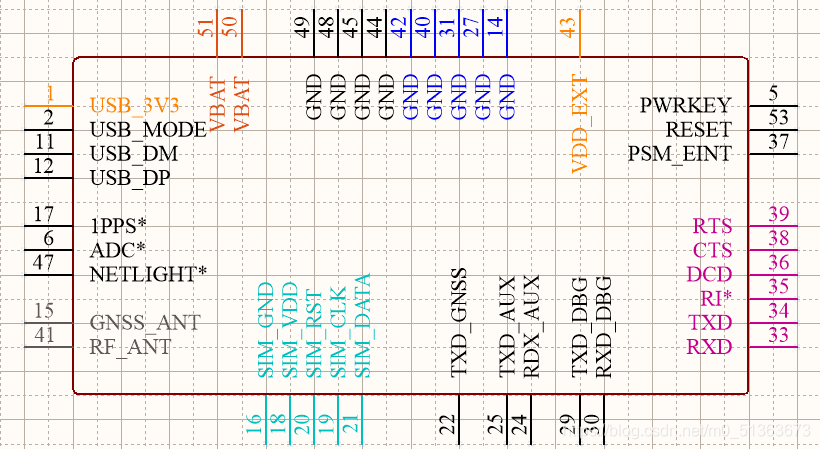

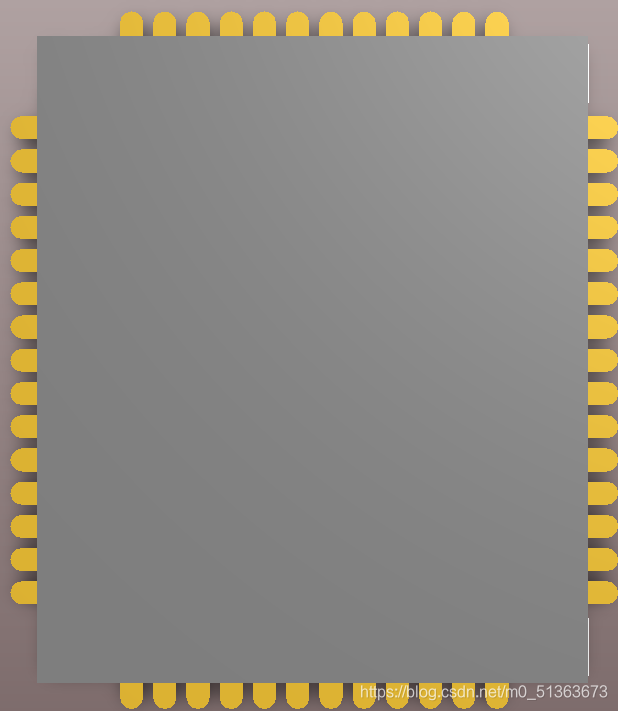

本文详细介绍了如何依据芯片数据手册,利用Altium Designer(AD)绘制芯片的原理图和封装。首先,参照数据手册的引脚分配图新建Schlib并调整引脚布局。接着,基于机械尺寸图在Pcblib中创建封装,利用IPC Compliant Footprint Wizard设置尺寸,并通过3D元件体创建立体效果。最后,提供了3D视角切换的快捷键操作。

本文详细介绍了如何依据芯片数据手册,利用Altium Designer(AD)绘制芯片的原理图和封装。首先,参照数据手册的引脚分配图新建Schlib并调整引脚布局。接着,基于机械尺寸图在Pcblib中创建封装,利用IPC Compliant Footprint Wizard设置尺寸,并通过3D元件体创建立体效果。最后,提供了3D视角切换的快捷键操作。

5859

5859

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?