- 实验类别

本实验为验证型实验。 - 实验目的

① 验证三人表决电路的功能。

② 能够运用 Verilog HDL 进行组合电路的设计和仿真。

③ 熟悉 Vivado 的设计流程,并进行硬件测试。 - 实验原理

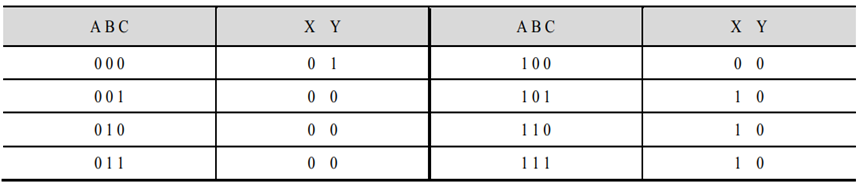

三人表决电路中,当表决某个提案时,多数人同意,则提案通过,同时有一个人具有否决权;若全票否决,也会显示。设输入为 A、B、C,且A具有否决权;同意用1表示,不同意用0表示;输出X为1时,表示提案通过;Y为1时,表示提案全票否决。那么,三人表决电路的真值表如下表所示。

4 实验内容和要求

1)三人表决电路的输入与仿真

学习软件平台和设计流程。利用 Vivado 完成三人表决电路的文本编辑输入和仿真测试等步骤,给出仿真波形。

2)设计实验方案

三人表决电路实验的结构框图如下图所示,输入信号 A、 B、 C 分别接拨码开关SW0、SW1、SW2,输出信号X、Y分别接指示灯LED1、LED2。

计算机组成原理实验报告 实验五 三人表决电路实验

于 2022-01-24 22:53:00 首次发布

本次实验旨在验证并设计三人表决电路,使用Verilog HDL进行组合电路设计,通过Vivado进行仿真和硬件测试。实验中,A具有否决权,输入A、B、C表示同意或反对,输出X表示提案通过,Y表示全票否决。实验步骤包括创建工程、编写代码、功能仿真、引脚绑定和硬件测试。

本次实验旨在验证并设计三人表决电路,使用Verilog HDL进行组合电路设计,通过Vivado进行仿真和硬件测试。实验中,A具有否决权,输入A、B、C表示同意或反对,输出X表示提案通过,Y表示全票否决。实验步骤包括创建工程、编写代码、功能仿真、引脚绑定和硬件测试。

订阅专栏 解锁全文

订阅专栏 解锁全文

6412

6412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?