H,表示是十六进制。

可以16进制运算,等同于10进制,2进制规则!

我们先草稿纸列出:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

1 2 3 4 5 6 7 8 9 A B C D E F H

则DFFFF-A0000得:(D-A=3)(F-0=F)(F-0=F)(F-0=F)(F-0=F)

最后得:3FFFF。

PS:为什么加一?从2000年到2009年共经历了多少年头?是不是2009-2000+1=10年?

然后3FFFF+1,产生进位变为:40000。注意这里还是16进制。

4 * 16^4 + 0 * 16^3 + 0 * 16^2 + 0 * 16^1 + 0 * 16^0 = 262144 B

单位是B!就是有 262144 个字节!

题目中有K的再除以1024 即可。

32K×8bit的意思:指的是这个芯片能够存储32k*8个位 (bit) (即 256Kb)也就是32K个字节 (Byte),(即 32KB)

解:

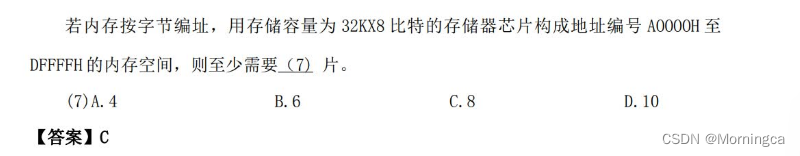

地址编号A0000H到DFFFFH的内存空间为 DFFFFH-A0000H+1=40000H,若内存按字节编址,即每个空间存储一个字节,则地址编号A0000H到DFFFFH的内存空间的存储容量为40000H * 8bit 。

4 * 16^4 + 0 * 16^3 + 0 * 16^2 + 0 * 16^1 + 0 * 16^0 = 262144 B

262144 B / 1024 = 256 KB

因为芯片的容量为 32K * 8 bit,1B = 8 bit,所以容量为 32KB

所以,256KB / 32KB = 8,需要 8 块芯片。

本文探讨了16进制的运算规则,并通过实例展示了如何计算内存空间的大小。从A0000H到DFFFFH的内存区域,经过计算得出其存储容量为256KB。结合32K*8bit的芯片规格,得出需要8块芯片来完成存储。内容涉及二进制、十六进制转换以及内存编址和存储单位的换算。

本文探讨了16进制的运算规则,并通过实例展示了如何计算内存空间的大小。从A0000H到DFFFFH的内存区域,经过计算得出其存储容量为256KB。结合32K*8bit的芯片规格,得出需要8块芯片来完成存储。内容涉及二进制、十六进制转换以及内存编址和存储单位的换算。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?