前言

本项目使用litex创建了一个soc,包括VexRiscv+uart+ddr+led+flash,并在上面运行了linux操作系统。

litex的项目不原生支持该板子,需要自己写一个

一、运行环境

全部都在ubuntu 22.04运行:下载链接:https://mirrors.sdu.edu.cn/ubuntu-releases/22.04/ubuntu-22.04.5-desktop-amd64.iso山大镜像源

二、使用步骤(无linux)

1.完成基础配置

#创建虚拟环境

python3 -m venv acx

#进入虚拟环境

source acx/bin/activate

#下载litex_setup.py文件

wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

#增加可执行权限

chmod +x litex_setup.py

#运行该文件

./litex_setup.py --init --install

下面是终端信息:

jiao@jiao-virtual-machine:~/acx720$ python3 -m venv acx

jiao@jiao-virtual-machine:~/acx720$ source acx/bin/activate

(acx) jiao@jiao-virtual-machine:~/acx720$ wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

--2024-11-26 19:32:40-- https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

正在解析主机 raw.githubusercontent.com (raw.githubusercontent.com)... 185.199.108.133, 185.199.110.133, 185.199.111.133, ...

正在连接 raw.githubusercontent.com (raw.githubusercontent.com)|185.199.108.133|:443... 已连接。

已发出 HTTP 请求,正在等待回应... 200 OK

长度: 19705 (19K) [text/plain]

正在保存至: ‘litex_setup.py’

litex_setup.py.1 100%[================>] 19.24K --.-KB/s 用时 0.02s

2024-11-26 19:32:41 (919 KB/s) - 已保存 ‘litex_setup.py’ [19705/19705])

(acx) jiao@jiao-virtual-machine:~/acx720$ chmod +x litex_setup.py

(acx) jiao@jiao-virtual-machine:~/acx720$ ./litex_setup.py --init --install当执行./litex_setup.py --init --install出现下载失败时,请看看ubuntu系统下的浏览器是否可以连接到github,我也没下载下来,我用我之前下载的。

若能正常访问,请看ssh是否配置好,配置教程如下Git教程 SSH keys配置-CSDN博客

若出现其他问题,请自行解决,可询问chatgpt或网络。

2.工程编译

在我这个板子上的ddr与原理图的型号不一样,需要自己改一下atest2_t.py文件

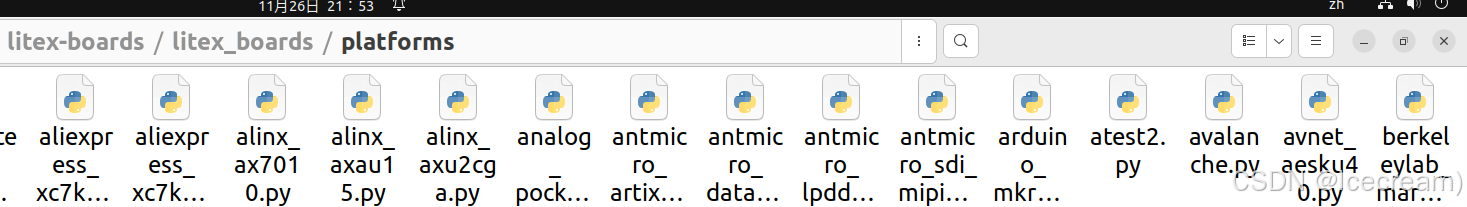

将atest2.py放在下载好的litex-boards/litex_boards/platforms文件夹下

将atest2_t.py放在litex-boards/litex_boards/targets文件夹下

现在确保我们的终端处在虚拟环境下(acx),输入以下命令

python3 -m litex-boards.litex_boards.targets.atest2_t --build

(acx)jiao-virtual-machine:~/acx720$ python3 -m litex-boards.litex_boards.targets.atest2_t --build

#最后会打印出的信息

===================================

Configuration Memory information

===================================

File Format BIN

Interface SPIX4

Size 16M

Start Address 0x00000000

End Address 0x00FFFFFF

Addr1 Addr2 Date File(s)

0x00000000 0x000E665B Nov 26 21:45:23 2024 atest2.bit

0 Infos, 0 Warnings, 0 Critical Warnings and 0 Errors encountered.

write_cfgmem completed successfully

# quit

INFO: [Common 17-206] Exiting Vivado at Tue Nov 26 21:45:27 2024...

之后会在acx720文件夹下生成build文件,生成的比特流文件在build/gateware文件夹下。

3.工程传入

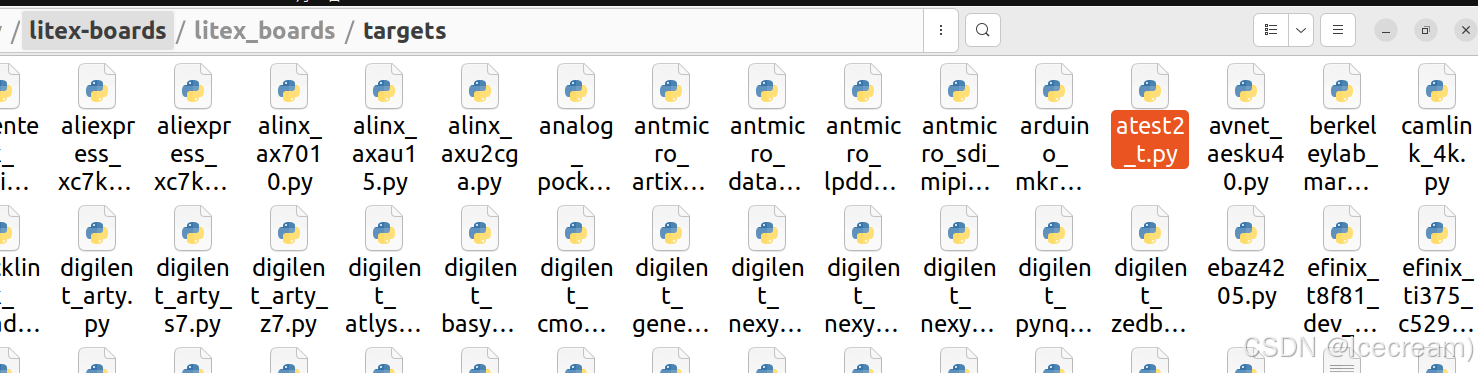

将bit文件通过vivado传到板子里,板子有两个micro-usb,接UART那个,接左边那个,接离数码管近的那个,接离以太网口远的那个。如下图所示:

之后打开一个新的终端,进入虚拟环境

#进入虚拟环境

source bin/activate

#假如找不到,在22.04上是由于一个软件导致的,解决方法如下链接

sudo chmod 777 /dev/ttyUSB0

#打开串口调试助手

litex_term /dev/ttyUSB0

#假如打开litex_term后没有信息出现,可能是ttyUSB没连对可能是ttyUSB1,2,3...

#也可能需要按板子上的S4键,即复位键。

ttyUSB找不到:ubuntu22.04 找不到串口,串口ttyusb时断时续的问题(拔插以后能检测到,过会儿就检测不到了)_ubuntu22.04不能识别串口-CSDN博客

下图是litex_term的信息,不知道输什么指令就输入help

oy-Digital

(c) Copyright 2007-2015 M-Labs

BIOS built on Nov 26 2024 21:37:58

BIOS CRC passed (139586bd)

LiteX git sha1: a350d2e90

--=============== SoC ==================--

CPU: VexRiscv @ 100MHz

BUS: wishbone 32-bit @ 4GiB

CSR: 32-bit data

ROM: 128.0KiB

SRAM: 8.0KiB

L2: 8.0KiB

FLASH: 16.0MiB

SDRAM: 256.0MiB 16-bit @ 800MT/s (CL-7 CWL-5)

MAIN-RAM: 256.0MiB

--========== Initialization ============--

Initializing SDRAM @0x40000000...

Switching SDRAM to software control.

Read leveling:

m0, b00: |00000000000000000000000000000000| delays: -

m0, b01: |00000000000000000000000000000000| delays: -

m0, b02: |11111111000000000000000000000000| delays: 03+-03

m0, b03: |00000000000011111111111000000000| delays: 17+-05

m0, b04: |00000000000000000000000000001111| delays: 29+-01

m0, b05: |00000000000000000000000000000000| delays: -

m0, b06: |00000000000000000000000000000000| delays: -

m0, b07: |00000000000000000000000000000000| delays: -

best: m0, b03 delays: 17+-05

m1, b00: |00000000000000000000000000000000| delays: -

m1, b01: |00000000000000000000000000000000| delays: -

m1, b02: |11111111100000000000000000000000| delays: 04+-04

m1, b03: |00000000000011111111111110000000| delays: 18+-06

m1, b04: |00000000000000000000000000001111| delays: 29+-01

m1, b05: |00000000000000000000000000000000| delays: -

m1, b06: |00000000000000000000000000000000| delays: -

m1, b07: |00000000000000000000000000000000| delays: -

best: m1, b03 delays: 18+-06

Switching SDRAM to hardware control.

Memtest at 0x40000000 (2.0MiB)...

Write: 0x40000000-0x40200000 2.0MiB

Read: 0x40000000-0x40200000 2.0MiB

Memtest OK

Memspeed at 0x40000000 (Sequential, 2.0MiB)...

Write speed: 36.8MiB/s

Read speed: 48.7MiB/s

Initializing mx25l12835f SPI Flash @0x01000000...

SPI Flash clk configured to 50 MHz

Memspeed at 0x1000000 (Sequential, 4.0KiB)...

Read speed: 5.0MiB/s

Memspeed at 0x1000000 (Random, 4.0KiB)...

Read speed: 2.3MiB/s

--============== Boot ==================--

Booting from serial...

Press Q or ESC to abort boot completely.

sL5DdSMmkekro

Timeout

No boot medium found

--============= Console ================--

litex> mem_test

mem_test <addr> [<maxsize>]

litex> mem_list

Available memory regions:

ROM 0x00000000 0x20000

SRAM 0x10000000 0x2000

MAIN_RAM 0x40000000 0x10000000

SPIFLASH 0x01000000 0x1000000

CSR 0xf0000000 0x10000

litex>

三、使用步骤(有linux)

在做完步骤2后,再进行该步骤

参考GitHub - litex-hub/linux-on-litex-vexriscv:LiteX-vexRiscv 上的 Linux的教程,大概下载一下我们上板所需要的东西。

#大概的需要的东西,具体看官方和后续步骤的报错

$ sudo apt install build-essential device-tree-compiler wget git python3-setuptools

$ git clone https://github.com/litex-hub/linux-on-litex-vexriscv

$ cd linux-on-litex-vexriscv

#在这个步骤Pre-built Bitstreams and Linux/OpenSBI images中

#这个下第一个文件,下载链接https://github.com/litex-hub/linux-on-litex-vexriscv/files/8331338/linux_2022_03_23.zip

#安装 RISC-V 工具链

$ wget https://static.dev.sifive.com/dev-tools/riscv64-unknown-elf-gcc-8.1.0-2019.01.0-x86_64-linux-ubuntu14.tar.gz

$ tar -xvf riscv64-unknown-elf-gcc-8.1.0-2019.01.0-x86_64-linux-ubuntu14.tar.gz

$ export PATH=$PATH:$PWD/riscv64-unknown-elf-gcc-8.1.0-2019.01.0-x86_64-linux-ubuntu14/bin/

#安装 OpenOCD

$ sudo apt install libtool automake pkg-config libusb-1.0-0-dev

$ git clone https://github.com/ntfreak/openocd.git

$ cd openocd

$ ./bootstrap

$ ./configure --enable-ftdi

$ make

$ sudo make install

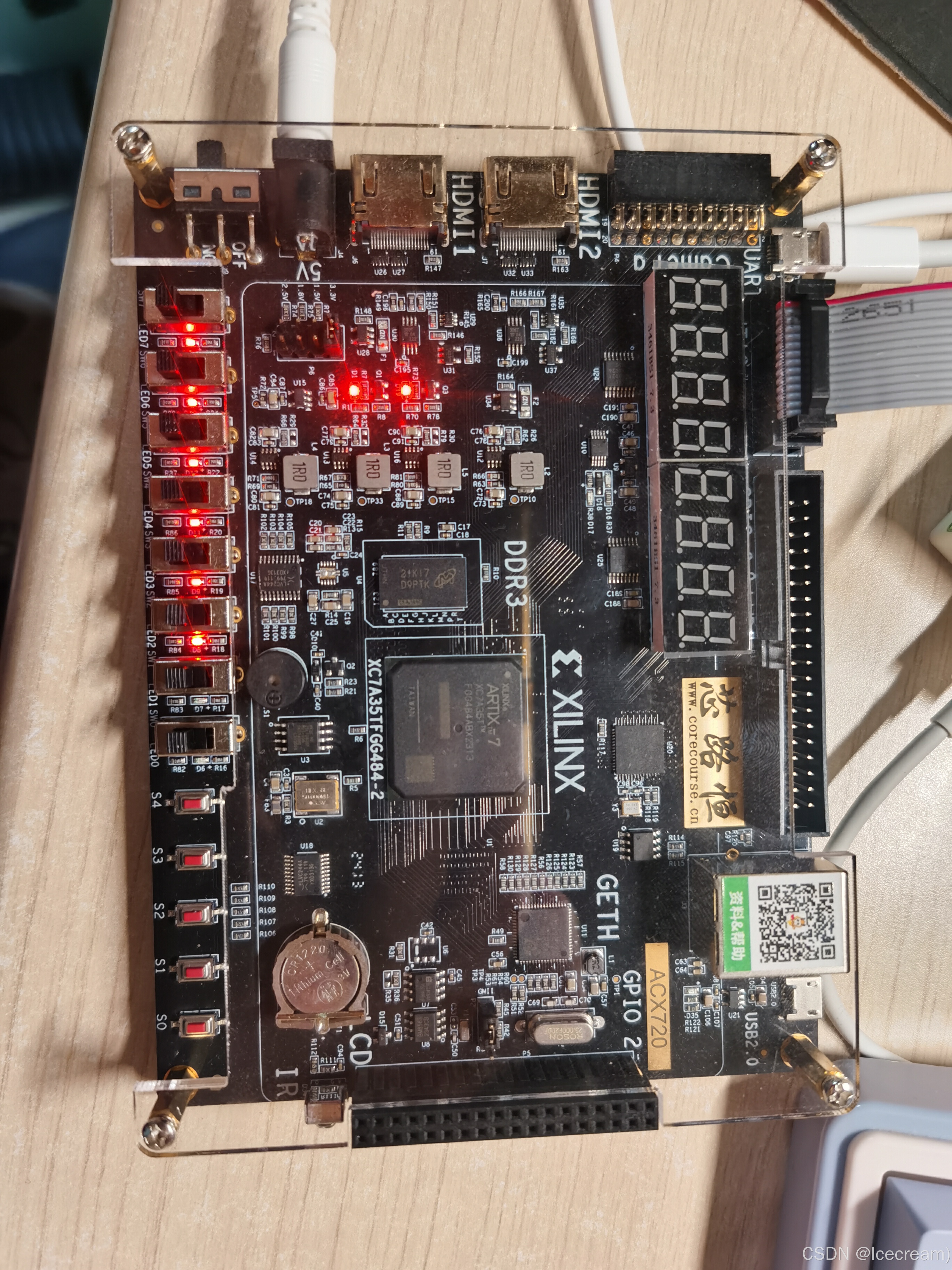

下一步将boards.py替换掉官方的boards.py

打开新终端,进入虚拟环境,之后将终端的目录切换到刚下好的linux-on-litex-vexriscv的目录下

(acx)jiao@jiao-virtual-machine:*****/****/linux-on-litex-vexriscv$

#输入该指令: ./make.py --board=atest2 --build

(acx) jiao@jiao-virtual-machine:~/env/linux/linux-on-litex-vexriscv$ ./make.py --board=atest2 --build

能够正常运行会有下面的信息,假如不能正常运行,就缺什么下什么。

INFO:SoC: / / (_) /____ | |/_/

INFO:SoC: / /__/ / __/ -_)> <

INFO:SoC: /____/_/\__/\__/_/|_|

INFO:SoC: Build your hardware, easily!

INFO:SoC:--------------------------------------------------------------------------------

INFO:SoC:Creating SoC... (2024-11-26 23:58:59)

INFO:SoC:--------------------------------------------------------------------------------

INFO:SoC:FPGA device : xc7a35t-fgg484-2.

INFO:SoC:System clock: 100.000MHz.

INFO:SoCBusHandler:Creating Bus Handler...

INFO:SoCBusHandler:32-bit wishbone Bus, 4.0GiB Address Space.

INFO:SoCBusHandler:Adding reserved Bus Regions...

INFO:SoCBusHandler:Bus Handler created.

INFO:SoCCSRHandler:Creating CSR Handler...

INFO:SoCCSRHandler:32-bit CSR Bus, 32-bit Aligned, 16.0KiB Address Space, 2048B Paging, big Ordering (Up to 32 Locations).

INFO:SoCCSRHandler:Adding reserved CSRs...

.........

===================================

Configuration Memory information

===================================

File Format BIN

Interface SPIX4

Size 16M

Start Address 0x00000000

End Address 0x00FFFFFF

Addr1 Addr2 Date File(s)

0x00000000 0x00105A87 Nov 27 00:08:25 2024 atest2.bit

0 Infos, 0 Warnings, 0 Critical Warnings and 0 Errors encountered.

write_cfgmem completed successfully

# quit

INFO: [Common 17-206] Exiting Vivado at Wed Nov 27 00:08:30 2024...

下一步打开vivado传入bit流,这里的bit文件在linux-on-litex-vexriscv的目录下的build文件夹下。

在完成bit流传入后,打开新的终端,先进虚拟环境,通过cd指令进到linux-on-litex-vexriscv的目录下,执行下面的指令

litex_term --images=images/boot.json /dev/ttyUSB0如下面所示:,出现buildroot login: 输入 root

(acx) jiao@jiao-virtual-machine:~/env/linux/linux-on-litex-vexriscv$ litex_term --images=images/boot.json /dev/ttyUSB0

__ _ __ _ __

/ / (_) /____ | |/_/

/ /__/ / __/ -_)> <

/____/_/\__/\__/_/|_|

Build your hardware, easily!

(c) Copyright 2012-2024 Enjoy-Digital

(c) Copyright 2007-2015 M-Labs

BIOS CRC passed (4bf52990)

LiteX git sha1: a350d2e90

--=============== SoC ==================--

CPU: VexRiscv SMP-LINUX @ 100MHz

BUS: wishbone 32-bit @ 4GiB

CSR: 32-bit data

ROM: 64.0KiB

SRAM: 6.0KiB

FLASH: 16.0MiB

SDRAM: 256.0MiB 16-bit @ 800MT/s (CL-7 CWL-5)

MAIN-RAM: 256.0MiB

--========== Initialization ============--

Initializing SDRAM @0x40000000...

Switching SDRAM to software control.

Read leveling:

m0, b00: |00000000000000000000000000000000| delays: -

m0, b01: |00000000000000000000000000000000| delays: -

m0, b02: |11111111000000000000000000000000| delays: 03+-03

m0, b03: |00000000000111111111111000000000| delays: 16+-05

m0, b04: |00000000000000000000000000001111| delays: 29+-01

m0, b05: |00000000000000000000000000000000| delays: -

m0, b06: |00000000000000000000000000000000| delays: -

m0, b07: |00000000000000000000000000000000| delays: -

best: m0, b03 delays: 16+-05

m1, b00: |00000000000000000000000000000000| delays: -

m1, b01: |00000000000000000000000000000000| delays: -

m1, b02: |11111111100000000000000000000000| delays: 04+-04

m1, b03: |00000000000111111111111110000000| delays: 18+-06

m1, b04: |00000000000000000000000000011111| delays: 29+-01

m1, b05: |00000000000000000000000000000000| delays: -

m1, b06: |00000000000000000000000000000000| delays: -

m1, b07: |00000000000000000000000000000000| delays: -

best: m1, b03 delays: 17+-06

Switching SDRAM to hardware control.

Memtest at 0x40000000 (2.0MiB)...

Write: 0x40000000-0x40200000 2.0MiB

Read: 0x40000000-0x40200000 2.0MiB

Memtest OK

Memspeed at 0x40000000 (Sequential, 2.0MiB)...

Write speed: 161.1MiB/s

Read speed: 77.8MiB/s

Initializing mx25l12835f SPI Flash @0x01000000...

SPI Flash clk configured to 50 MHz

Memspeed at 0x1000000 (Sequential, 4.0KiB)...

Read speed: 5.0MiB/s

Memspeed at 0x1000000 (Random, 4.0KiB)...

Read speed: 1.8MiB/s

--============== Boot ==================--

Booting from serial...

Press Q or ESC to abort boot completely.

sL5DdSMmkekro

[LITEX-TERM] Received firmware download request from the device.

[LITEX-TERM] Uploading images/Image to 0x40000000 (7531468 bytes)...

[LITEX-TERM] Upload calibration... (inter-frame: 10.00us, length: 64)

[LITEX-TERM] Upload complete (9.9KB/s).

[LITEX-TERM] Uploading images/rv32.dtb to 0x40ef0000 (2367 bytes)...

[LITEX-TERM] Upload calibration... (inter-frame: 10.00us, length: 64)

[LITEX-TERM] Upload complete (9.8KB/s).

[LITEX-TERM] Uploading images/rootfs.cpio to 0x41000000 (3781632 bytes)...

[LITEX-TERM] Upload calibration... (inter-frame: 10.00us, length: 64)

[LITEX-TERM] Upload complete (9.9KB/s).

[LITEX-TERM] Uploading images/opensbi.bin to 0x40f00000 (53640 bytes)...

[LITEX-TERM] Upload calibration... (inter-frame: 10.00us, length: 64)

[LITEX-TERM] Upload complete (9.9KB/s).

[LITEX-TERM] Booting the device.

[LITEX-TERM] Done.

Executing booted program at 0x40f00000

--============= Liftoff! ===============--

OpenSBI v0.8-1-gecf7701

____ _____ ____ _____

/ __ \ / ____| _ \_ _|

| | | |_ __ ___ _ __ | (___ | |_) || |

| | | | '_ \ / _ \ '_ \ \___ \| _ < | |

| |__| | |_) | __/ | | |____) | |_) || |_

\____/| .__/ \___|_| |_|_____/|____/_____|

| |

|_|

Platform Name : LiteX / VexRiscv-SMP

Platform Features : timer,mfdeleg

Platform HART Count : 8

Boot HART ID : 0

Boot HART ISA : rv32imasu

BOOT HART Features : pmp,time

BOOT HART PMP Count : 16

Firmware Base : 0x40f00000

Firmware Size : 124 KB

Runtime SBI Version : 0.2

MIDELEG : 0x00000222

MEDELEG : 0x0000b109

[ 0.000000] Linux version 5.14.0 (florent@panda) (riscv32-buildroot-linux-gnu-gcc.br_real (Buildroot 2021.08-381-g279167ee8d) 10.3.0, GNU ld (GNU Binutils) 2.36.1) #1 SMP Tue Sep 21 12:57:31 CEST 2021

[ 0.000000] Machine model: atest2

[ 0.000000] earlycon: liteuart0 at I/O port 0x0 (options '')

[ 0.000000] Malformed early option 'console'

[ 0.000000] earlycon: liteuart0 at MMIO 0xf0001000 (options '')

[ 0.000000] printk: bootconsole [liteuart0] enabled

[ 0.000000] Zone ranges:

[ 0.000000] Normal [mem 0x0000000040000000-0x000000004fffffff]

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040000000-0x000000004fffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040000000-0x000000004fffffff]

[ 0.000000] SBI specification v0.2 detected

[ 0.000000] SBI implementation ID=0x1 Version=0x8

[ 0.000000] SBI TIME extension detected

[ 0.000000] SBI IPI extension detected

[ 0.000000] SBI RFENCE extension detected

[ 0.000000] SBI v0.2 HSM extension detected

[ 0.000000] riscv: ISA extensions aimp

[ 0.000000] riscv: ELF capabilities aim

[ 0.000000] percpu: Embedded 8 pages/cpu s11340 r0 d21428 u32768

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 65024

[ 0.000000] Kernel command line: console=liteuart earlycon=liteuart,0xf0001000 rootwait root=/dev/ram0

[ 0.000000] Dentry cache hash table entries: 32768 (order: 5, 131072 bytes, linear)

[ 0.000000] Inode-cache hash table entries: 16384 (order: 4, 65536 bytes, linear)

[ 0.000000] Sorting __ex_table...

[ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off

[ 0.000000] Memory: 243572K/262144K available (5685K kernel code, 572K rwdata, 883K rodata, 209K init, 221K bss, 18572K reserved, 0K cma-reserved)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[ 0.000000] rcu: Hierarchical RCU implementation.

[ 0.000000] rcu: RCU restricting CPUs from NR_CPUS=8 to nr_cpu_ids=1.

[ 0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 25 jiffies.

[ 0.000000] rcu: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=1

[ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0

[ 0.000000] riscv-intc: 32 local interrupts mapped

[ 0.000000] plic: interrupt-controller@f0c00000: mapped 32 interrupts with 1 handlers for 2 contexts.

[ 0.000000] random: get_random_bytes called from start_kernel+0x4ac/0x63c with crng_init=0

[ 0.000000] riscv_timer_init_dt: Registering clocksource cpuid [0] hartid [0]

[ 0.000000] clocksource: riscv_clocksource: mask: 0xffffffffffffffff max_cycles: 0x171024e7e0, max_idle_ns: 440795205315 ns

[ 0.000018] sched_clock: 64 bits at 100MHz, resolution 10ns, wraps every 4398046511100ns

[ 0.009281] Console: colour dummy device 80x25

[ 0.013440] Calibrating delay loop (skipped), value calculated using timer frequency.. 200.00 BogoMIPS (lpj=400000)

[ 0.024157] pid_max: default: 32768 minimum: 301

[ 0.031689] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes, linear)

[ 0.038771] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes, linear)

[ 0.067965] ASID allocator using 9 bits (512 entries)

[ 0.074355] rcu: Hierarchical SRCU implementation.

[ 0.083859] smp: Bringing up secondary CPUs ...

[ 0.087748] smp: Brought up 1 node, 1 CPU

[ 0.097041] devtmpfs: initialized

[ 0.127044] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns

[ 0.136905] futex hash table entries: 256 (order: 2, 16384 bytes, linear)

[ 0.150759] NET: Registered PF_NETLINK/PF_ROUTE protocol family

[ 0.318408] pps_core: LinuxPPS API ver. 1 registered

[ 0.322701] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.332176] PTP clock support registered

[ 0.338861] FPGA manager framework

[ 0.355403] clocksource: Switched to clocksource riscv_clocksource

[ 0.528812] NET: Registered PF_INET protocol family

[ 0.534493] IP idents hash table entries: 4096 (order: 3, 32768 bytes, linear)

[ 0.550380] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 6144 bytes, linear)

[ 0.559490] TCP established hash table entries: 2048 (order: 1, 8192 bytes, linear)

[ 0.567615] TCP bind hash table entries: 2048 (order: 2, 16384 bytes, linear)

[ 0.574745] TCP: Hash tables configured (established 2048 bind 2048)

[ 0.581661] UDP hash table entries: 256 (order: 1, 8192 bytes, linear)

[ 0.588252] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes, linear)

[ 0.613813] Unpacking initramfs...

[ 0.708721] workingset: timestamp_bits=30 max_order=16 bucket_order=0

[ 0.947690] io scheduler mq-deadline registered

[ 0.951620] io scheduler kyber registered

[ 1.255386] LiteX SoC Controller driver initialized

[ 2.006172] Initramfs unpacking failed: invalid magic at start of compressed archive

[ 2.076720] Freeing initrd memory: 8192K

[ 2.765019] f0001000.serial: ttyLXU0 at MMIO 0x0 (irq = 0, base_baud = 0) is a liteuart

[ 2.773234] printk: console [liteuart0] enabled

[ 2.773234] printk: console [liteuart0] enabled

[ 2.782024] printk: bootconsole [liteuart0] disabled

[ 2.782024] printk: bootconsole [liteuart0] disabled

[ 2.814827] i2c_dev: i2c /dev entries driver

[ 2.859326] NET: Registered PF_INET6 protocol family

[ 2.877381] Segment Routing with IPv6

[ 2.880761] In-situ OAM (IOAM) with IPv6

[ 2.885356] sit: IPv6, IPv4 and MPLS over IPv4 tunneling driver

[ 2.904338] NET: Registered PF_PACKET protocol family

[ 2.920176] Freeing unused kernel image (initmem) memory: 204K

[ 2.925657] Kernel memory protection not selected by kernel config.

[ 2.932153] Run /init as init process

Starting syslogd: OK

Starting klogd: OK

Running sysctl: OK

Saving random seed: [ 5.226659] random: dd: uninitialized urandom read (512 bytes read)

OK

Starting network: OK

Welcome to Buildroot

buildroot login: acx

Password:

Login incorrect

login[69]: invalid password for 'UNKNOWN' on 'console'

buildroot login: root

__ _

/ / (_)__ __ ____ __

/ /__/ / _ \/ // /\ \ /

/____/_/_//_/\_,_//_\_\

/ _ \/ _ \

__ _ __ _ _\___/_//_/ ___ _

/ / (_) /____ | |/_/__| | / /____ __ / _ \(_)__ _____ __

/ /__/ / __/ -_)> </___/ |/ / -_) \ // , _/ (_-</ __/ |/ /

/____/_/\__/\__/_/|_|____|___/\__/_\_\/_/|_/_/___/\__/|___/

/ __/ |/ / _ \

_\ \/ /|_/ / ___/

/___/_/ /_/_/

32-bit RISC-V Linux running on LiteX / VexRiscv-SMP.

login[69]: root login on 'console'

root@buildroot:~#

现在已经启动了linux系统。

四、代码

通过百度网盘分享的文件:acx720-litex.7z

链接:https://pan.baidu.com/s/1nU77wU95s9dZP7dJCO01oA?pwd=c946

提取码:c946

1466

1466

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?