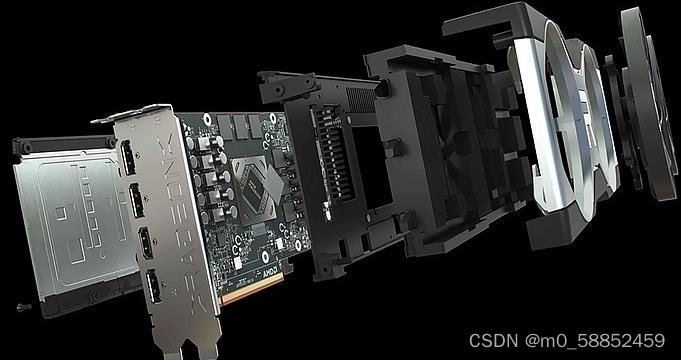

RX 7900 XT,将使用Navi 31旗舰核心,流处理器可能会多达15360个,同时配备16GB 256bit GDDR6显存、256MB 3D无限缓存,核心频率可达2.5GHz。RX 7900 XT怎么样这些点很重要http://www.adiannao.cn/dy

Navi 32、Navi 33核心显存容量基本和前代核心保持一致,但是核心频率将有明显的提升,Navi 32的频率高达2.8GHz,Navi 32核心的频率更是冲到了3.0GHz。RX 7000系列显卡在流处理器数量、核心频率方面有明显的提升,图形处理能力也将会更加出色。

AMD即将推出的RX7900XT显卡采用Navi31旗舰核心,预计搭载15360个流处理器及16GB GDDR6显存,核心频率可达2.5GHz。Navi32、Navi33核心频率分别高达2.8GHz和3.0GHz,整体图形处理能力将显著提升。

AMD即将推出的RX7900XT显卡采用Navi31旗舰核心,预计搭载15360个流处理器及16GB GDDR6显存,核心频率可达2.5GHz。Navi32、Navi33核心频率分别高达2.8GHz和3.0GHz,整体图形处理能力将显著提升。

1409

1409

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?