第一章

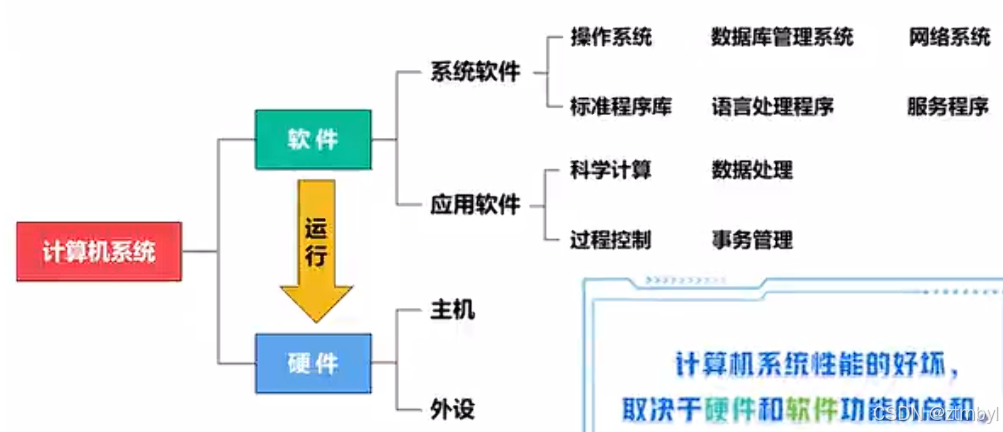

一、计算机系统的组成

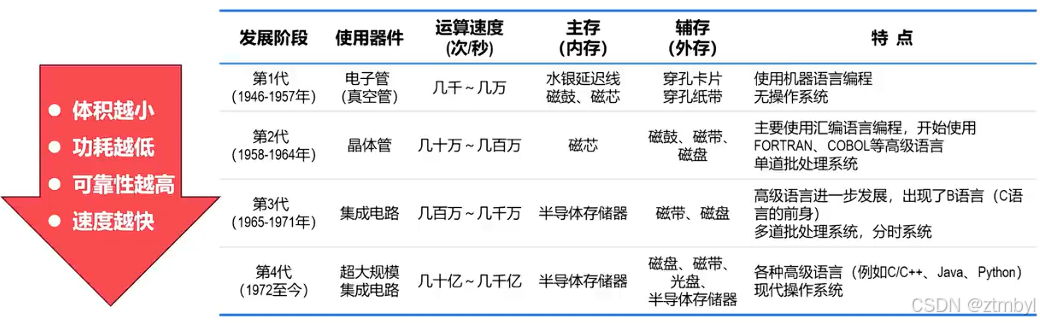

二、计算机发展

- 硬件发展

电子管(真空管)——晶体管——集成电路——超大规模集成电路

- 软件发展

机器语言——汇编语言——高级语言——面向对象

- 摩尔定律:

集成电路上可容纳的晶体管数目大约每经过18到24个月便会增加一倍。换言之,处理器的性能大约每两年翻一倍,同时价格下降为之前的一半。

三、计算机硬件

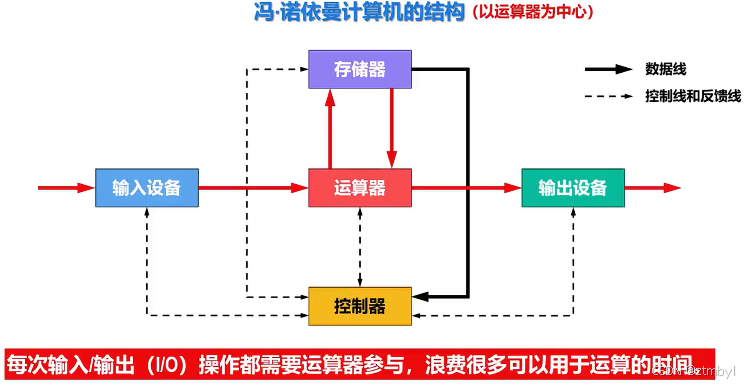

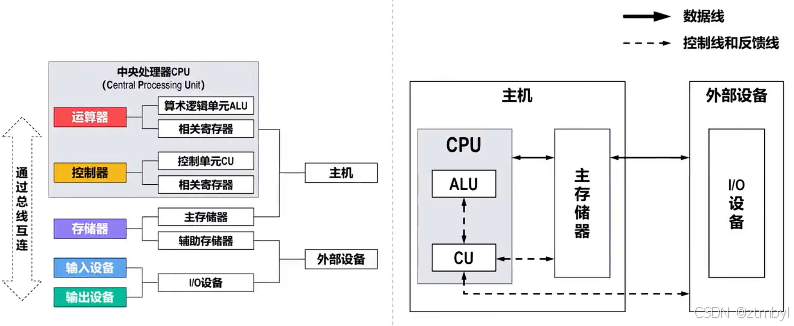

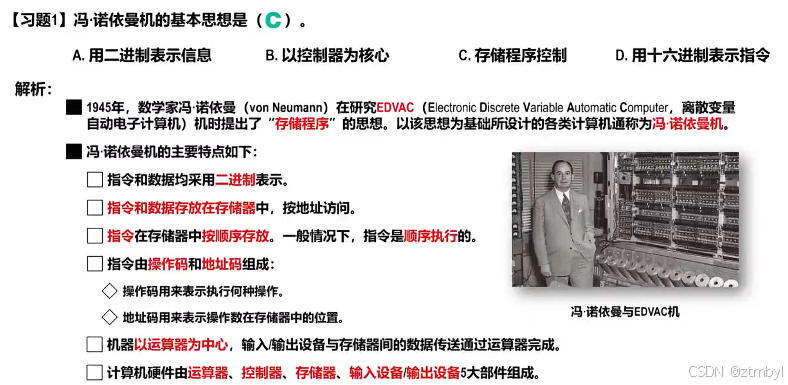

1 冯诺依曼计算机的结构

主要思想:研制一台可以存储程序的新机器

主要特点:

——构成程序的指令和数据均采用二进制表示。

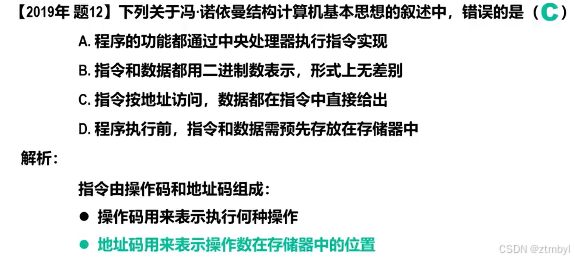

——指令和数据存放在存储器中,按地址访问。

——指令在存储器中按顺序存放。一般情况下,指令是顺序执行的

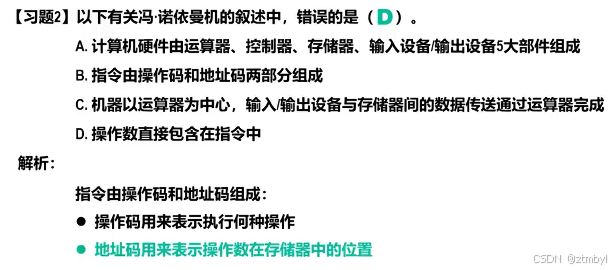

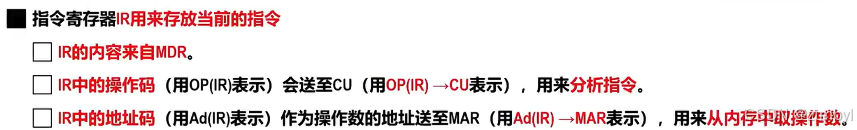

——指令由操作码和地址码组成:

操作码用来表示执行何种操作。

地址码用来表示操作数在存储器中的位置。

——机器以运算器为中心,输入输出设备与存储器间的数据传送通过运算器完成。

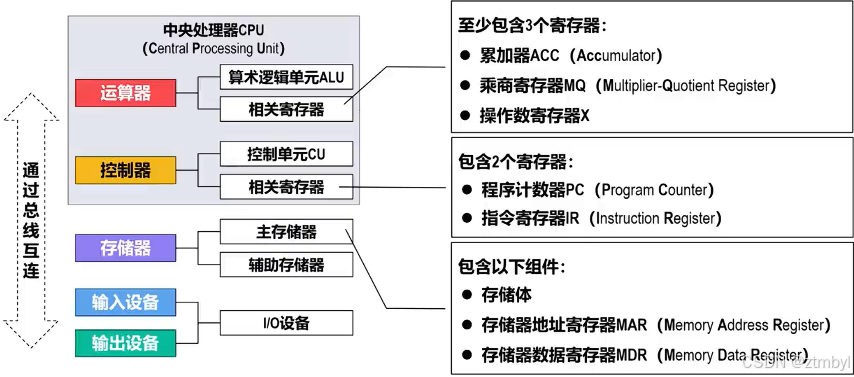

——计算机硬件由运算器、控制器、存储器、输入设备输出设备5大部件组成。

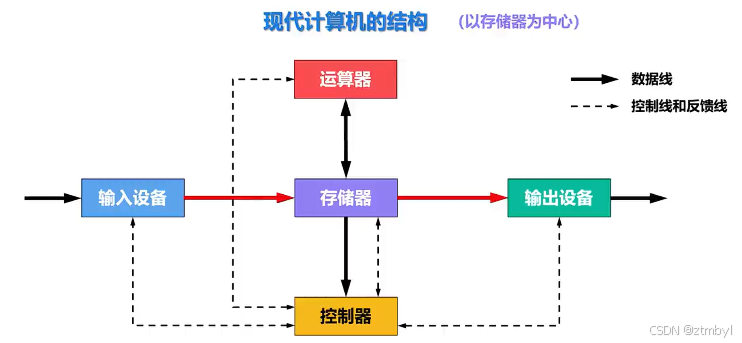

2 现代计算机的结构

可以让输入输出设备直接与存储器交换数据,以提高整体效率

- 输入设备:将人们熟悉的信息形式转换为计算机能够识别的信息形式,常见的有键盘、鼠标、扫描仪、摄像头等。

- 输出设备:将计算机运算结果转换为人们熟悉的信息形式,常见的有显示器、打印机等。

- 主存储器:主存储器:用于存放程序和数据可以直接与CPU交换信息,又称为内存储器,简称内存或主存。

- 辅助存储器:铺助存储器:用于帮助主存存储更多的信息。又称为外部存储器,简称外存或辅存。辅存中的信息必须调入主存后,才能被CPU访问。

- 运算器:核心为算术逻辑单元ALU(Arithmetic LogicUnit),主要功能如下:

算术运算:加、减、乘、除

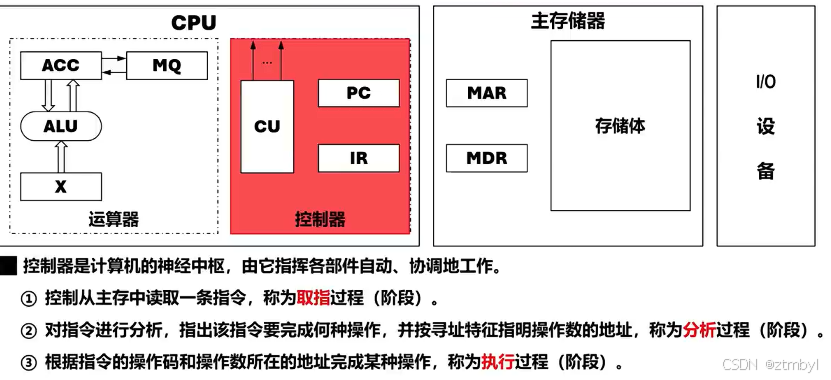

逻辑运算:与、或、非、异或等- 控制器:核心为控制单元CU(Control Unit),主要功能如下:

用于解释存储器中的指令,并发出各种操作命令来执行指令。

VO设备也受CU控制,用于完成相应的输入输出操作。

四、计算机软件

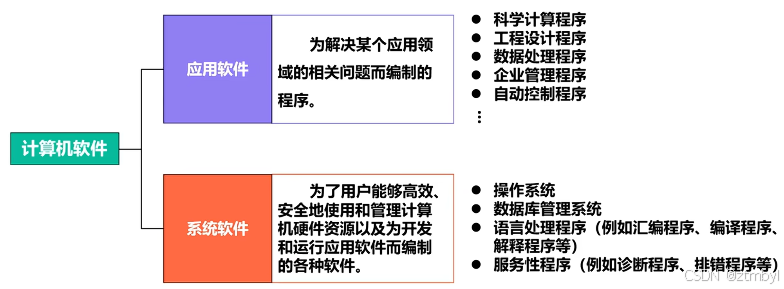

1 分类

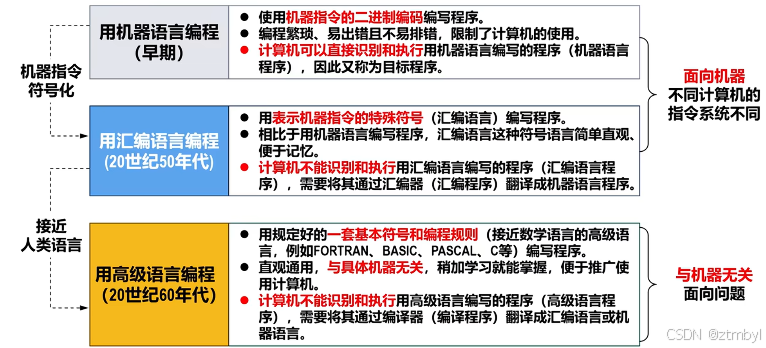

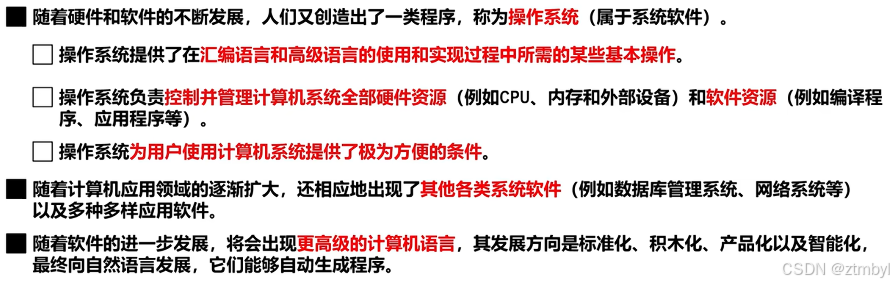

2 发展

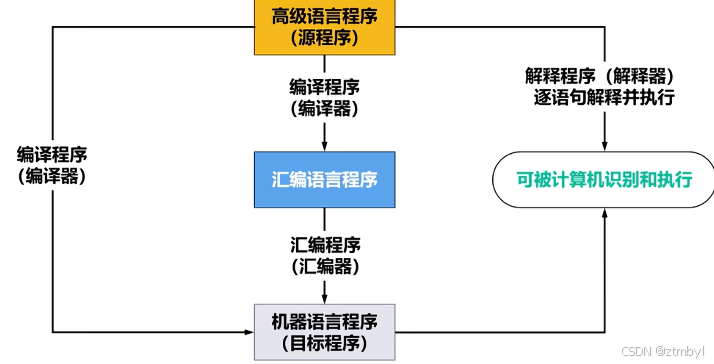

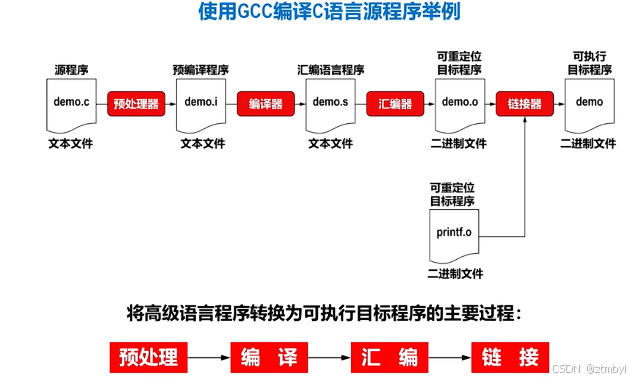

3 程序设计语言与语言翻译程序的关系

编译程序、解释程序以及汇编程序都属于翻译程序。

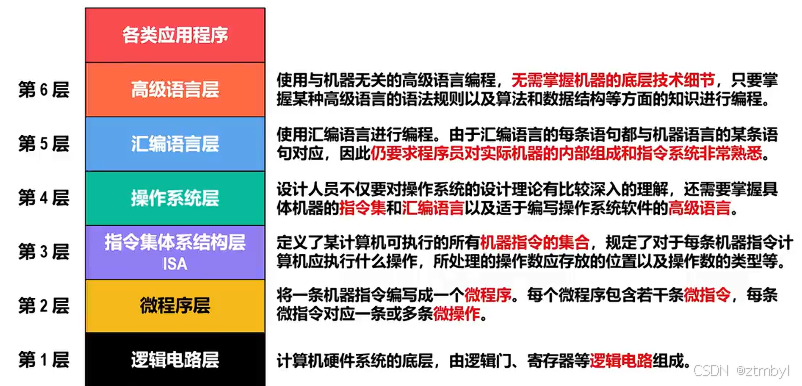

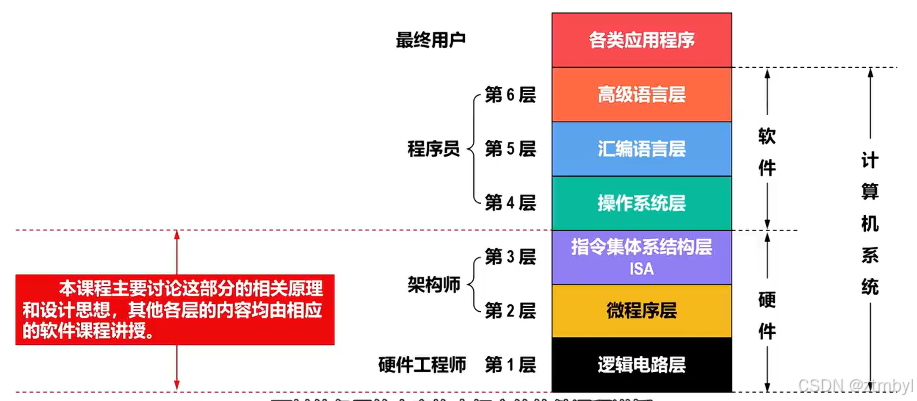

五、计算机系统的结构

1 分层思想

计算机是一个非常复杂的系统,为了简化对计算机系统的研究和实现,可采用分层思想将计算机系统划分成一个层次结构的系统。

——系统中的每一层都向其上层提供一个简洁和抽象的接口。

——每一层的实现细节对其上层而言都是“看不见”的,也就是透明的。

计算机解决问题的过程就是层次结构中的各层逐层转换的过程。

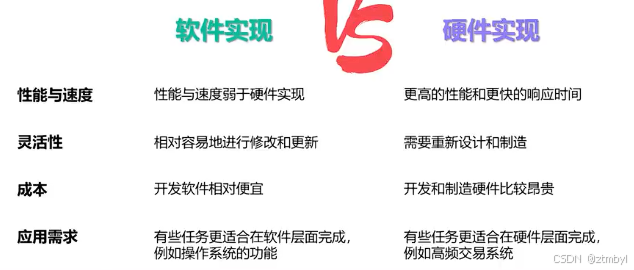

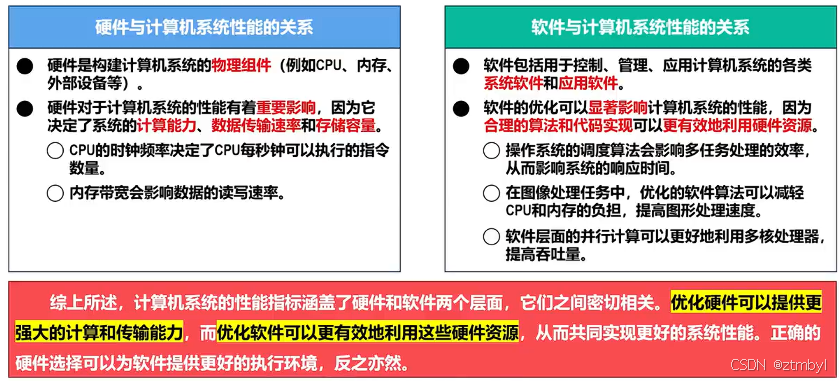

- 软件与硬件的逻辑功能等价性 :

在特定条件下,用软件实现的逻辑功能也可以通过硬件电路来实现,反之亦然。

对于一些特定的计算或控制任务,可以选择将其使用软件编程来实现,也可以选择设计专用硬件电路来实现,而两者的结果将在功能上等效。

软件和硬件的逻辑功能等价性是计算机科学中的一个重要概念,也是计算机体系结构和工程中的基本原则之一。

当选择在软件层面实现某些逻辑功能时,这通常意味着使用通用处理器(例如CPU)来执行程序;而当选择在硬件层面实现这些逻辑功能时,这通常意味着使用专用的硬件电路,例如现场可编程门阵列FPGA(Field Programmable Gate Array)或专用集成电路ASIC(Application Specific Integrated Circuit)技术。

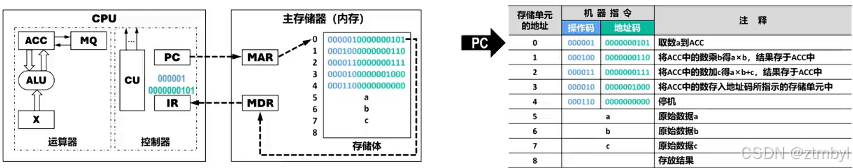

六、基本工作原理

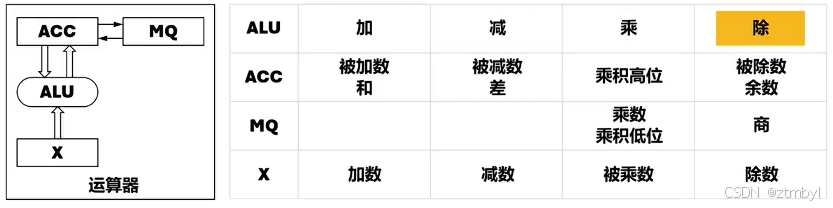

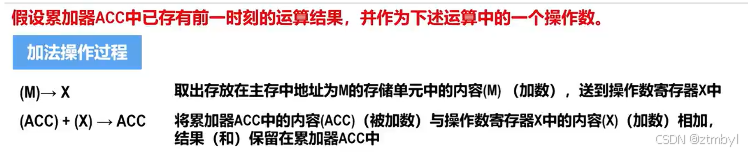

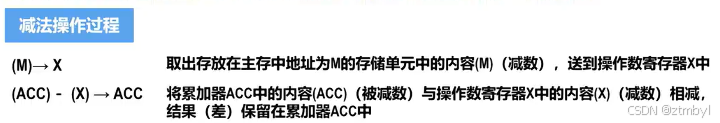

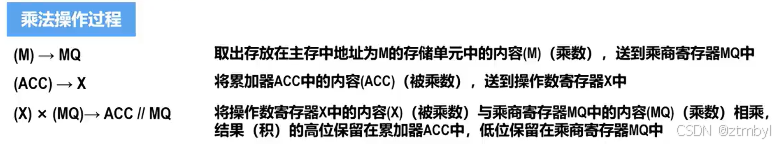

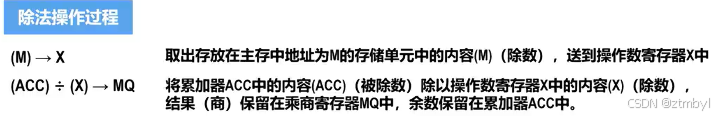

1 运算器

M表示主存储器中某个存储单元的地址

(M)表示地址为M的存储单元中的内容

ACC表示累加器

(ACC)表示累加器中的内容

MQ表示乘商寄存器

(MQ)表示乘商寄存器中的内容

X表示操作数寄存器

(X)表示操作数寄存器中的内容

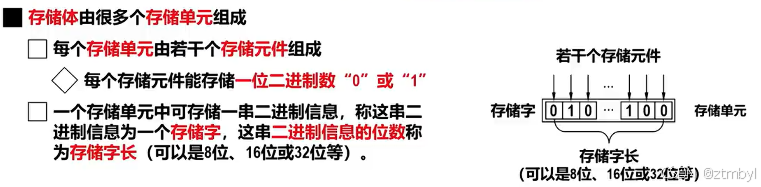

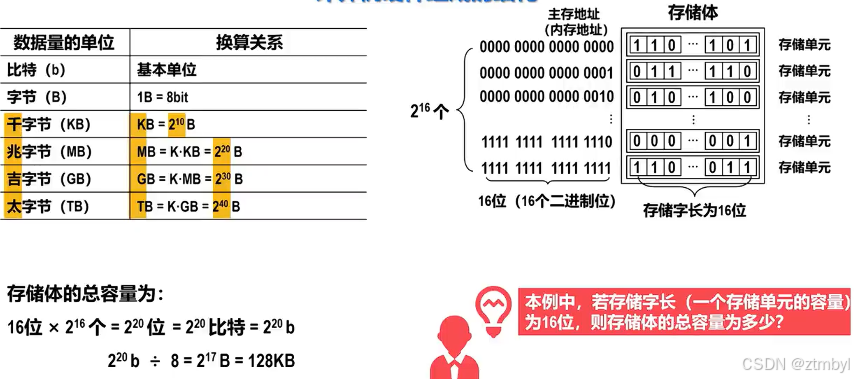

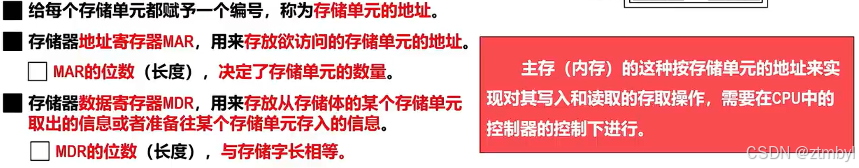

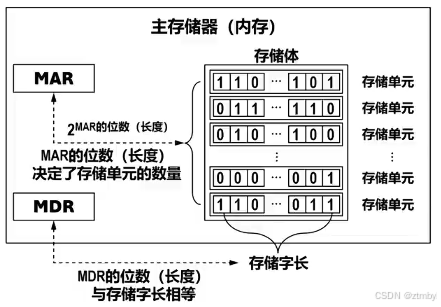

2 主存储器

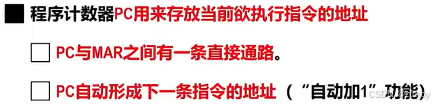

3 控制器

![]()

4 机器指令简介

具体过程:

初始化:(PC)=0,指向内存中的编号为0的存储单元,该存储单元的内容是第一条机器指令

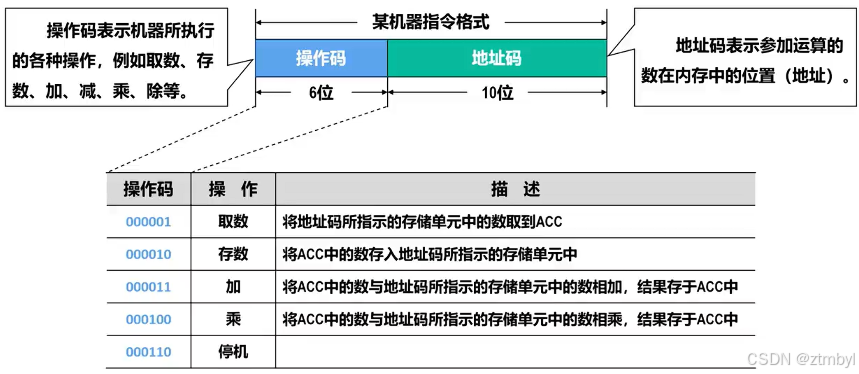

对第一条指令进行取指:

①控制器将PC的内容送至内存的MAR(用(PC)→MAR表示)对内存进行寻址,并命令内存做读操作,此时所寻址的存储单元(0号存储单元)的内容“0000010000000101”被送入MDR内。

②将MDR的内容传送至控制器的IR(用(MDR)→R表示)对第一条指令进行分析:

①将R中保存的指令的操作码送至CU进行分析(用0PI)→CU),操作码“000001”为取数指令。对第一条指令进行执行:

将R中保存的指令的地址码送至MAR(用AdR)一→MAR)对内存进行寻址,并命令内存做读操作,此时所寻址的存储单元(“0000000101”号存储单元,即5号存储单元)的内容“a”被送入MDR内。

②将MDR的内容传送至运算器的ACC(用MDR)→ACC表示)

(PC)=1,指向内存中的编号为1的存储单元,该存储单元的内容是第二条机器指令

对第二条指令进行取指:

①控制器将PC的内容送至内存的MAR(用(PC)→MAR表示)对内存进行寻址,并命令内存做读操作,此时所寻址的存储单元(1号存储单元)的内容“0001000000000110”被送入MDR内。

②将MDR的内容传送至控制器的R(用(MDR)→IR表示)对第二条指令进行分析:

①将R中保存的指令的操作码送至CU进行分析(用0PIR)→CU),操作码“O00100”为乘法指令。对第二条指令进行执行:

①将R中保存的指令的地址码送至MAR(用AdIR)→MAR)

对内存进行寻址,并命令内存做读操作,此时所寻址的存储单元(“0000000110”号存储单元,即6号存储单元)的内容“b”被送入MDR内。

②将MDR的内容传送至运算器的MQ(用(MDR)→MQ表示)。

BCU向ALU发送乘法操作命令,并把运算结果(a×b)的高位存放在ACC中、低位存放在MQ中。

随着硬件技术的发展,内存都制成大规模集成电路芯片,而将MAR和MDR集成到了CPU芯片中。

七、计算机系统的性能指标

1 硬件相关指标

1.1 基本性能指标

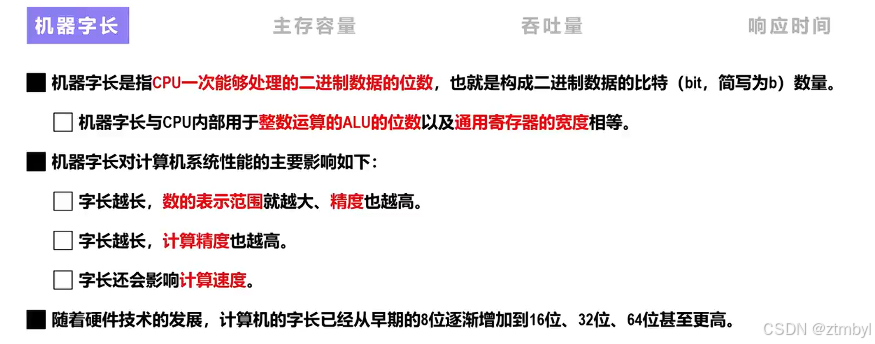

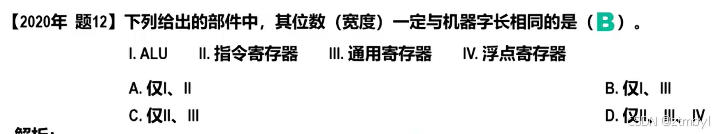

1)机器字长

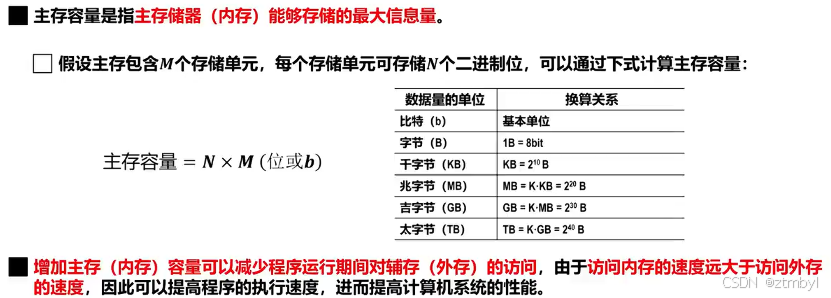

2)主存容量

3)吞吐量

吞吐量是指计算机系统在单位时间内能够处理的信息量。

影响吞吐量的主要因素如下:

- CPU的处理能力。

- 内存(主存)的访问速度。

- 外存(辅存,例如硬盘)的访问速度。

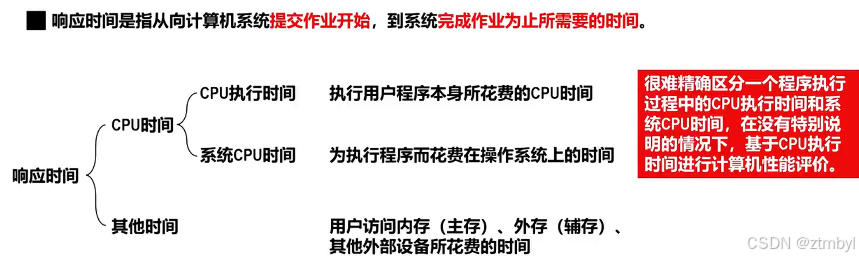

4)响应时间

1.2 与运算速度相关的性能指标

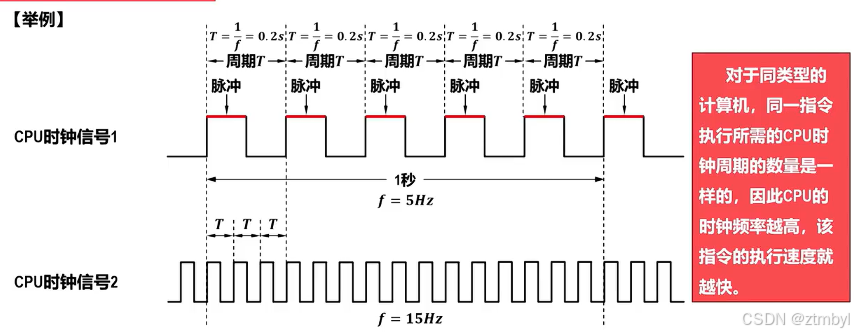

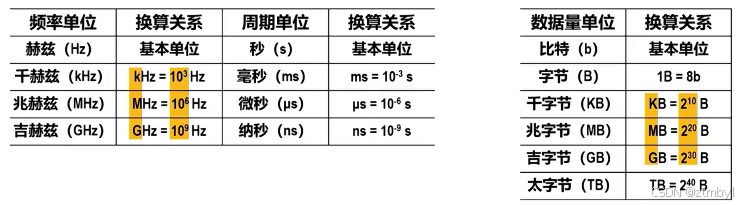

1)CPU时钟频率与时钟周期

CPU时钟信号是一个基本定时信号,它是一种固定频率的脉冲信号,用于驱动计算机内部各组件协调工作。这种脉冲信号的频率被称为CPU时钟频率(Clock Rate),基本单位为赫兹(Hz).

CPU时钟周期(Clock Cycle或Clock Tick,也可简称为clock或tick)是CPU时钟频率的倒数,基本单位为秒(s)。

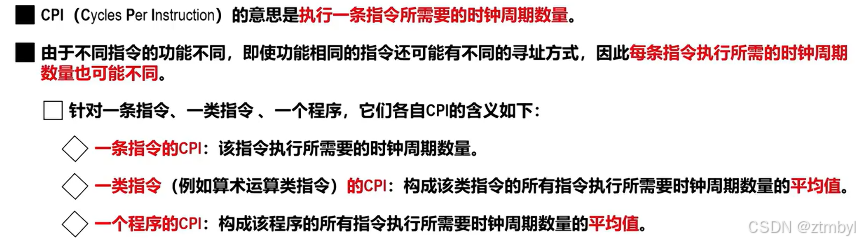

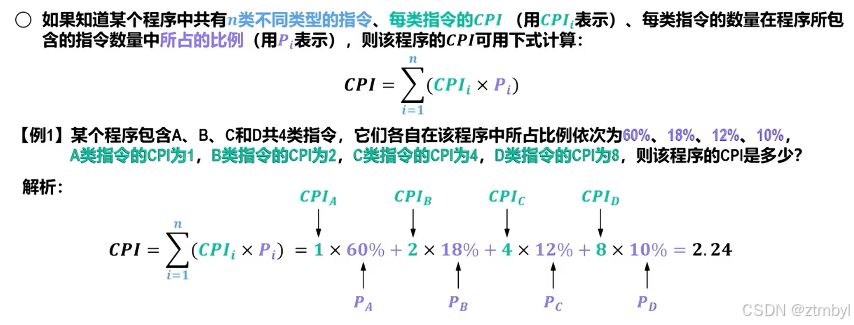

2)CPI

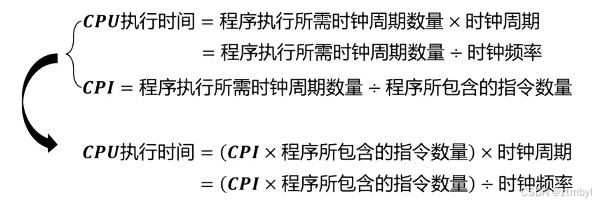

CPI=程序执行所需时钟周期数量÷程序所包含的指令数量

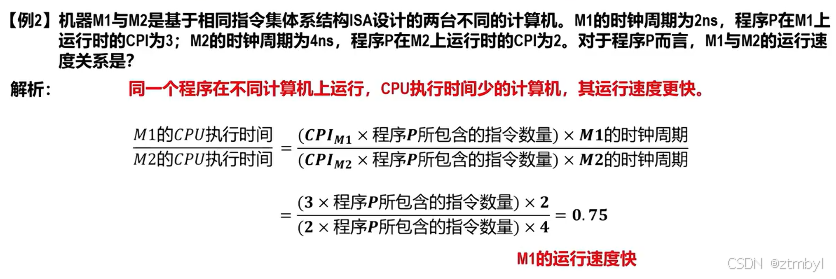

3)CPU执行时间

CPU执行时间是指真正用于用户程序的执行时间,而不包括为执行用户程序而花费在操作系统、访问主存(内存)、访问辅存(外存)、访问外部设备上的时间。

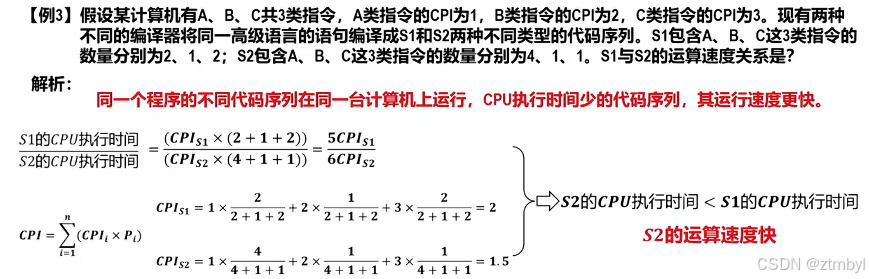

根据本例可以看出:

仅仅通过计算机编译后目标代码中包含的指令数量来评估计算机性能是不准确的。在本例中,尽管S2包含的指令数量(4+1+1=6)比S1(2+1+2=5)多,但是由于S2中CPI小的指令(即CPI为1的A类指令)所占比例(4/6),比S1中CPI小的指令(即CPI为1的A类指令)所占比例(25)高,因此指令数量更多的S2实际上比指令数量较少的S1执行速度更快。

4)IPC(CPI的倒数)

IPC(Instructions Per Cycle)的意思是每个时钟周期能够执行的指令数量。

IPC是CPI的倒数,它与CPU架构、指令集、指令流水线技术等密切相关。

由于指令流水线技术以及多核技术的发展,目前PC的值已经可以大于1。

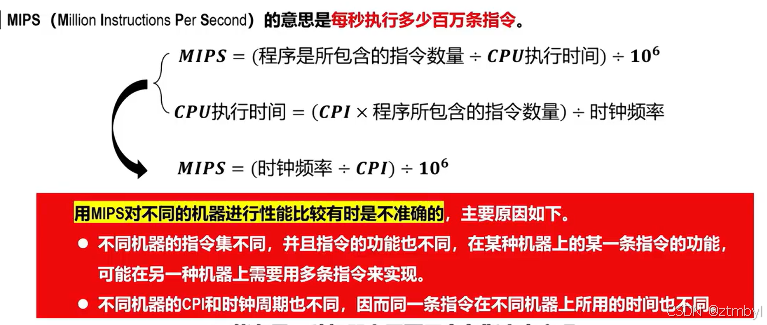

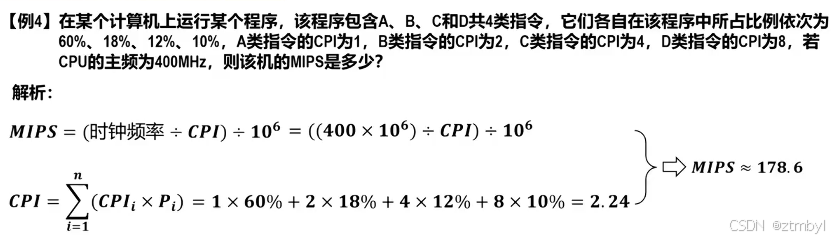

5)MIPS

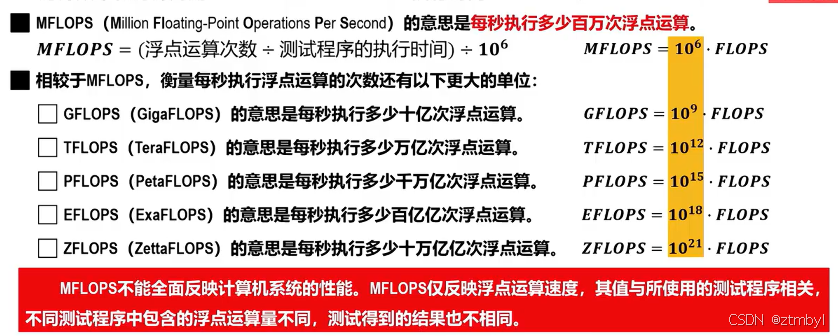

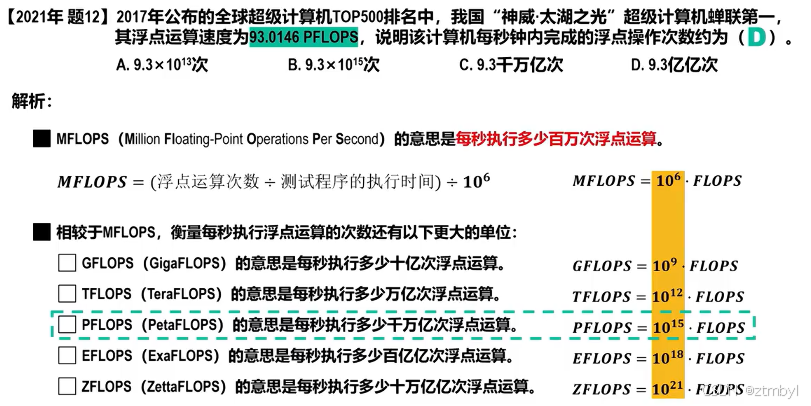

6)MFLOPS

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?