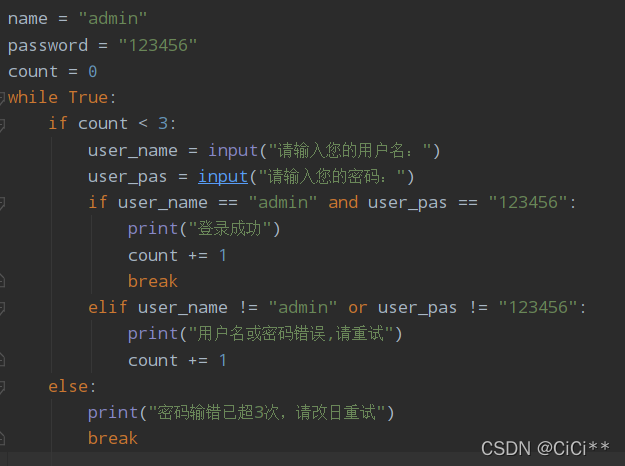

1,线定义两个变量来存储正确的账号、密码,以及输入的次数

2,使用死循环,不断提示用户输入用户名和密码

3,在判断账号密码是否正确前先判断输入次数<3?

如果True,则进行账号、密码的判断

如果False, 则提示超过3次

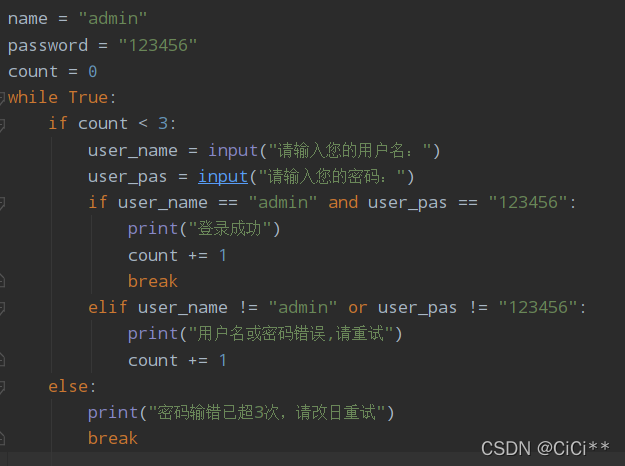

1,线定义两个变量来存储正确的账号、密码,以及输入的次数

2,使用死循环,不断提示用户输入用户名和密码

3,在判断账号密码是否正确前先判断输入次数<3?

如果True,则进行账号、密码的判断

如果False, 则提示超过3次

7271

7271

205

205

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?