在这一章,我们要熟练掌握各种功能门电路的逻辑功能。熟练掌握TTL门电路输入端的负载特性、输入/输出端的电压电流关系特性,会判断各种情况下输入端的逻辑值。熟练掌握集电极开路门的线与结构、三态门工作状态的判断、CMOS传输门工作状态的判断。这些就已经足够了。这一张的内容其实对于IC方向的同学不太重要,注重理解就好。我们的最终目的是将门电路的原理搞清楚,之后快速的将其封装到集成电路中。

首先我们要知道二极管的开关特性是正向导通,反向截止。

主要介绍下cmos管

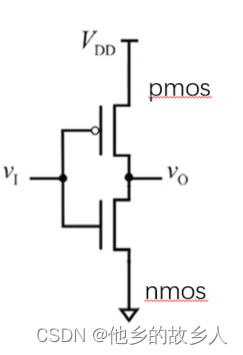

CMOS反相器

整体电路结构是两个互补得mos管,nmos下拉,pmos上拉。当输入高电平时,pmos截止,nmos导通,实现下拉,输出低电平;当输入低电平得时候,nmos截止,pmos导通,实现上拉,输出高电平。整体实现得逻辑是输入一个变量,输出其反变量的功能。

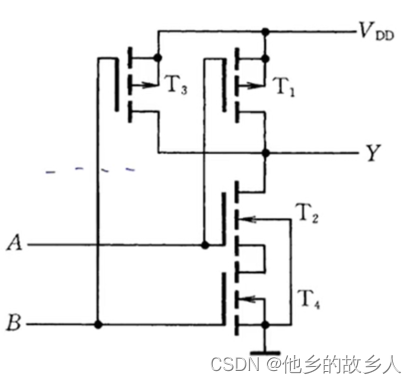

CMOS与非门

当输入的两个都是高电平的时候,两个nmos才能被导通,此时输出会实现下拉至0,即Y=(AB)'实现与非门;当任意一个输入为低电平的时候,pmos就会导通,就会输出高电平即Y=A'+B'实现与非门。我们可以看到,CMOS与非门的结构是上面两个pmos并联,下面两个nmos串联,即上并下串是与非。

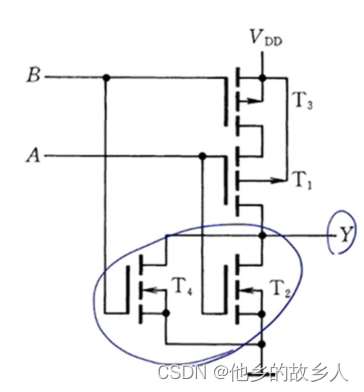

CMOS或非门

接下来我们看下CMOS或非门,从结构上我们可以看出,两个pmos管是串联的,下面两个nmos是并联的。即上串下并是或非。只有当两个输入都是低电平的时候,才能使的pmos管导通,输出高电平,只要有任意一个输入时高电平,那么就会让nmos管导通,输出低电平。

那么该如何应用这些cmos管来完成其他逻辑功能的cmos门电路的设计呢?下面我举个例子:

Y=(A(B+C))'看到这个式子我们知道,Y'=A(B+C).其逻辑输出为0时比较简单,因此我们就从下拉部分开始,让B,C两个nmos进行并联,再和A进行串联,完成下拉部分的设计,再对称性的设计上拉部分(即串变成并,并变成串,将B,C进行串联在和A进行并联就行。)

OD门

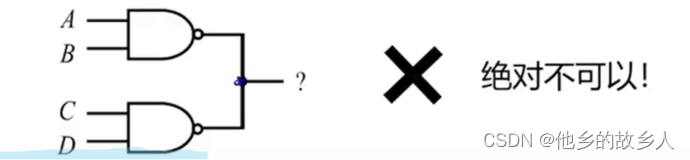

如果我们直接将两个门电路输出直接相与,这是万万不可以的。假设上面的输出是1,则pmos管导通,而下面的输出是0,则nmos导通,由于开关管的导通电阻很小近短路,则电流非常大,会烧坏电路。

为了解决这个问题,引入OD门,他的原理是将原来本互补的cmos反相器的上拉策的pmos去掉,这样再输入为高电平的时候会让nmos导通,是先下拉,而输入为低电平的时候,电路表现为高阻的状态。OD门的重要功能是可以实现线与。

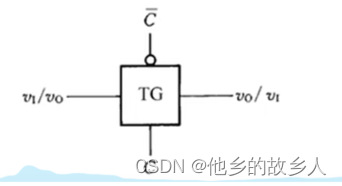

cmos传输门

原理很简单,当C=0,C'=1时,传输门截止(高阻态);当C=1,C'=0的时候,传输门导通,信号通过。

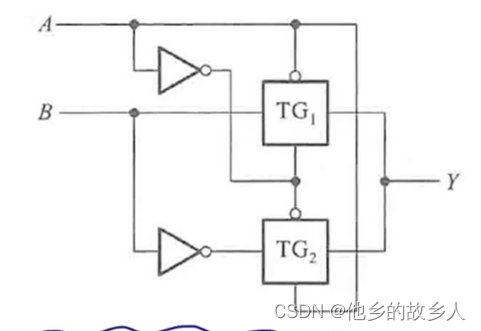

通过传输门,我们可以设计出异或门,当A=1时,TG1截止,TG2导通,Y=B';当B=1时,TG1导通,TG2截止,Y=A'.即Y=AB'+A'B

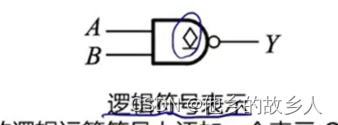

三态门

原理较为简单:当EN'=0时,电路正常工作,实现反相器的功能;当EN'=1时,电路呈现出高阻态

我们要注意这个小圆圈,他代表低电平有效,如果没有这个小圆圈的话,则EN‘=1,电路正常工作

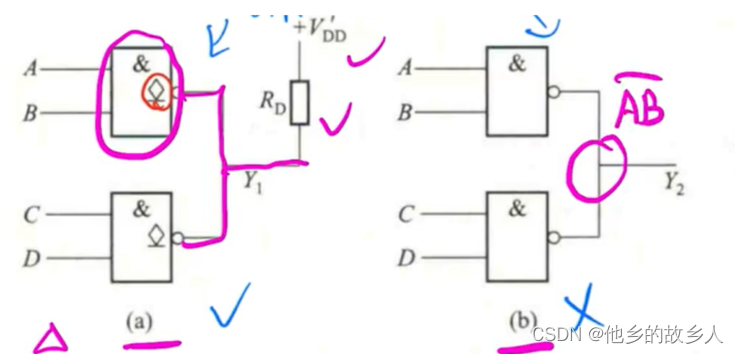

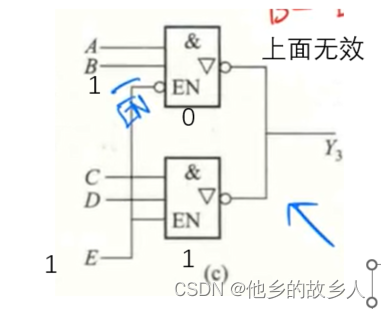

下面简单做几个练习题,判断下列电路能否正常工作

对于a来说,这是两个od门串联实现线与功能,可行。

对于B来说,这是两个普通的与非门,不能实现线与,所以不可行。

这是两个三态门由于上半部分时低电平有效,下半部分时高电平有效,因此可行

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?