新建工程文件:

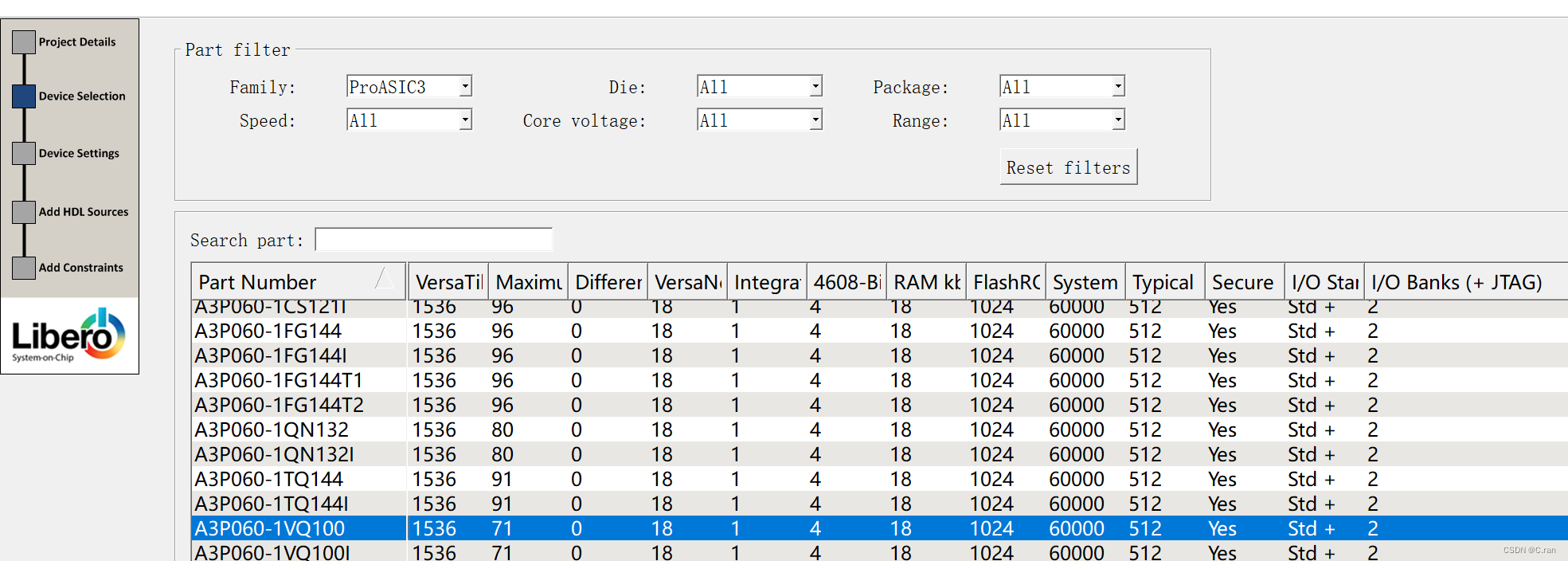

点击New,选择存放的文件夹路径中也不能有中文!!!选好后来到芯片选择,本课程使用的是A3P060-VQ100,具体属性如下,别选错了就行:

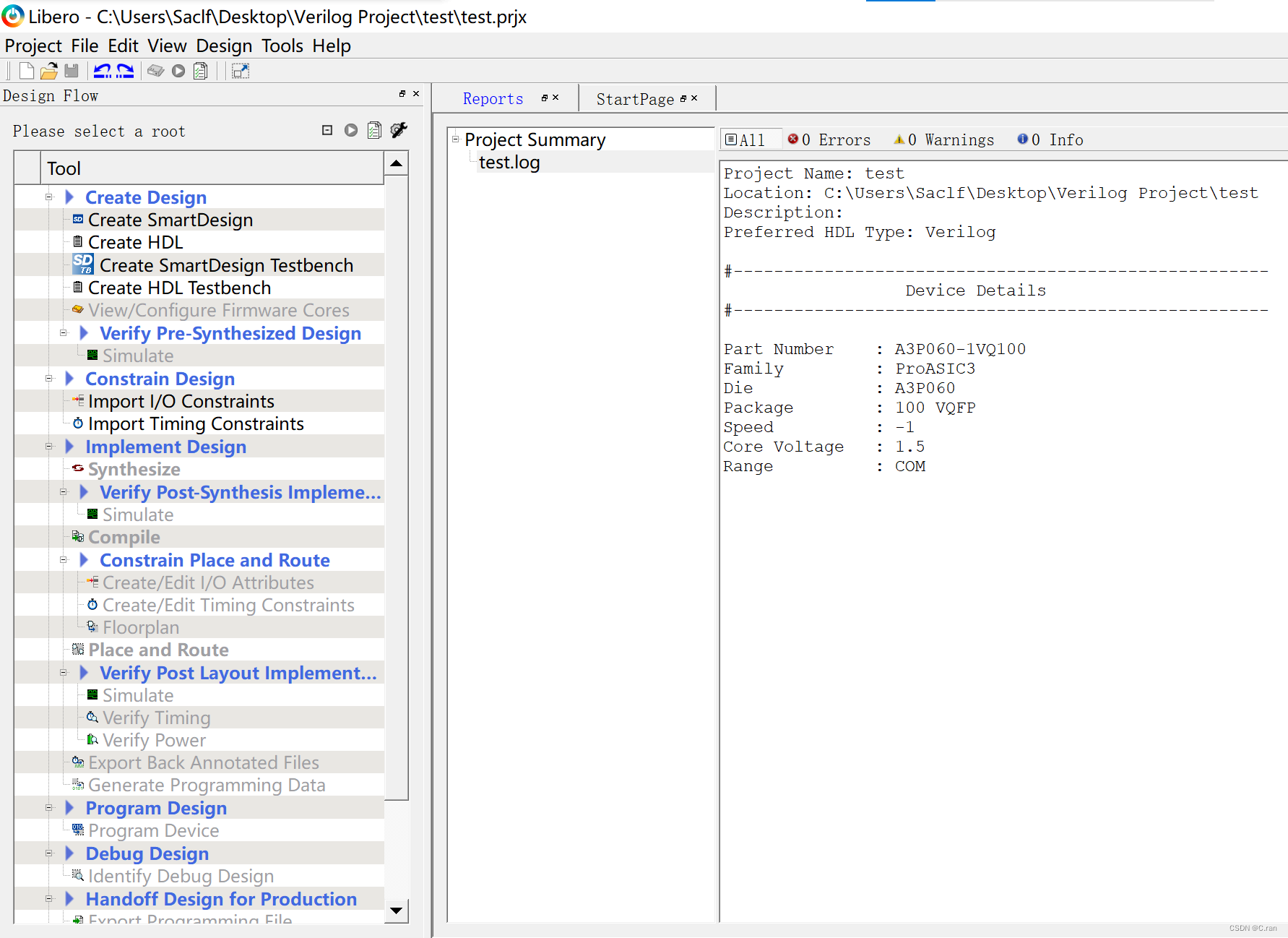

选好后,点击Finish即可。

双击Create HDL命令,产生一个硬件语言描述的新文件,可以不勾选下方选项。

在区域中敲好代码后,点击Check HDL File

如果有问题就根据报错修改问题,需要注意的是,比如出错行在5,那么就要检查5行分号前的语句有没有问题。比如下述问题:

对于5行分号前的内容进行检查,就可以发现是第四行没有分号,分号代表一个语句,因此要整条语句进行检查。

然后需要用测试平台进行测试,选择Create HDL Testbench命令,也是产生一个新的文件。下方的勾选都可以不用勾选。

OK后就可以生成一个测试文件,可以在上方栏进行选择。

输入完代码后,可以看到不同颜色的字。比如,蓝色表示关键字,绿色表达表达式、对象、常量之类的。黑色一般是自己命名的。

Check后没有问题就可以进行下一步了。左侧栏步骤是一步一步打开的,做完前一步,后面的步骤就会被解开。

然后要做仿真,仿真的对象是muxtwo,其命名为t0。记得保存。变灰了就是操作成功了。生成的文件可以用“记事本”打开以查看。

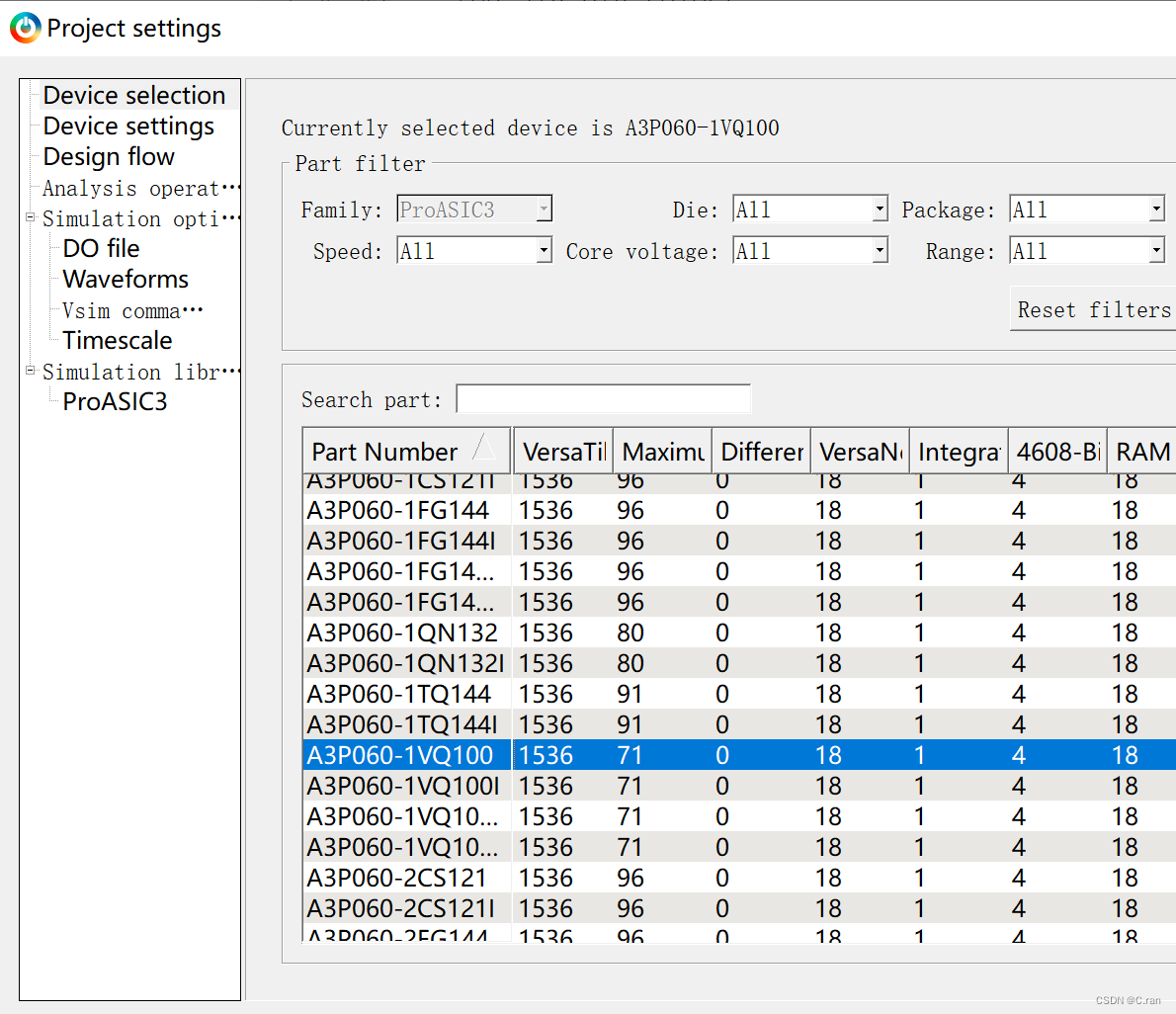

仿真之前需要先选择Configure Design Flow Options,进行一些设置。

仿真选项的设置,需要更改DO File中的内容,是最重要的,需要设置运行时长,这里默认都是ps。故在此进行设置,用键盘左上角“1”旁边的这个英文引号才可以,加入timescale命令,设置1ns/100ps,表示一个时间单位为1ns,精度为100ps,这样可以将延迟设置为非整数。

测试平台的模块名需要更改,改成测试平台的模块名,需要注意。

另外,调用需要改,如下。

然后就可以进行仿真,第一次仿真的时候会弹出窗口,选择Yes即可。

然后选择User

并且需要将下面的文件ADD到右侧去,即把用户定义的文件作为仿真的文件,点OK。

再进行仿真,打开后切换到Wave窗口查看。

波形图Wave窗口中,可以使用![]() (Zoom Full)来对波形图进行整理,从而使波形图在限定的区域内全部呈现。

(Zoom Full)来对波形图进行整理,从而使波形图在限定的区域内全部呈现。

在这里可以拖动以切换波形顺序,也可以在代码中换顺序,代码中的定义顺序与最后波形图窗口的顺序一致。

再看是否符合我们所涉及的逻辑。就可以进行下一步了。

综合 Synthesize:

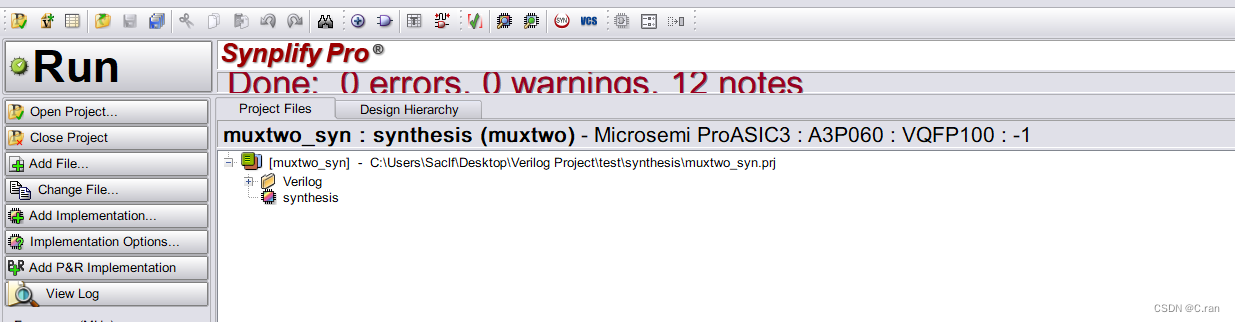

做完Simulate后,关闭Module Sim窗口,右键“Synthesize”,选择“open interactively”,进入后,选择“Run”,上方栏可看到“Done”,可以看到errors,warning,note(不用在意note)。

选择上方栏中的![]() (RTL View),即可看到电路逻辑图。

(RTL View),即可看到电路逻辑图。

想看是通过上面逻辑结构实现的,可以点击

想看是通过上面逻辑结构实现的,可以点击![]() (Technology View),即为工艺视图。

(Technology View),即为工艺视图。

如果想看整个流程,回到刚刚初始的Synplify Pro界面,

@N表示为note

划拉到最下面,可以看到总的使用的逻辑单元等数据:

综合完成后,可以关闭掉综合窗口。如果综合命令之前有“✔”,就代表这个已经完成通过了,是ok的。

进而可以做综合后的仿真:

可以看到,在做电路综合以后,由于ain为651000ps时,outw在651300ps才有输出变化,引起了0.3ns的传输延迟。是因为综合产生了具体地元器件,即会预测门电路或器件在信号变化以后产生输出的传输延迟,但不一定准确。这个延迟在综合之前的第一次仿真,是看不到的。

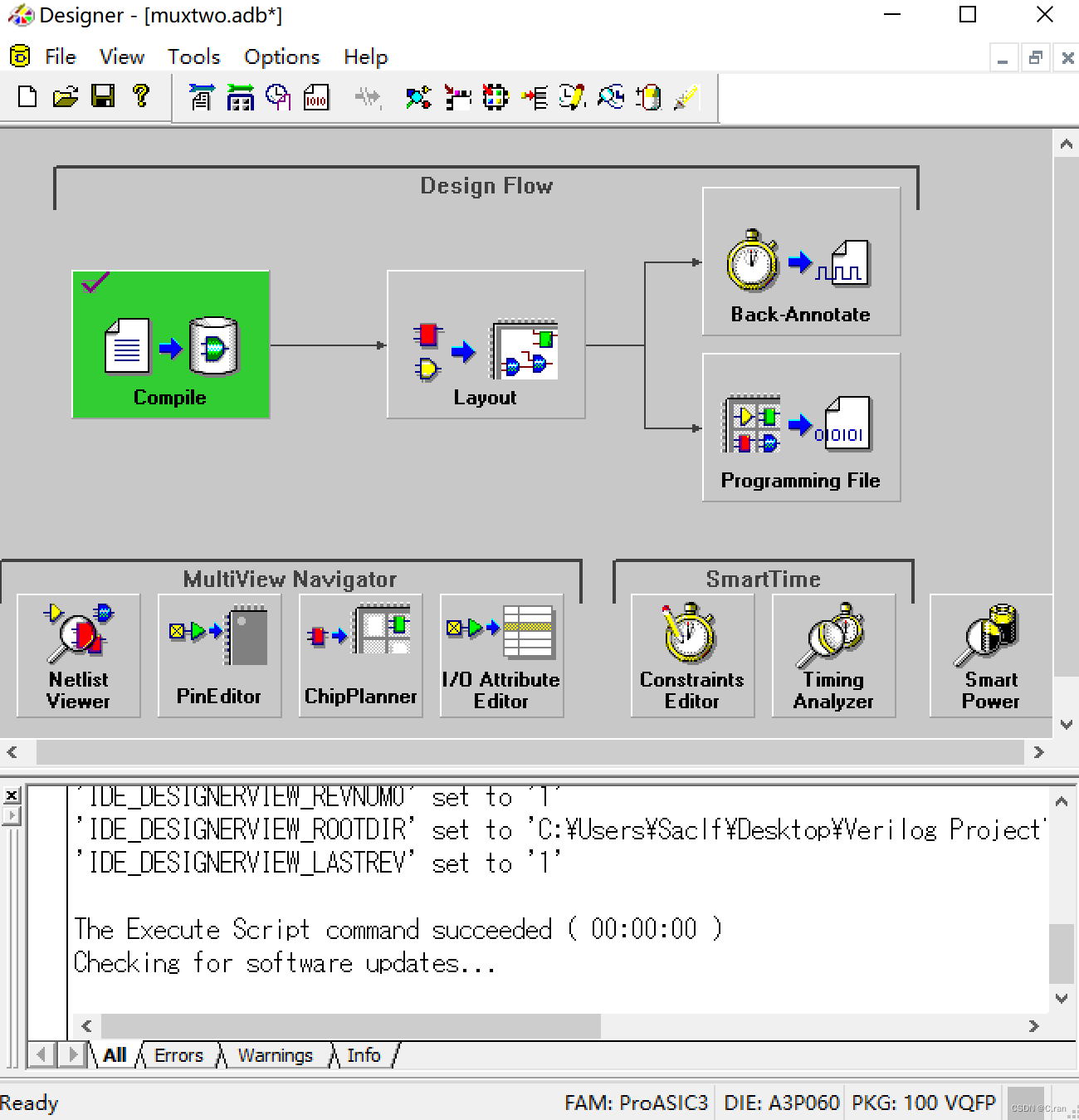

Compile:

实际上可以直接跳过,直接做Place and Route,因为在做place and route时第一步做的就是compile。同综合模块一样,直接对Place and Route右键,选择open interactively,否则看不到交互界面。

其中,Back-Annotate是优化,做不做都无所谓,但是要点一下,OK即可。

而Programming File到了实验室后,必须要做,只有这个命令才能生成烧录文件,才能对芯片功能做测试。

直接做布局布线即可,选择OK,变绿了表示完成了

至此,芯片的内部就被设计好了。

还没有用到芯片上时,先做一下针对芯片的仿真,即同样的信号作用于芯片的仿真结果会怎样,再Simulate一次。

这里如果出现Wave窗口没有自动弹出的情况,需要点击View栏,选择Wave即可。

此时输出与输入的时间差与刚才的波形不一致,是此芯片由于输入变化的时候产生的延迟,是准确的传输延迟。

完成后再看一下Place and Route,可以点击I/O查看真实布线或引脚。

在这里可以改变引脚号:

对于真实的上机操作场景而言,需要根据试验箱的具体铜柱或引脚的编号进行实际的选择。这一步建议再进行完成Lay out后进行,因为这样本身会检测到哪些引脚可能会使用到。但是需要注意的是,并非所有索引都是可以使用的,建议还是对照看会较方便一些。

由于为了接线方便,因此可以对于INPUT和OUTPUT分开进行索引,从而更好接线。

生成文件后,邮件Open Interactively打开Program Device等待烧录。

这里建议烧录完成后再接线,因为不确定芯片引脚的输入输出等是否接错的问题,需要先进行测试或者确定,这样也更加保护芯片安全。

这里笔者由于未在实验室使用试验箱,因此只是示范。

在这里,笔者标明了步骤:

首先,需要检查一号位置是否有编号,这个编号是烧录器的编号,只要有就代表主机已经识别到了。笔者图示这里没有。

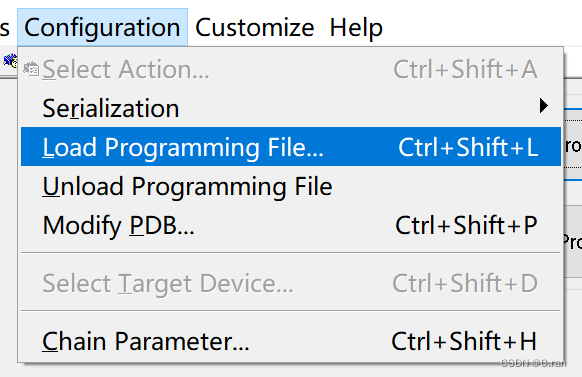

如果第一步显示为有,但是第三步却仍然是Run,就需要点击第二步的Configuration,进行配置。

配置时直接选择Load Programming File,并在弹出的窗口里选择.pdp文件![]()

即可。

关闭窗口就可以看到Run编程了Programming。

至此,笔者的实验一部分就介绍完毕。后续关于Model sim的使用以及实验二的操作,有待下次见分晓。感谢观看!

151

151

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?