12bit sar adc电路,可直接仿真,逻辑模块也是实际电路,可指导利用cadence或者matlab进行频谱分析

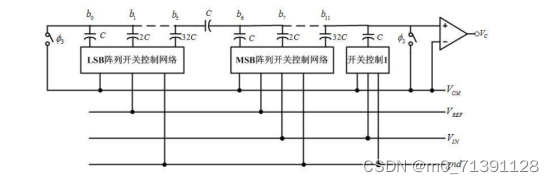

本次所提供的小项目为12bit sar adc, 所用工艺为simc 18mmrf,整体测试cell名称为12badc_ADC,最终的整个测试电路如图所示:

12badc_dac模块为DAC模块,12adc_COMP为比较器模块,12bsarlog_16B_COUNT模块为电路所需时序产生电路,12bsarlog_logic为逻辑模块,这些都是实际的电路,包括逻辑模块。

图2 用到的DAC结构

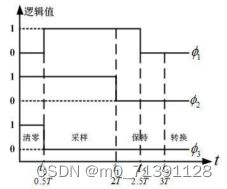

从开关网络控制信号可以看出,此控制信号将 DAC 划分为四个工作状态,其中清零、采样和保持所花时间为3个时钟周期,而作为12位的SARADC它转换一个模拟量至少需要13个时钟周期,因此,结合此DAC的工作特性,本文设计的SAR ADC转换一个模拟信号所花的总时间为16个时钟周期。DAC 的清零阶段(0-t0):此工作阶段的目的是将前一个转换数据所存储的电荷全部放掉。在此时间段内φ2和φ3为高电平,在DAC的电路中表现为电容阵列的所有电容的上、下极板均接在VCM上。在数据转换完成时VX的电压接近为VCM,所以清零阶段所需要的时间较短为0.5T。

12bit sar adc电路,可直接仿真,逻辑模块也是实际电路,可指导利用cadence或者matlab进行频谱分析

最新推荐文章于 2024-05-21 12:03:29 发布

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

674

674

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?