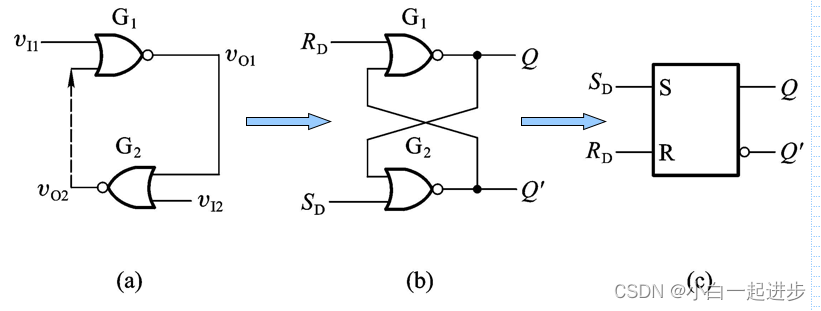

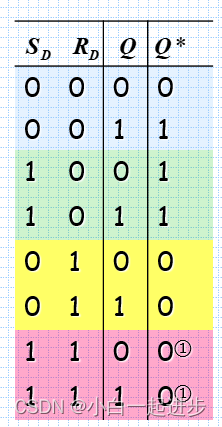

上图是由两个或非门组成的SR锁存器。下图是两个或非门组成的SR锁存器的真值表:

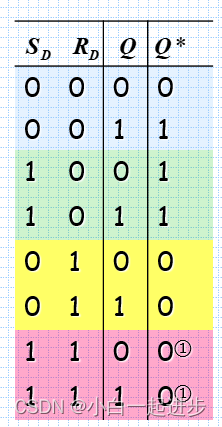

注意:Q代表SD和RD代入后得到的初始状态,而Q*是在已知SD、RD和初始状态后根据电路特性而得到的下一个Q的状态,即为次级状态Q*。(注意次级状态指的是Q*,而不是Q')

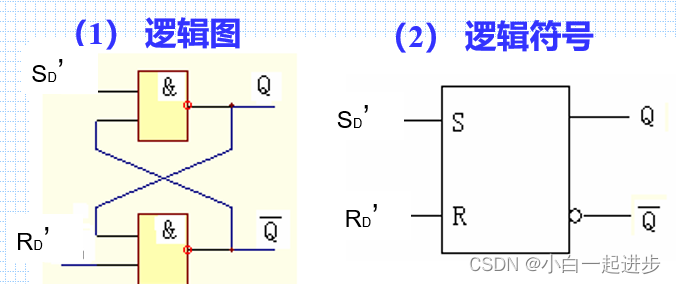

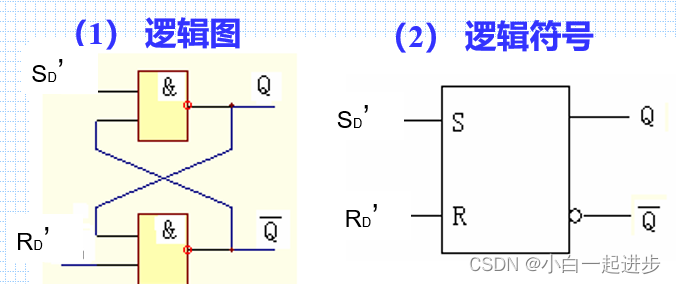

上图是由两个与非门组成的SR锁存器,其次级状态Q*与 两个或非门组成的SR锁存器的原理是一致的,只是逻辑电路不同。

SR逻辑电路是基础的逻辑电路,它在触发器、锁存器、定时器等方面有着极其广泛的应用。

上图是由两个或非门组成的SR锁存器。下图是两个或非门组成的SR锁存器的真值表:

注意:Q代表SD和RD代入后得到的初始状态,而Q*是在已知SD、RD和初始状态后根据电路特性而得到的下一个Q的状态,即为次级状态Q*。(注意次级状态指的是Q*,而不是Q')

上图是由两个与非门组成的SR锁存器,其次级状态Q*与 两个或非门组成的SR锁存器的原理是一致的,只是逻辑电路不同。

SR逻辑电路是基础的逻辑电路,它在触发器、锁存器、定时器等方面有着极其广泛的应用。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?