四.MOS管

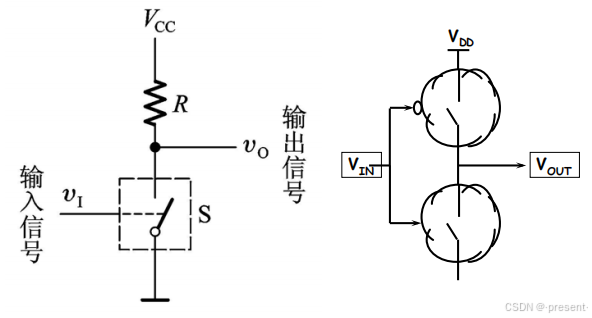

4.1 MOS开关

除了二极管充当开关外,MOS管也可以充当开关(通过电压来控制器件的导通与否)

和二极管一样,我们也先简单介绍一下它的原理

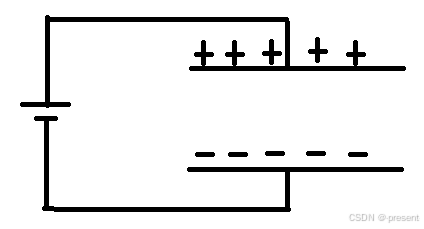

MOS管的来源就是我们初高中经常学习的平行板电容器

当电容器一边接上电源正极,另一边接上电源负极,就会带上等量的正负电荷

不过平行板上的电荷都是静止不动的,无法形成电流

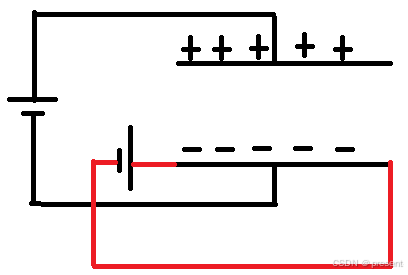

但换一种思路,假如又另外加一个电源呢?此时平行板上的电荷就会因为压差动起来,自然电流也就形成了

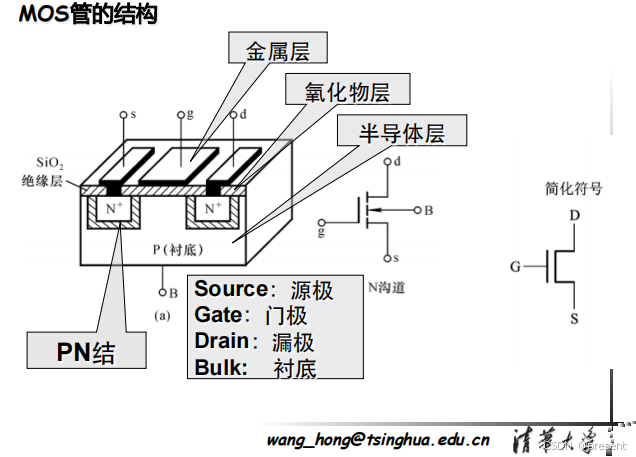

有了上述的设计思路,MOS管便横空出世了

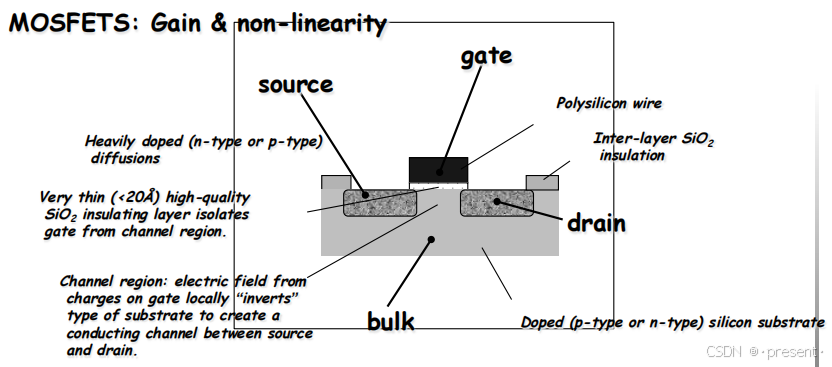

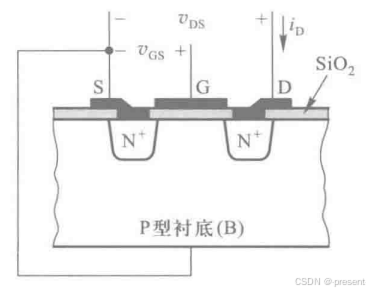

总共有四个端口,分别为源极Source,栅极Gate(也被称为门极),漏极Drain,衬底Bulk

还有一层非常薄(在0.1微米内)的二氧化硅层,用来隔开栅极和衬底,并不导电

对应的剖面图如下:

假如源极和衬底接在一起,即两者的电压相同

当

V

G

S

V_{GS}

VGS小于某个阈值

V

G

S

(

t

h

)

V_{GS(th)}

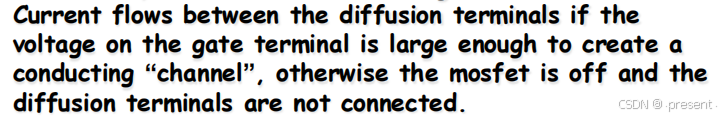

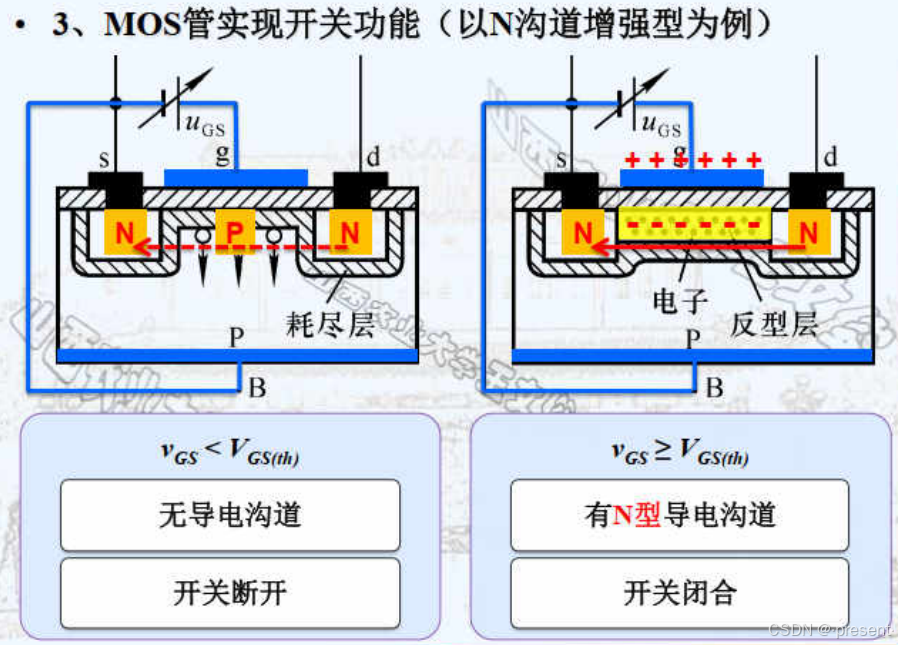

VGS(th)的时候,此时相当于一个背对背的二极管,没有电流通过

只有当

V

G

S

V_{GS}

VGS大于某个阈值

V

G

S

(

t

h

)

V_{GS(th)}

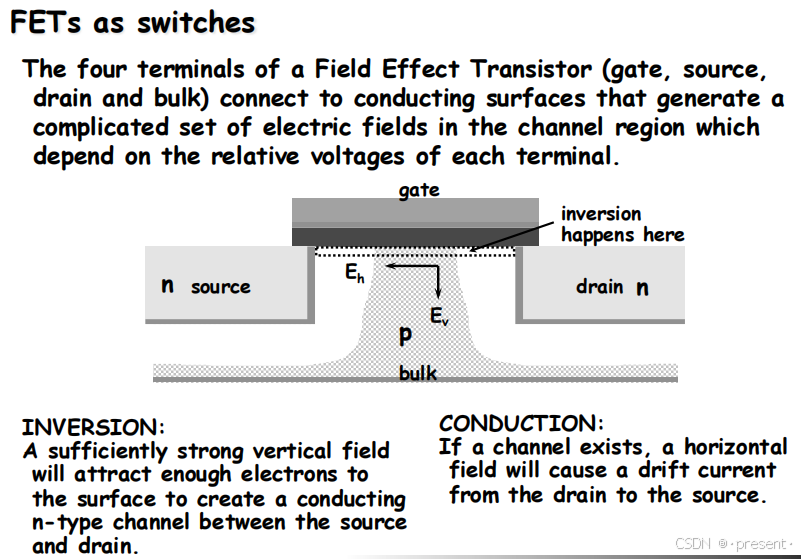

VGS(th)的时候,此时相当于我们上述说过的平行板电容器,在栅极会有正电荷,而在衬底会有等量的负电荷,此时便形成了一个导电通道,两口井源极和漏极(电子为多子)连在了一起

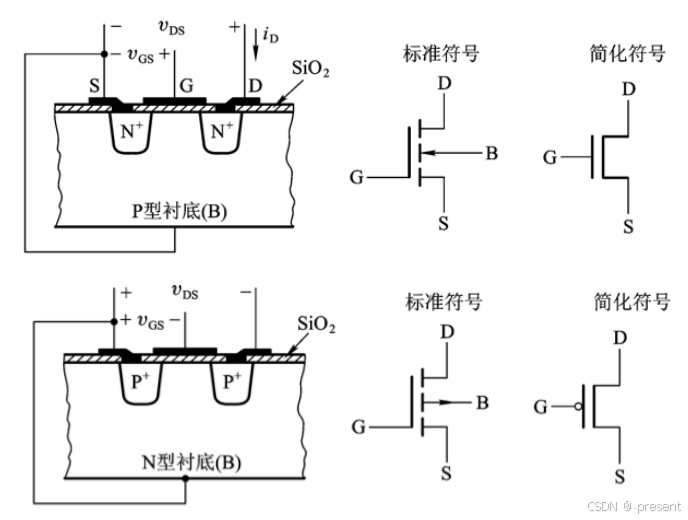

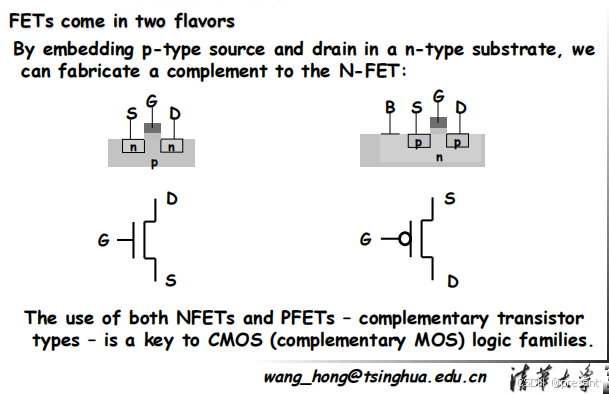

由于此时形成的沟道是电子(Negative),所以这类MOS管也被称为N沟道增强型MOS管;反之,假如形成的沟道是空穴(Positive),这类MOS管被称为P沟道增强型MOS管

假如此时我再接一个电源,

V

D

S

V_{DS}

VDS > 0,此时又形成了一个新的回路,电流便产生了

为什么源漏极区分,两者可以互换吗?

答案是可以的,我们之所以称它为源极(source),仅仅是因为在

V

D

S

V_{DS}

VDS > 0的情况下,电子是从源极开始出发,流向漏极;对应电流从漏极流向源极

通过控制

V

G

S

V_{GS}

VGS的大小,我们便可以实现开关的功能(在数电中,我们只利用MOS管的开关特性,而不采用其放大特性)

当然,虽然说数电中并不需要利用MOS管的放大特性,我们同样可以定性理解其如何做到放大

在平行板电容器中,电源加的越大,平行板上所带的电荷值也就相应提高

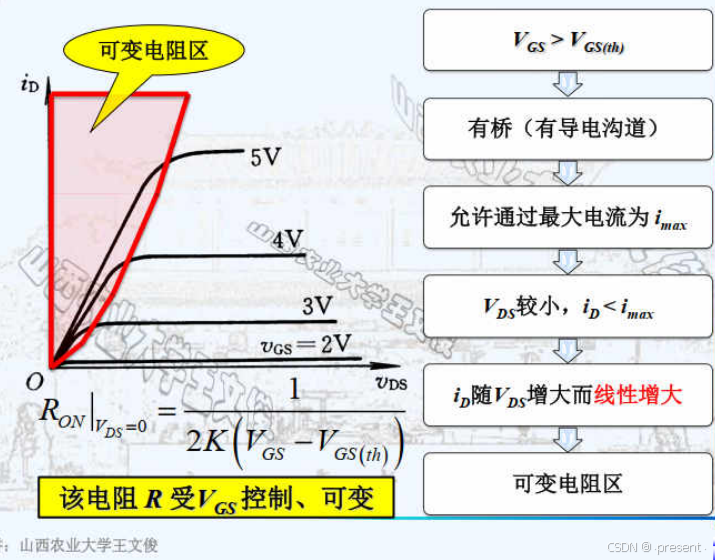

在MOS管中也是如此,当

V

G

S

V_{GS}

VGS越大,形成的导电通道自然也就越宽(等效电阻越小),此时在

V

D

S

V_{DS}

VDS > 0都相同的情况下,形成的电流自然也就越大(马路越宽,单位时间内通过的车辆也就越多)

当

V

G

S

V_{GS}

VGS相同时,

V

D

S

V_{DS}

VDS 不断增大,形成的电流自然也就越大(马路宽度相同,每辆车平均行驶的速度相应提高,单位时间内通过的车辆也就越多)

我们也把MOS管此时所处的区域称作可变电阻区

但是

V

D

S

V_{DS}

VDS 不断增大,电流会无限制不断相应增大吗?

我们说理想很丰满,现实很骨感,答案是并不会

当加的横线电场,即

V

D

S

V_{DS}

VDS 越大,就可能会形成夹断,进入饱和区,此时继续增大

V

D

S

V_{DS}

VDS,电流也不会有很大变化

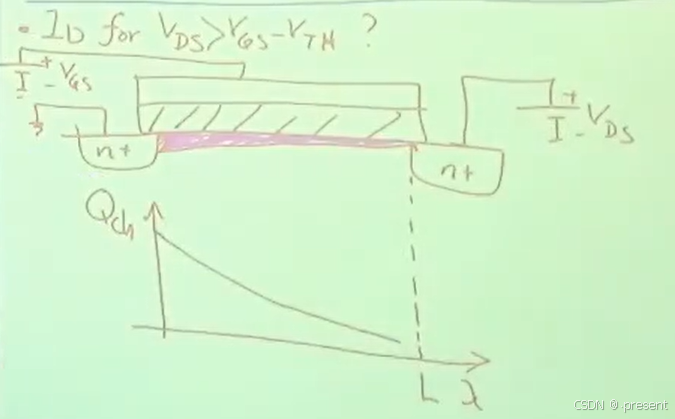

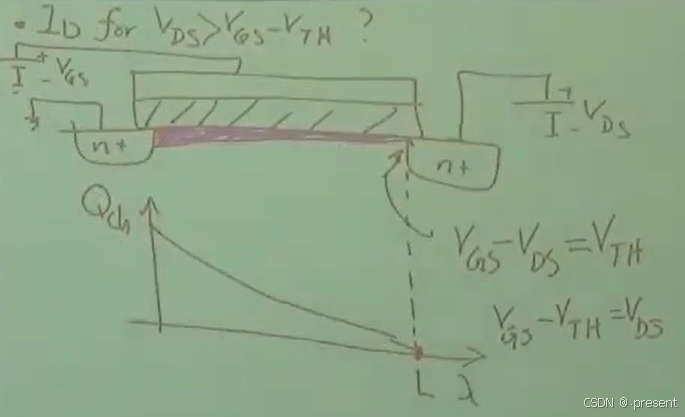

为什么会形成夹断呢?

答案也很好理解,导电通道是一根理想的导线吗?答案是不是

我们应该将其等效为一个电阻,流经电阻必定会带来压降

比如

V

D

S

V_{DS}

VDS =

V

D

V_{D}

VD -

V

S

V_{S}

VS = 5V > 0 ,即

V

D

V_{D}

VD >

V

S

V_{S}

VS ,电流在流经我们的导电通道(电阻)时,就会有压降,使电压从

V

D

V_{D}

VD降到

V

S

V_{S}

VS

所以,MOS管不是我们的电容器,它是一类“特殊的电容器”,在导电通道各点处所含有的电荷量数目是不同的(Q = CV,V不同),真实的导电沟道会随着我们的

V

D

S

V_{DS}

VDS 不断增大,变成一条斜坡的形态

而且

V

D

S

V_{DS}

VDS越大,斜坡越倾斜,当

V

D

S

V_{DS}

VDS增大到

V

G

S

V_{GS}

VGS,甚至比

V

G

S

V_{GS}

VGS要大时,就不再足以能够形成一个导电通道了,此时就会发生夹断现象

我们也把这种进入夹断状态,

V

D

S

V_{DS}

VDS增大,电流几乎不发生什么改变的状态,称之为恒流区

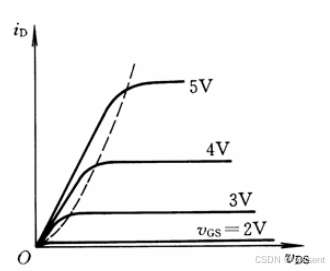

总结一下就是下面这张图

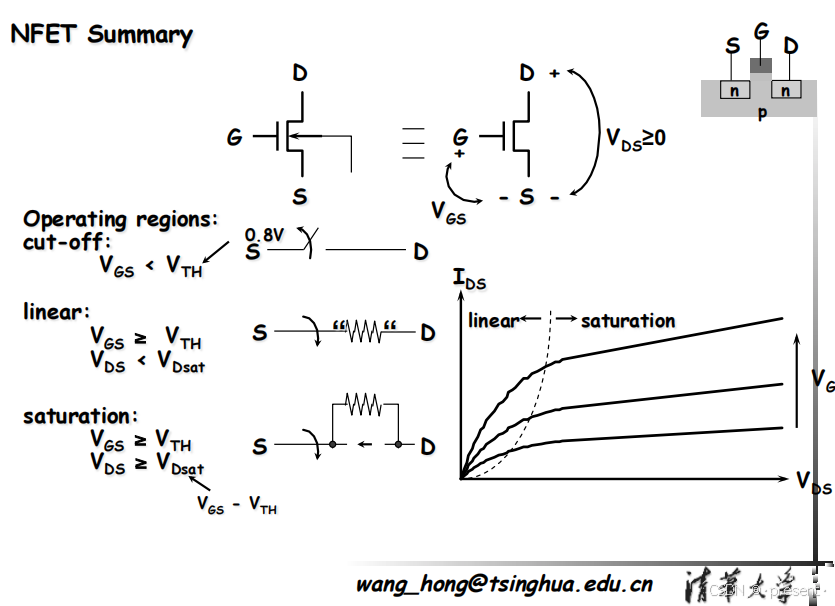

总共三个区域,截止区,可变电阻区(线性区),饱和区

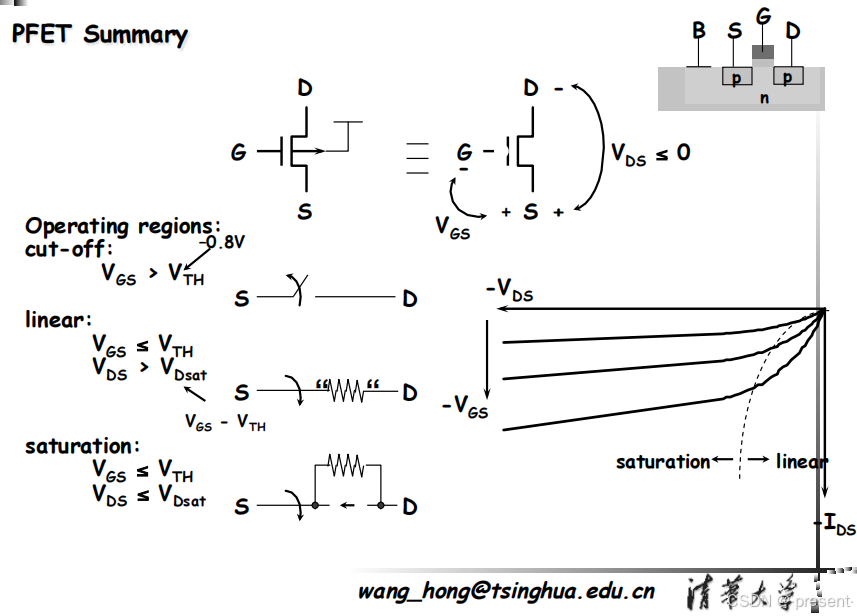

P沟道增强型MOS管也是同样的原理,只不过此时我们形成的沟道是空穴,即正电荷,所以

V

G

S

V_{GS}

VGS应该小于0,并且只有小于某个

V

G

S

(

T

H

)

V_{GS(TH)}

VGS(TH)值,MOS管才会导通,相当于开关接上。

整张图像和N沟道增强型图像关于原点对称

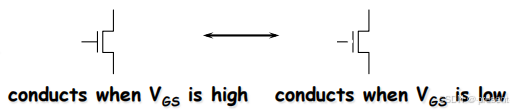

可简单记为高电平NMOS管导通,低电平PMOS管导通

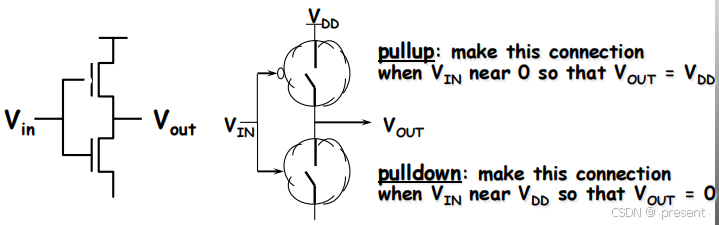

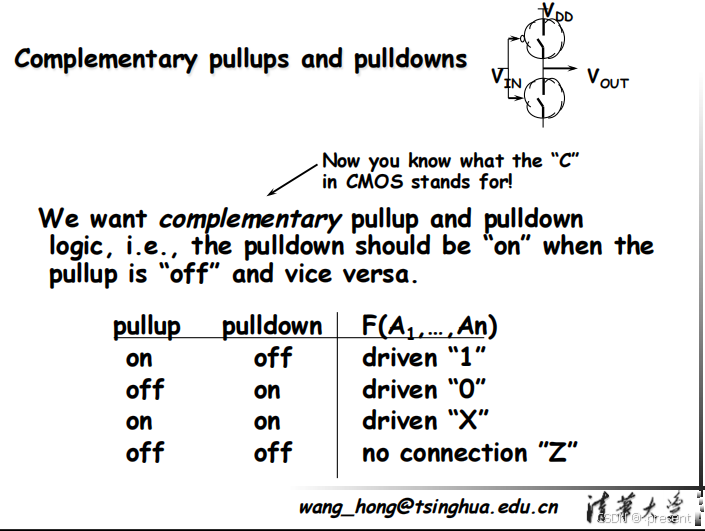

4.2 CMOS反相器(Complementary)

4.2.1 CMOS反相器的组成

在开关一节中,我们曾经提出过互补开关的概念(two-pole switch),在二极管时,我们并没有实现实际的电路,而在这节中我们将自己从零开始实现一个

第一个思考的问题,为什么我们要采用互补开关电路?

这个其实我们前面讲到过了,单刀开关有着电平偏移,带负载能力差的问题,尤其是电平偏移问题,是我们不希望要的,每个开关应该都遵守相同的协议(输入,输出采取同样的游戏规则)。

第二个思考的问题,应该怎么修改我们的单刀开关?

互补开关电路是如何设计出来的?

我们希望所有的门电路输出都相同,换句话说,我们想要一个理想的高电平和低电平输出

什么是系统中最理想的高电平和低电平?

这在我们第一节引言中就已经提过,电源VCC和地

所以,我们要将电源VCC和地从单刀开关中拉出来,相互独立隔开两者,不管输出两者之中的哪一个,都和另外一个没有关系

如何隔开两者,使得两者各自的输出只和输入信号有关呢?

顺水推舟便想到增加一个开关,一个开关负责一个理想输出

第三个思考的问题,为什么要采用互补开关呢?可不可以采取同样类型的开关?

我们说假如是相同类型的开关,同时打开没有问题,但一旦同时闭合,电源瞬间就会被击穿

所以不能采用相同类型的开关,必须采用互补类型,当一个开关闭合,另外一个开关便打开

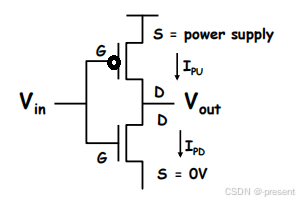

于是便得到了我们的CMOS反相器

输入与输出之间为逻辑非的关系,因此称为反相器

第四个思考的问题,对于NMOS(PMOS)管来说,谁是漏极,谁是源极?

要回答这个问题,就必须充分理解我们之前所说的MOS管原理

NMOS管之所以被称为N沟道增强型MOS管,是因为所形成的沟道是电子,源极提供电子,漏极接收电子

同样的,PMOS管之所以被称为P沟道增强型MOS管,是因为所形成的沟道是空穴,源极提供正电荷,漏极接收正电荷

因此,NMOS管接到下方时,是谁提供电子呢?

答案是地,所以与地相连的是源极,剩下与输出直接相连的端口是漏极

同理,PMOS管接到上方时,是谁提供正电荷呢?

答案是电源,所以与电源相连的是源极,剩下与输出直接相连的端口是漏极

第五个问题,为什么PMOS管在上面,NMOS管在下面呢?可不可以反过来?

假如NMOS管在上面,PMOS管在下面,会发生什么情况呢?

此时输入低电平,输出逻辑"0"(接地);输入高电平,输出逻辑"1"(电源VCC),完美符合我们之前所学过的"常识",而不是像现在这样的反相关系

但是细细思考真的是这样吗?

NMOS管导通的条件是什么?真的是高电平导通吗?

并不是,之所以输入高电平,NMOS导通,是因为它在下方,源极S电平最低,直接就为0,

V

G

S

V_{GS}

VGS >

V

G

S

(

t

h

)

V_{GS(th)}

VGS(th),只需要

V

G

V_{G}

VG > 0

进一步说,对于NMOS管假如要导通,必须要

V

G

S

V_{GS}

VGS >

V

G

S

(

t

h

)

V_{GS(th)}

VGS(th),

V

D

S

V_{DS}

VDS > 0,源极S在三个端口的电压是最低的

假如NMOS管接到上方,与电源相连的一端可以作为源极吗?

答案显然是不能的,所以只能输出端作为源极,三方中总该有一方退让

而我们又需要

V

G

S

V_{GS}

VGS >

V

G

S

(

t

h

)

V_{GS(th)}

VGS(th),

V

D

S

V_{DS}

VDS > 0,故

V

G

V_{G}

VG 输入电压信号不变的情况(假设为

V

C

C

V_{CC}

VCC)下,此时假如导通,输出信号不是

V

C

C

V_{CC}

VCC,而是比

V

C

C

V_{CC}

VCC要小的一个值

V

C

C

V_{CC}

VCC -

V

G

S

(

t

h

)

V_{GS(th)}

VGS(th)(和PMOS管接到上方时,作对比),

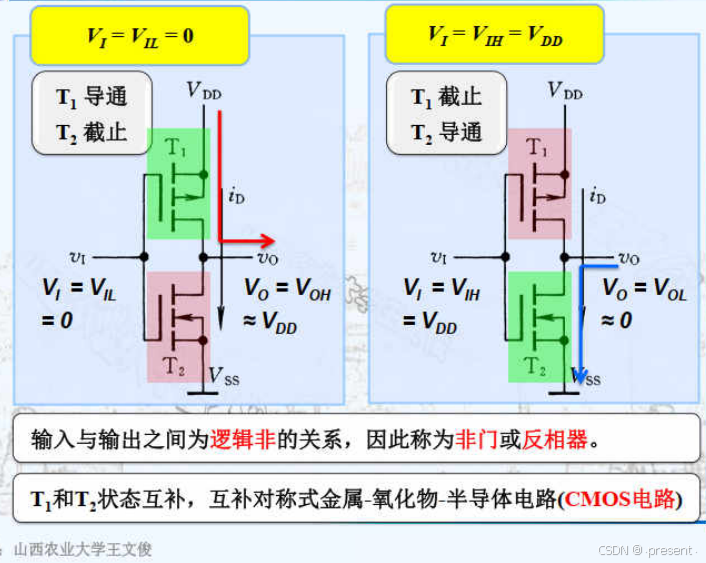

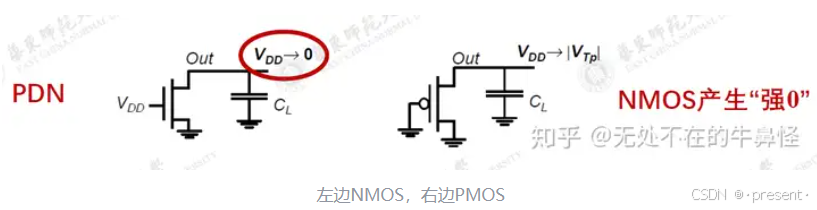

这就是我们所说的NMOS管输出强0,输出弱1的由来

而PMOS管则相反,

V

G

S

V_{GS}

VGS <

V

G

S

(

t

h

)

V_{GS(th)}

VGS(th),

V

D

S

V_{DS}

VDS < 0,PMOS管导通

源极S是三个端口中电压最高的,我们之所以说输入低电平,PMOS导通,原因是源极S此时直接和VCC相连,自动满足电压最高的条件

但是PMOS管假如接到下方,则与地相连的一端同样不能作为源极,要有一个端牺牲,只能和输出端相连的一端作为源极

于是

V

G

V_{G}

VG 输入电压信号不变的情况下,输出电压

V

S

V_{S}

VS≠VCC,此时假如导通,输出信号不是0,而是比0要大的一个值(和NMOS管接到下方时,作对比)

这就是我们所说的PMOS管输出强1,输出弱0的由来

而我们提出来互补开关的目的,其中一个重要原因就是解决电平漂移的问题,想要得到理想的数字信号"1",“0”

因此,我们采取PMOS管上接,NMOS管下接的设计

此时虽然反相,但是获得的却是高质量的数字信号"1",“0”

但是,我们又可以武断地下结论,NMOS管只能接在下面,PMOS管只能接在上面吗?

答案也是错误的,不可以直接下结论

每一个工作区域都有着它自己大展宏图的场地,只不过在数电中,我们需要输出高质量的数字信号,所以,采用反相器的设计

但是NMOS管也能接在下面,PMOS管接在上面,这在模电中也是一个比较常见的设计,发挥一个电压跟随器的作用,输出电压摆幅在[

V

G

S

(

t

h

)

V_{GS(th)}

VGS(th),

V

C

C

V_{CC}

VCC -

V

G

S

(

t

h

)

V_{GS(th)}

VGS(th)],常用于大功率电路的输出级,优点也很明显,每次只有一个管子导通,静态功耗很小

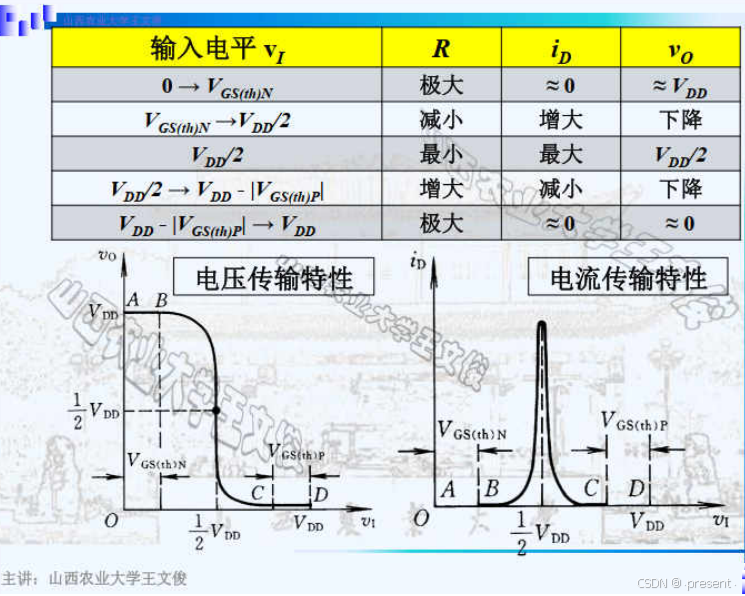

4.2.2 输入和输出之间的电压关系

我们说反相器起到的是反相的效果

输入低电平,输出高质量的数字信号"1"

输入高电平,输出高质量的数字信号"0"

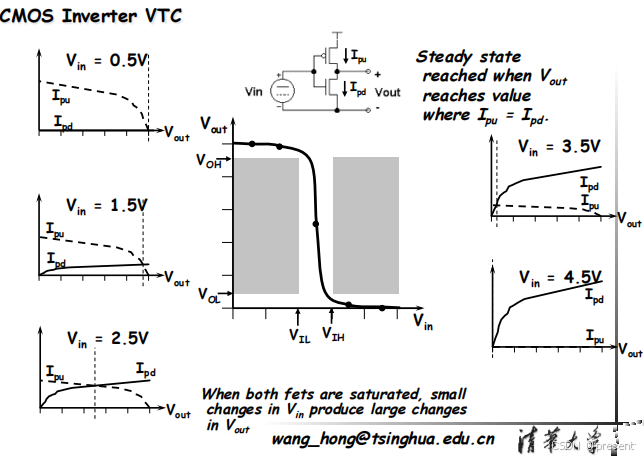

真的是这样吗?最直观看出输入和输出之间的电压关系就是画出对应的图像(电压工作曲线)

假如我们现在在实验室,就可以在输入端输入不同的电压信号,用示波器来扫描出对应的输出(选择X-Y档),画出对应的图像

但是现在我们不在实验室,只能用我们脑子来分析了

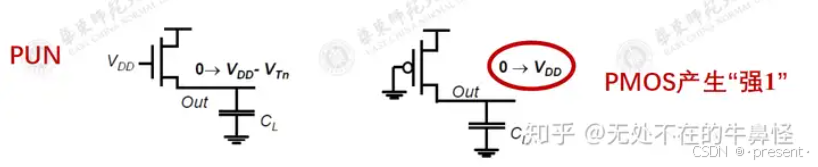

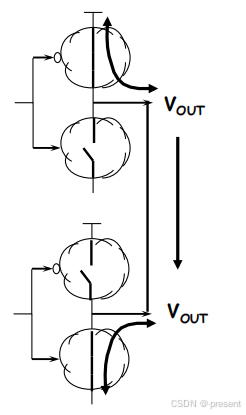

从定性上来分析(图解法)

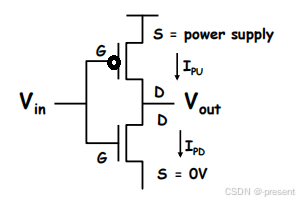

流过上面管子的电流

I

p

u

I_{pu}

Ipu和流过下面管子的

I

p

d

I_{pd}

Ipd应该是完全一样的

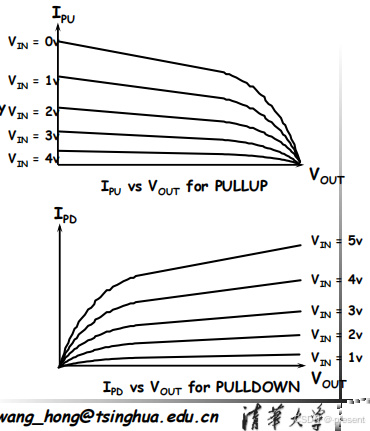

而PMOS管和NMOS管的伏安特性曲线我们在上一节也知道了

PS:之前我们画的工作曲线自变量是

V

D

S

V_{DS}

VDS,此时工作曲线的自变量是

V

D

=

V

o

u

t

V_{D} = V_{out}

VD=Vout

对于NMOS管来说,

V

S

V_{S}

VS = 0,因此

V

o

u

t

V_{out}

Vout直接就等于

V

D

S

V_{DS}

VDS,所以曲线并没有发生任何改变

但是PMOS管就不一样了,

V

S

V_{S}

VS =

V

C

C

V_{CC}

VCC ≠ 0,所以,假如想要得到PMOS的工作曲线,还需要整体图像往右平移

V

C

C

V_{CC}

VCC,并且由于电流不是从D到S,而是从S到D,因此还要再做一次关于x轴的翻转

两者的交点,汇成的曲线,就是我们CMOS的电压工作曲线

当然,我们还可以从定量的角度推理,得出对应的VTC曲线

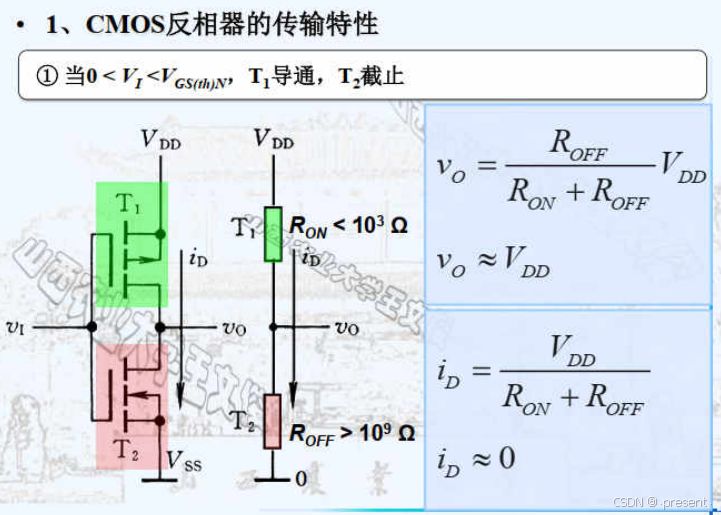

当输入信号为低电平时,上面的T1管导通,下面的T2管截止

输出电压可以直接看作是电源电压,因为下面T2管的电阻相较于T1管而言非常大,分走了大部分电压

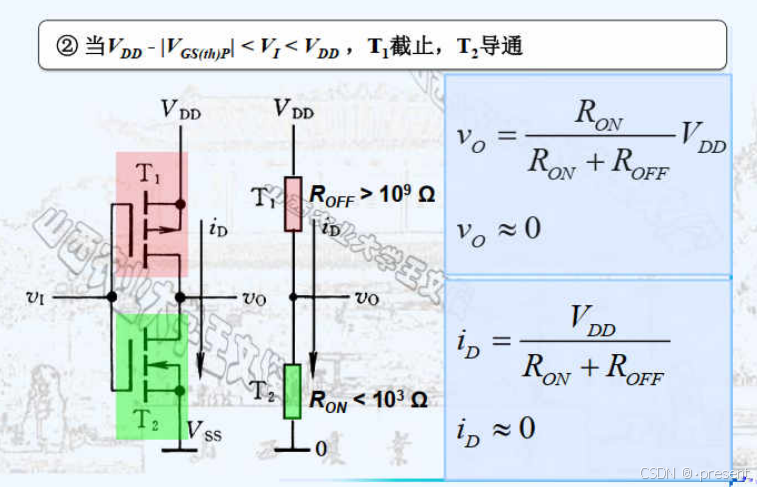

当输入信号为高电平时,上面的T1管截止,下面的T2管导通

输出电压可以直接看作是0,因为下面T2管的电阻相较于T1管而言非常小,没分到啥电压

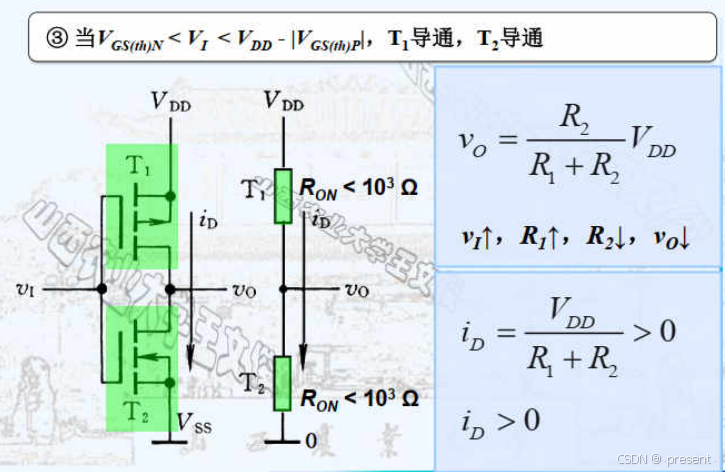

当处于两者之间的状态时,两个管子都导通

并且输出电压随着输入电压的增大,T1管的电阻增大,T2管的电阻减小,而逐步变小

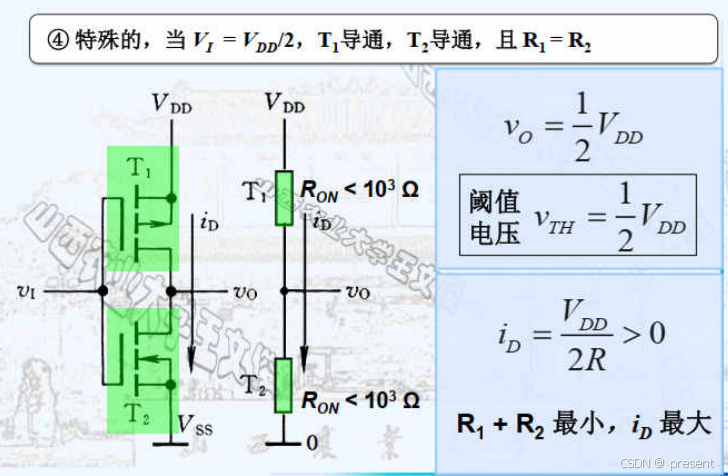

特殊的,当输入电压为电源电压的一半时

上下两个管子都导通,并且等效出来的电阻都相同,输出电压为电源电压的一半

通过上面的定量分析,同样可以画出来对应的工作曲线

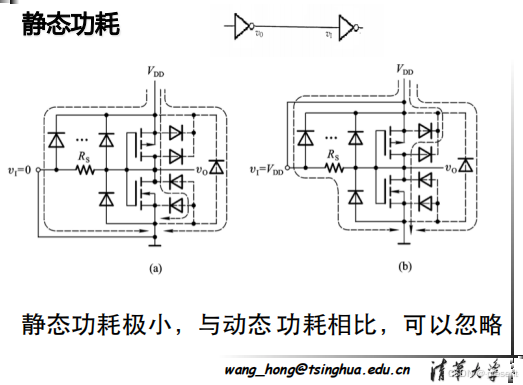

从分析的过程中我们也可以看出来CMOS的一大重要特性,当输出"0"或者"1"时,有且仅有一个MOS管导通,此时电流接近于0,没有一点功耗!

而在过渡地带,会有尖峰电流产生,并且在输入电压为电源电压的一半时取到最大值(初中所学的不等式,

R

1

2

R1^2

R12 +

R

2

2

R2^2

R22 ≥ 2R1R2,在R1 = R2时取到等号)

也就是说随着工作频率的提高(0,1之间不同切换),出现的尖峰次数也就越多

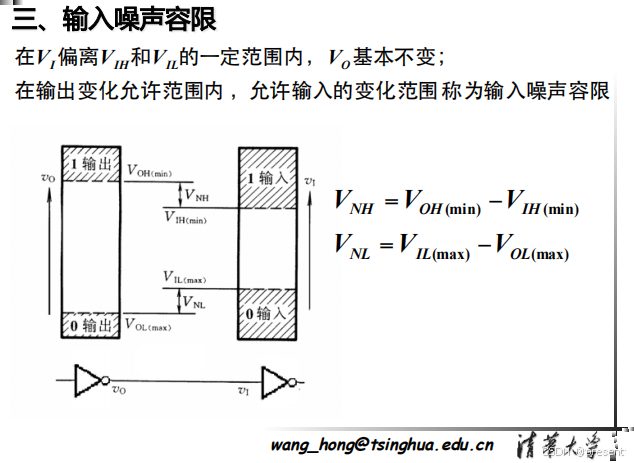

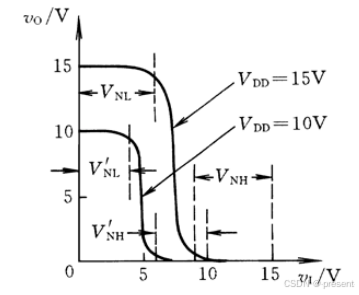

4.2.3 输入噪声容限

我们在前面也已经提到过我们的器件的输出,往往并不可能就输出理想的数字信号"1",“0”,在传输过程中,受噪声干扰等问题,发生电平偏移是很正常的事情

因此器件判断这是"0"还是"1",往往是一个取值范围,允许我们发生差错(有一个波动范围)

噪声波动容限取

V

N

H

V_{NH}

VNH和

V

N

L

V_{NL}

VNL的最小值

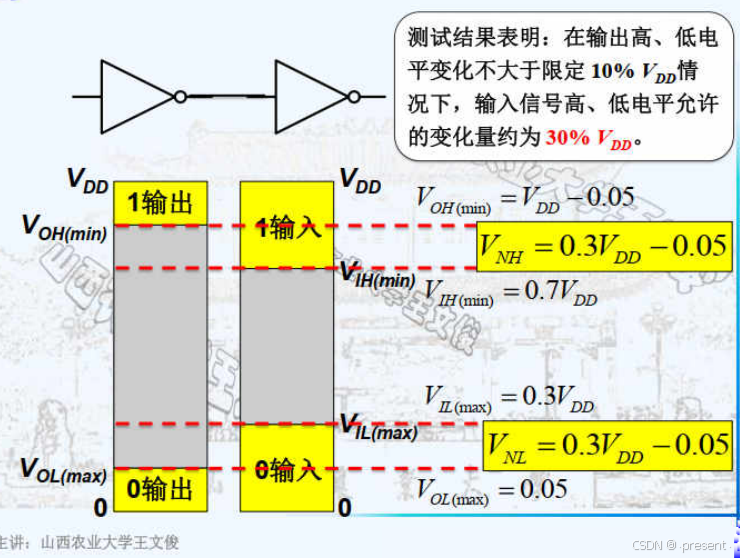

而测试结果表明,在输出高,低电平变化不大于限定10%

V

C

C

V_{CC}

VCC情况下,输入信号高低电平允许的变化量约为30%

V

C

C

V_{CC}

VCC

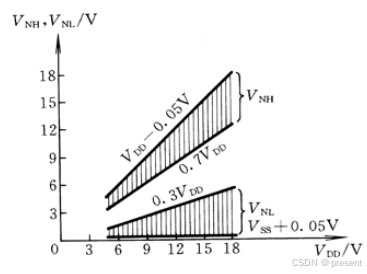

将电源电压

V

C

C

V_{CC}

VCC作为自变量,

V

N

H

V_{NH}

VNH和

V

N

L

V_{NL}

VNL作为因变量,就可以分别画出来对应的一次函数图像

图中两两直线的差值,就是我们的输入和输出噪声容限

不难直观看出来,通过提高电源电压

V

C

C

V_{CC}

VCC,可以提高我们的噪声容限

但是电源电压 V C C V_{CC} VCC可以无限增大吗?

答案也是不行的,电源电压

V

C

C

V_{CC}

VCC的增大,也会带来功耗的上升

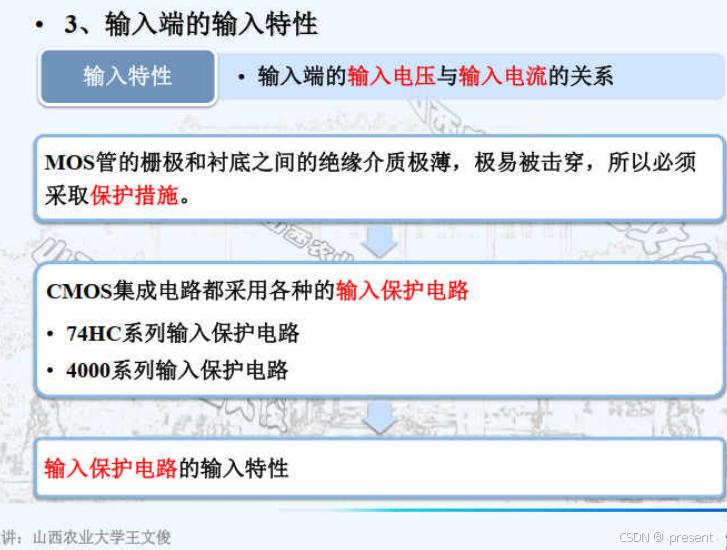

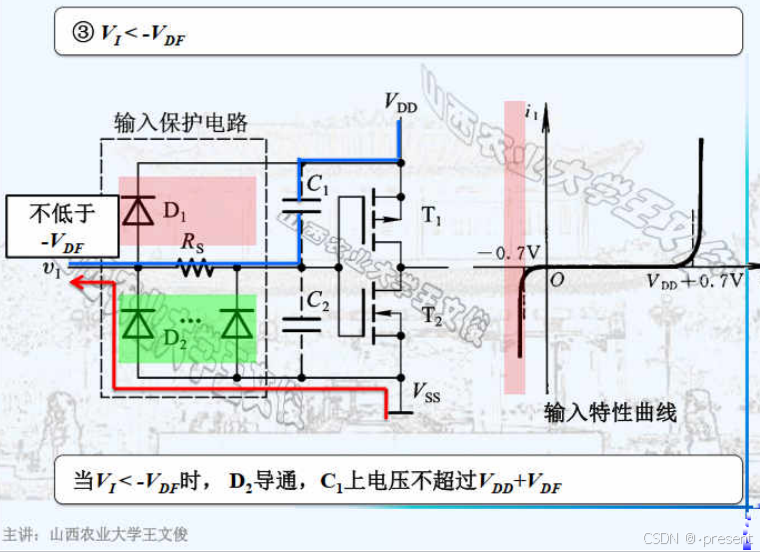

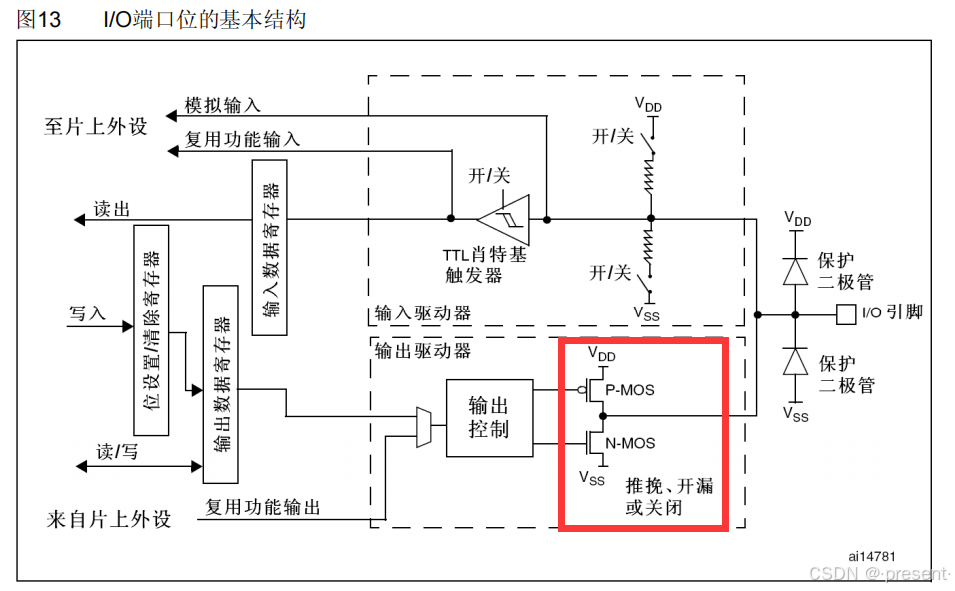

4.2.4 CMOS静态输入/输出特性

输入特性

MOS管的栅极和衬底之间的绝缘介值极薄,很容易被击穿,因此我们往往需要加保护电路

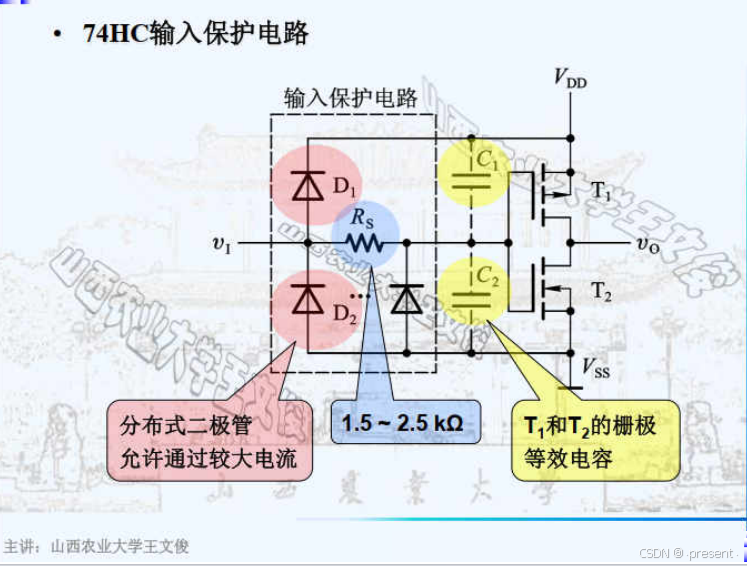

我们可以简单来看一下其中一款被称作74HC的保护电路

虽然被称为保护电路,但其实我们发现并没有多什么器件,只多了两个核心的分布式二极管(允许通过较大电流)

当我们的输入信号正常时(在0到

V

C

C

V_{CC}

VCC范围内),它们都不会工作

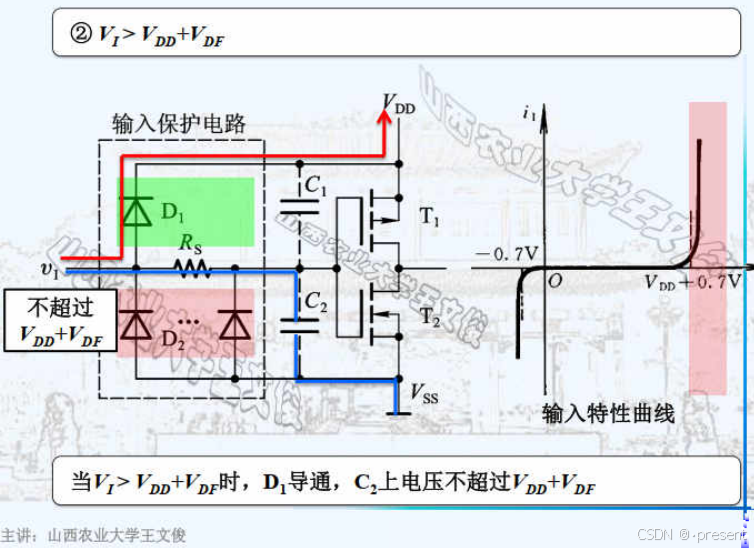

但是一旦输入信号大于

V

C

C

+

V

D

F

V_{CC} + V_{DF}

VCC+VDF,此时二极管就会被导通,然后将输入信号钳位在

V

C

C

+

V

D

F

V_{CC} + V_{DF}

VCC+VDF,以起到保护我们反相器的作用

同样的,当输入信号小于

−

V

D

F

-V_{DF}

−VDF时,下面的二极管也会导通,将栅极信号钳位在

−

V

D

F

-V_{DF}

−VDF,保证加到C1上的电压也不会超过

V

C

C

+

V

D

F

V_{CC} + V_{DF}

VCC+VDF

当然,这种保护措施是有一定限度的,通过两个二极管的正向导通电流过大,或者反向电流过大,都会直接先干掉两个二极管,然后再击穿MOS管栅极,因此,实际上保护电路还比这个更复杂,会采取一些附加的保护措施,这里就不再详谈了.

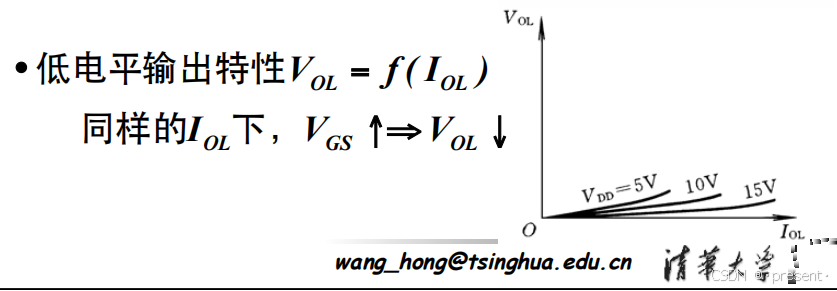

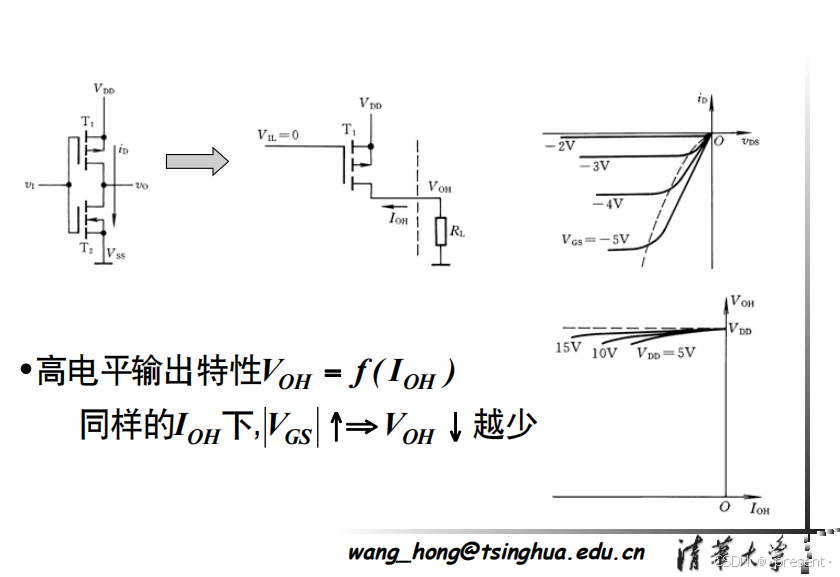

输出特性

输入特性研究完后,我们来研究CMOS的输出特性

所有的数字电路,信号在一级级传递,都是从一级输出传到下一级的输入

每一级的输出,其实都可以等效为一个有内阻的电压源

那这个电阻从哪里来?

当上面管子导通,输出高电平时,就是上面管子的电阻

下面管子导通时,输出低电平,就是下面管子的电阻

既然有内阻,当输出接上负载的时候,输出的电压值自然也会发生对应的变化,或者被抬高,或者被拉低

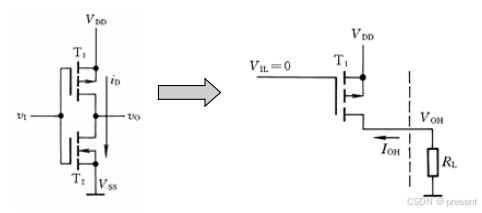

当输入低电平的时候,由于上面管子截止,所以我们可以直接把它去掉,整个电路可以等效成这样一种样子

那现在我们可以问一个问题,当负载的数目增多时,负载的值是减小还是增大?

答案是减小,不同电阻相当于并联在一起,越并越小

所以此时灌进去NMOS管的电流会增大,电压输出也就不是0,会随着负载数目增多,而不断抬升

而上面这张图,其实就和我们原来学过的NMOS工作状态图一样

那此时我们想要NMOS管工作在哪个区呢?

答案是线性区(可变电阻区)

原因是我们想要MOS管充当开关,将输出电平尽可能的拉低,也就是

V

D

S

V_{DS}

VDS尽可能要小

所以我们把我们希望器件工作在的区域截取出来,并调个位置,就能直接得到我们输出特性曲线

为什么我会有一组曲线?(注意此时的输入为 V D D V_{DD} VDD, V D D V_{DD} VDD = V G S V_{GS} VGS)

答案是MOS管的沟道宽度由

V

G

S

V_{GS}

VGS来控制,当

V

G

S

V_{GS}

VGS越大,也就是沟道越宽,等效出来的电阻值也就越小

对应在图中,它的斜率也就越小,自然也就会有一组曲线

那我们在实际操作中,假如想要输出的电平尽可能被拉低,应该选取 V G S V_{GS} VGS大好还是小好?

答案肯定是大比较好,此时等效出来的电阻就很小,输出电平就越接近于0

但是输入电压越大越好,但也要满足在合理的输入电压范围之内(0到

V

C

C

V_{CC}

VCC),并且当你输入电压调整的时候,同时也要抬高电源电压

输出高电平的时候,也是同样的操作

我们同样截取PMOS管可变电阻区的图像

即可得到对应高电平的输出特性曲线

4.2.5 CMOS动态特性

下面我们来谈CMOS的动态特性

总共可以分为三大模块,传输延迟时间,交流噪声容限,动态功耗

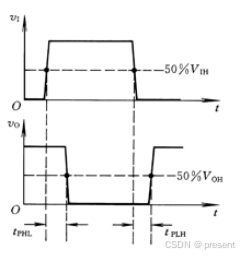

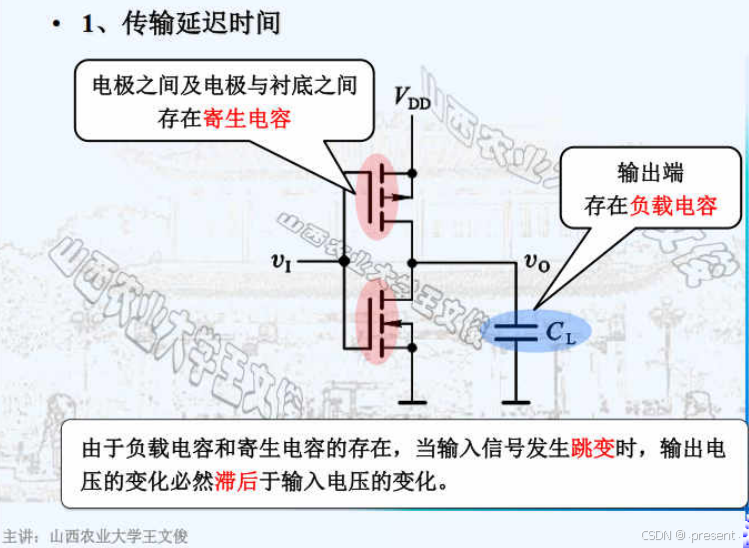

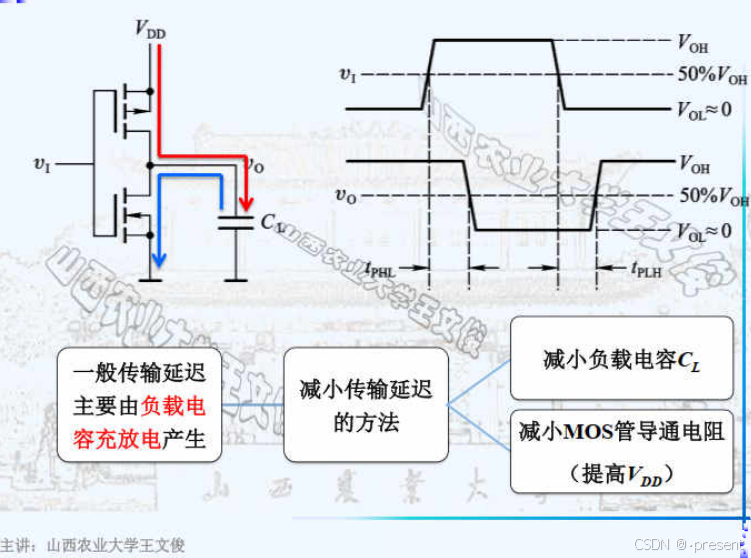

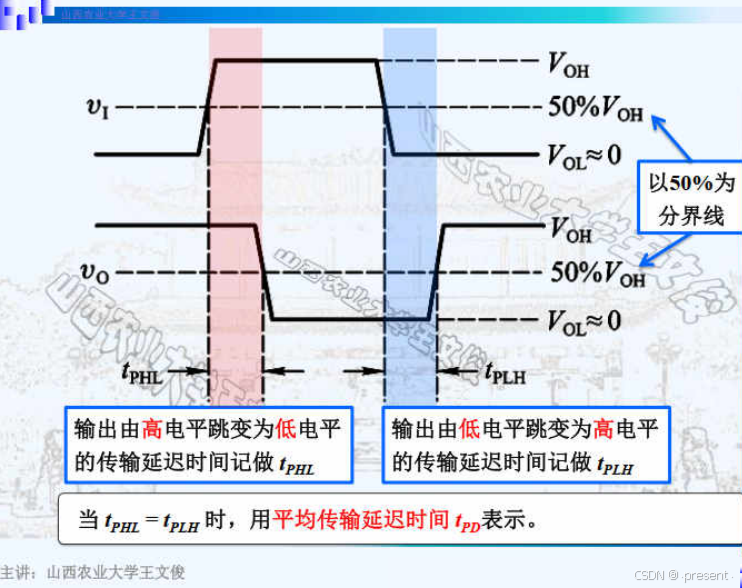

传输延迟时间

传输延迟时间,指的就是输出的变化会滞后输入的变化出现

为什么会有延迟呢?它取决于谁?

我们说关键就在于电容的影响

可能会有人说,CMOS电路中并没有看到电容的存在啊?

不要忘记,我们MOS管的设计,就是从电容,两个平行板电容而来,所以MOS管本身就是自带电容的

同样的,我们后面接的负载,除了电阻之外,也有它自己的电容

有电容,有电阻,就形成了RC回路,在抬高电压或者拉低电压之前,都要先充满电容或者把电容中含有的电荷释放掉,于是便带来了延迟

那如何减小这些延迟呢?

本质上就是减小这两个电容值

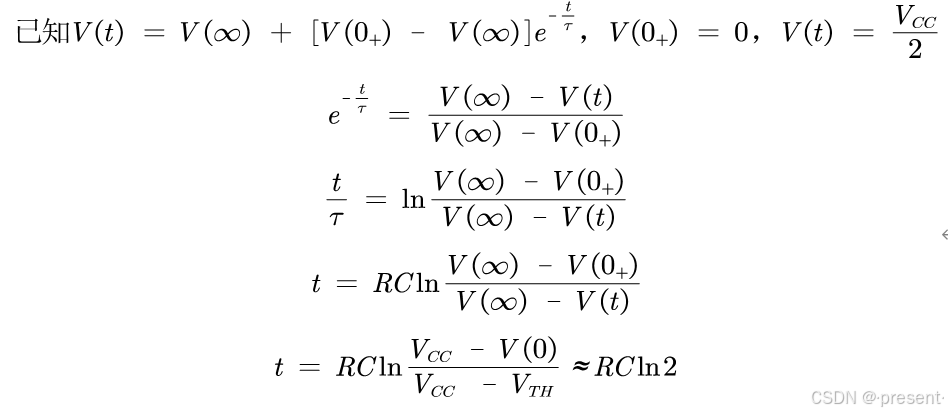

而这个延迟大概时间,我们其实是可以大致估算出来的

利用我们在电路分析中所学过的三要素法

取变化到50%

V

C

C

V_{CC}

VCC的时间,来作为我们的延迟时间,则可以得到下面的近似式子

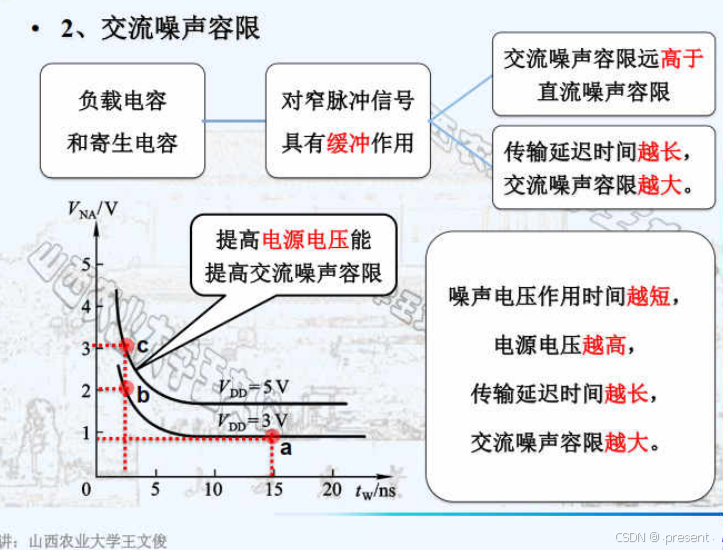

交流噪声容限

动态功耗

由于CMOS管不工作时,两个管子同时截止,电阻非常大,静态功耗近乎为0,所以我们不讨论静态功耗问题

关键讨论的就是CMOS电路的动态功耗

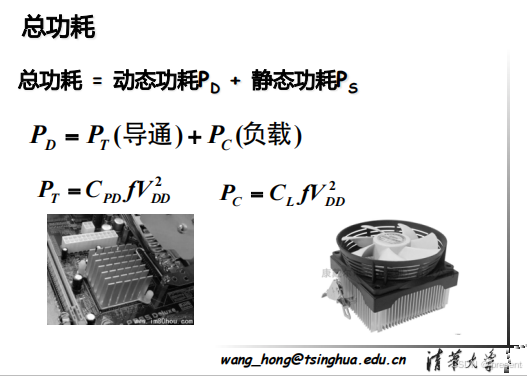

而动态功耗又由两部分组成

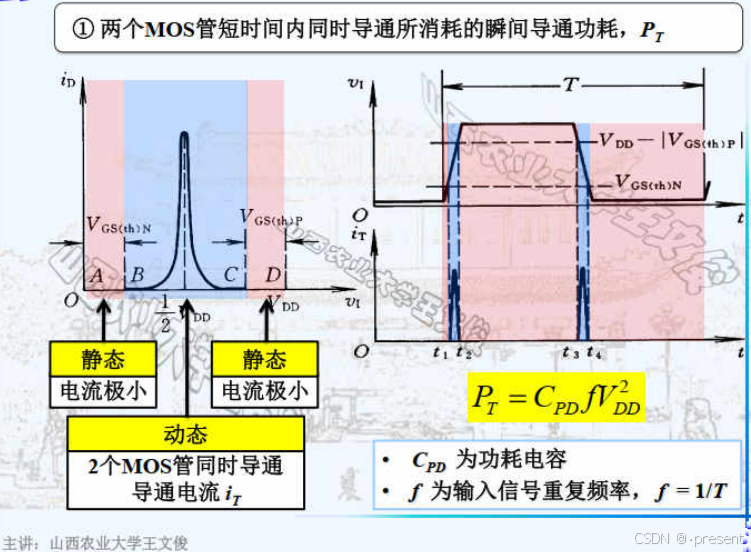

一个是我们前面提到过的导通功耗

这主要是CMOS工作时,会有两个管子同时导通的情况,从而出现尖峰电流,带来动态功耗

并且随着工作频率的增加(0和1之间的切换次数增多),导通功耗也会随之上升

对于的公式为

P

T

P_{T}

PT =

C

P

D

f

V

D

D

2

C_{PD}fV_{DD}^{2}

CPDfVDD2

其中

C

P

D

V

D

D

2

C_{PD}V_{DD}^{2}

CPDVDD2计算电容功耗(电路分析中所学),由于有两个MOS管,所以前面的二分之一没了

f

f

f代表的就是我们的尖峰个数

所以这个公式还是很好理解的

并且也和我们前面提到过的噪声容限相呼应,我们说电源电压提高,噪声容限越大,但是功耗也就越大

公式中也可以直观看出来这点,并且功耗还是平方倍的增加

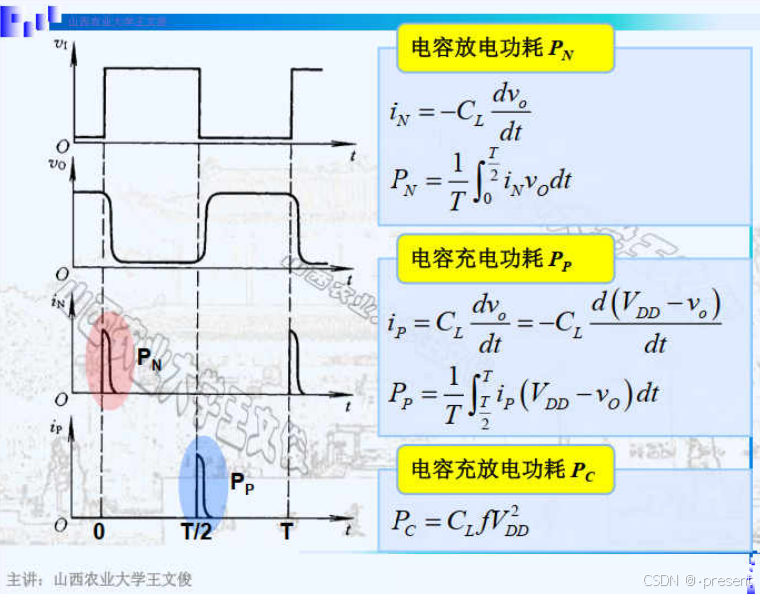

另一个就是我们之前没有谈及的负载功耗

负载也有电容部分,对其充放电的过程,就是一个做功的过程

联立充放电的两个公式(加起来),如下图所示

即可得到负载电容充放电的功耗

P

C

P_{C}

PC

动态功耗就是两个功耗的相加

不难看出,工作频率直接影响CMOS的整个功耗

所以,我们选购CPU的时候,通常也是会选主频越大的CPU,它代表了单位时间所能处理的工作量

同时这也意味着动态功耗也会越大,因此,往往现在的电脑CPU附近都会有冷却液或者电风扇在那散热

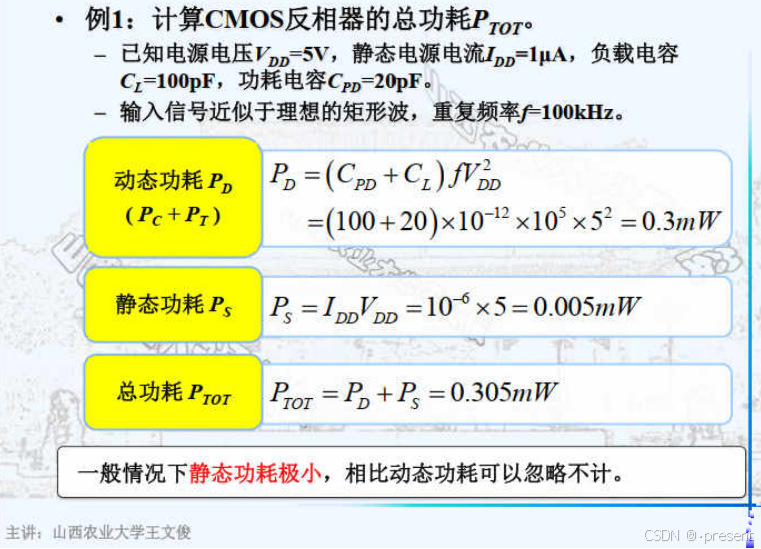

王文俊老师还给出了一道例题,可以参考着看

4.3 其它类型的CMOS门电路

为什么我们前面要这么详细介绍CMOS特性?

原因都是为了这节服务,只有了解特性,在这基础上,演变设计出来的电路才不会觉得突兀

4.3.1 其它逻辑功能的CMOS门电路

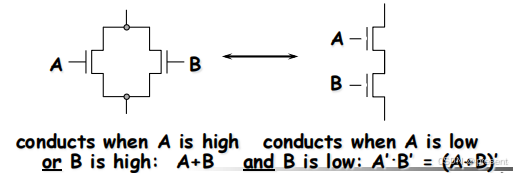

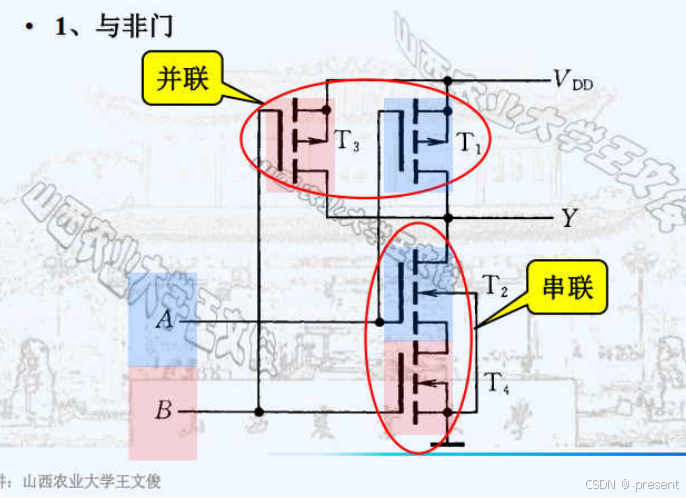

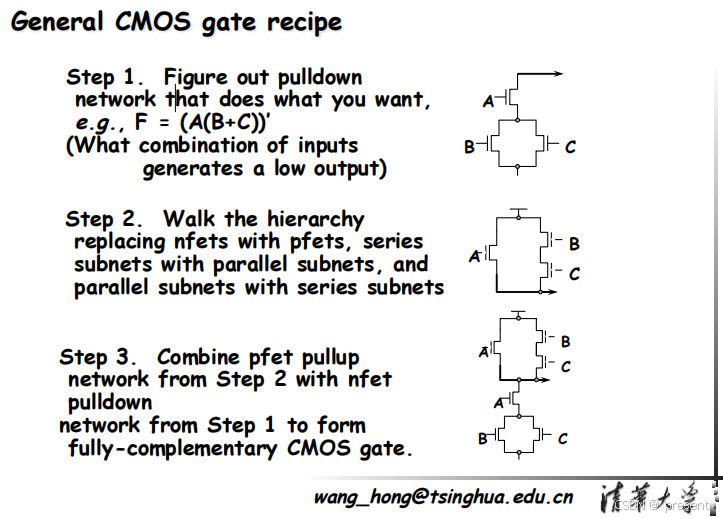

NMOS管负责下拉部分(输出强0),PMOS管负责上拉部分(输出强1),两者共同构成了我们的CMOS反相器

能否将这种设计思想延续下去,用互补电路的形式设计出其它逻辑功能的CMOS逻辑电路呢?

当输入高电平的时候,NMOS管导通;当输入低电平时,PMOS管导通

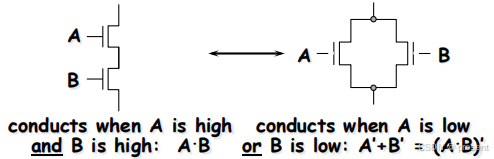

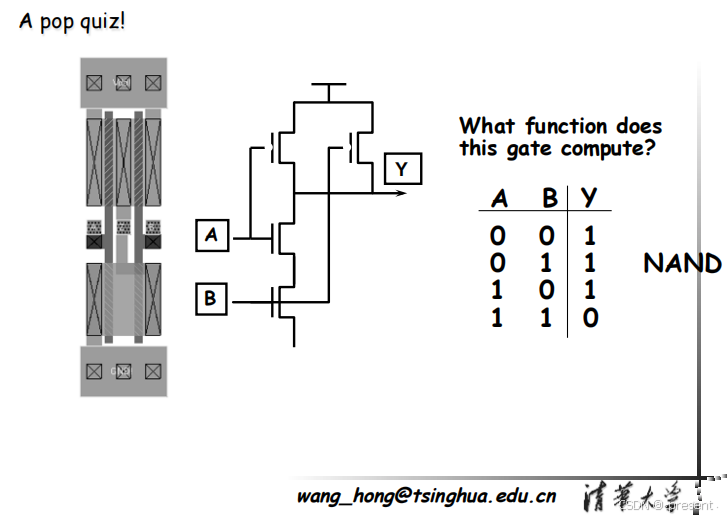

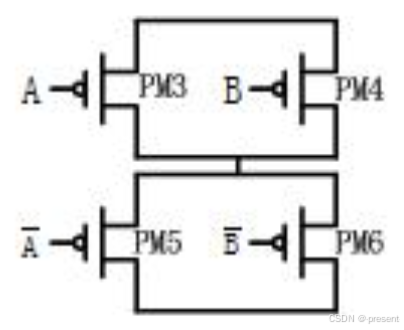

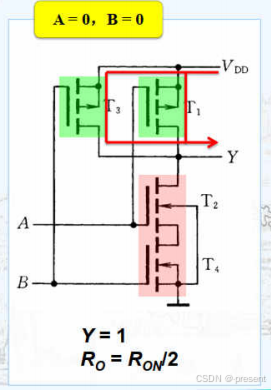

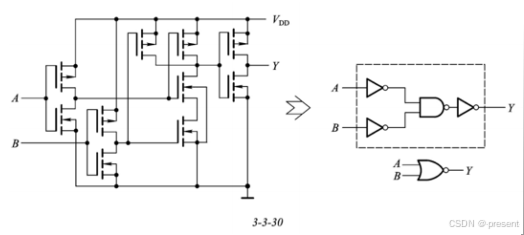

那现在假如我们想要实现与非,上拉部分和下拉部分应该怎么设计呢?

逻辑与非代表的是,两者都为1时,输出才为0;其余情况输出都为1

很直观的我们可以在下拉网络中,将两个NMOS管串连起来,只有A,B输入都为高电平,两个管子才会同时导通,输出"0"(两者都为1时,输出才为0)

而在上拉网络中,将两个PMOS管并联起来,只要有一个输入是低电平,PMOS管都会导通,输出"1"(其余情况输出都为1)

将上下拉网络组合起来,我们便成功实现与非

为什么设计出逻辑与非的功能,而不是逻辑与?

由于NMOS管是由原变量去控制,而控制导通的是下拉,所以,所有的CMOS器件在构成逻辑时,都是xx非的形式,不过,我们不用担心,有很多方法解决这个问题,最简单的在输出直接接一个反相器就好

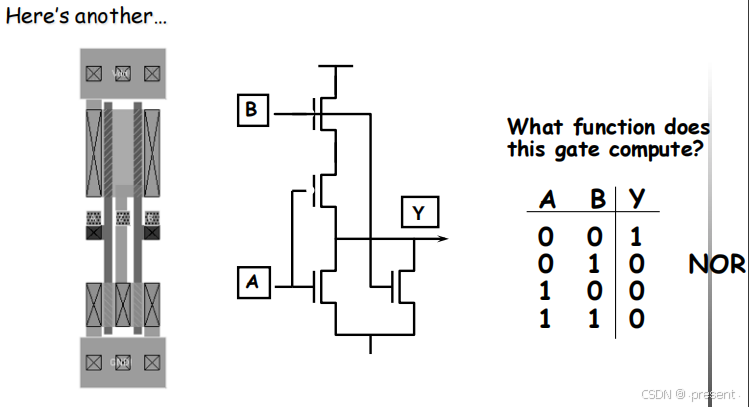

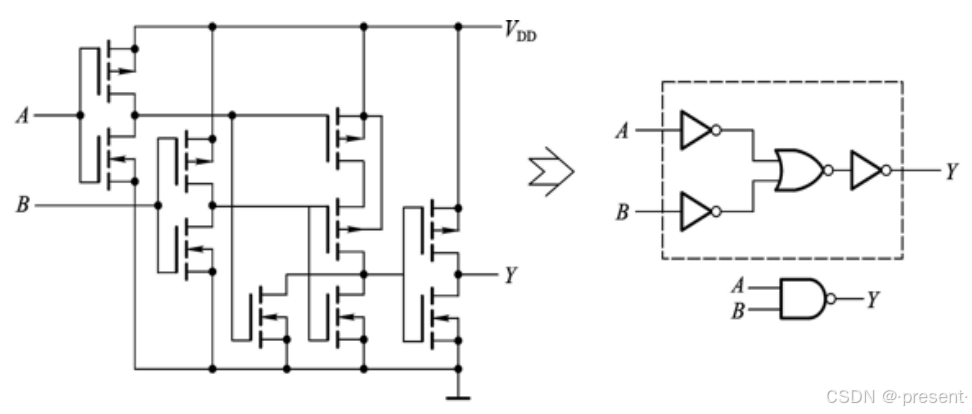

那假如我们想要实现或非呢?

也是同样的思路

逻辑或非代表的是,两者都为0时,输出才为1;其余情况输出都为0

很直观的我们可以在下拉网络中,将两个NMOS管并连起来,只要A,B输入中有一个为高电平,管子就会导通,输出"0"(其余情况输出都为0)

而在上拉网络中,将两个PMOS管串联起来,只有两个输入同时都为低电平,两个PMOS管才会同时导通,输出"1"(两者都为0时,输出才为1)

将上下拉网络组合起来,我们便成功实现或非

从上面的两个设计中,我们可以得到什么设计经验呢?

第一.和CMOS反相器一样,上拉网络负责的是输出"1",下拉网络负责的是输出"0",当一个网络导通时,另一个网络就是关闭的,两者结合,实际上就覆盖了真值表的所有输入,两者本质上是互补的关系,利用了我们大名鼎鼎的摩根定理

第二.NMOS管负责构成下拉网络,PMOS管负责构成上拉网络,原因就是我们前面提到过的NMOS管输出强"0"弱“1”,PMOS管输出强"1"弱“0”

第三.输出是xx非的形式

有了上述三个设计经验,我们其实就可以自信设计出任意其它逻辑功能的CMOS门电路

1.输出写成非的形式(经验三)

2.用NMOS管设计下拉网络,与则为串联,或则为并联(经验二)

3.串变并,并变串,转成上拉网络,两者拼在一起,over(经验一)

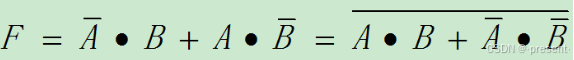

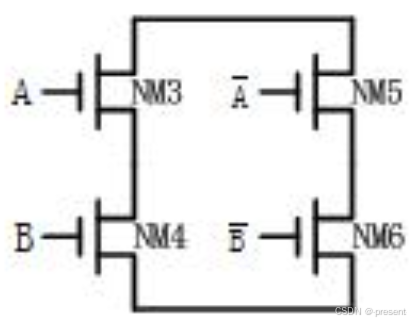

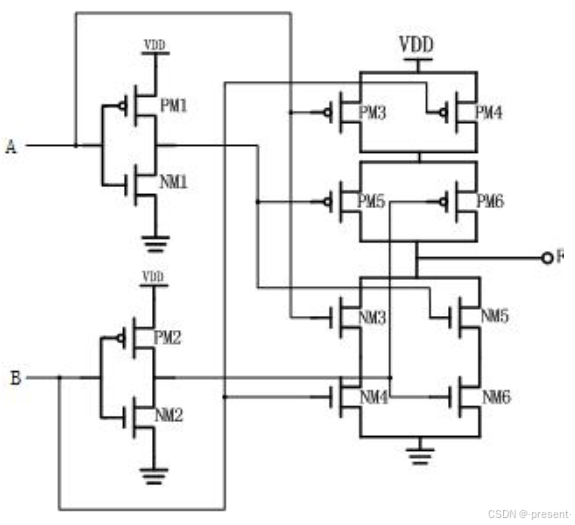

检验自己是否真的明白,可以用CMOS工艺自己设计一个异或门(PS:设计方法并不唯一)

这里给出来其中一种

先实现一个同或门,然后在输出再加一个反相器

第二步,设计下拉网络,相与用两个NMOS管串联,相或,将两路输出并联

第三步,根据互补关系,串转并,并转串,设计出对应的上拉网络

最后,将上拉网络和下拉网络结合在一起,便得到我们的异或门

4.3.2 带缓冲级的CMOS门电路

在4.3.1节我们已经可以实现任意逻辑功能的CMOS门电路,但是这样就大功告成了吗?

我们说还不够,我们之前设计的电路还有一个重要的问题没有解决

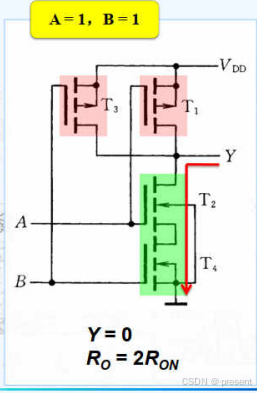

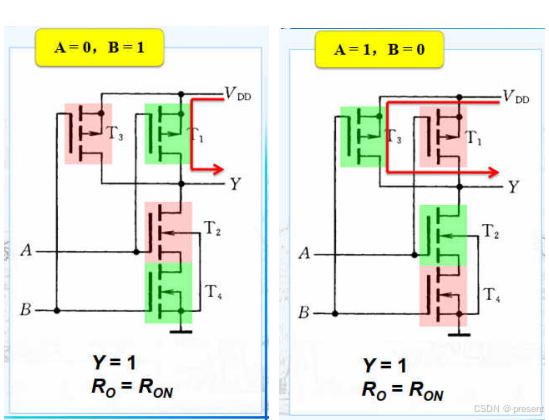

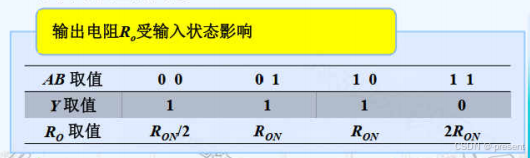

简单拿我们之前设计的与非门电路来举例子

当输入同时为0时,上面两个PMOS管同时导通,由于并联的关系,所以输出电阻为

R

2

\frac{R}{2}

2R,其中R为一个MOS管的等效电阻

当A,B两个输入同时都是高电平时,下面两个NMOS管同时导通,此时输出电阻为2R

当输入中一个为1,另一个为0时,等效输出电阻又变为R(上拉网络和下拉网络都不导通)

这样有点尴尬,我们说在下一级看来,我们的门电路会是一个带内阻的电压源,但现在这个电压源内阻会随着输入状态而发生改变,这显然不是我们想要的

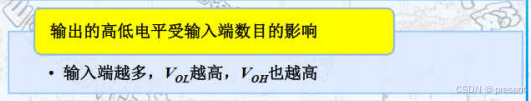

这还不是最大的问题,有一个致命的问题,此时我们的门电路又出现了电平偏移问题,而且随着输入端的数目增多,偏移情况会变得更加严重

还是拿与非门来举例子,原来输出"0",只是需要两个NMOS管导通,但是输入端假如变为三个的话,却要三个NMOS管同时导通,抬高输出的低电平也就越高

电平偏移明显不是我们想要的,我们想要的是输出的高低电平应该保持一致(Getting bits under contract),而且尽量是高质量的数字信号输出VCC和地

解决办法就是在输入端和输出端都加一个反相器,反相器的噪声容限可以将结果重新拉回高质量的0和1

当然,此时就相当于使用了摩根定律(输入取反,然后符号改变),实际上整个模块由与非门变成了或非门

假如我们想要一个与非门,主体的逻辑部分应该用或非门

所以,为什么我们之前要讲解那么多CMOS反相器的特性?

在实现其它逻辑功能的CMOS电路借鉴的是它的互补思想

改善信号质量,也是用CMOS反相器(作为缓冲级)

正是因为重要,所以才要重点去讲

当然,输入输出加了反相器之后,电路的分析就会变得更复杂,此时假如要分析电路的功能,需要分模块去分析,每次分析时,我们都要问自己这两个问题

1.这个模块是做什么的,输出是什么?

2.再分析输入是什么?

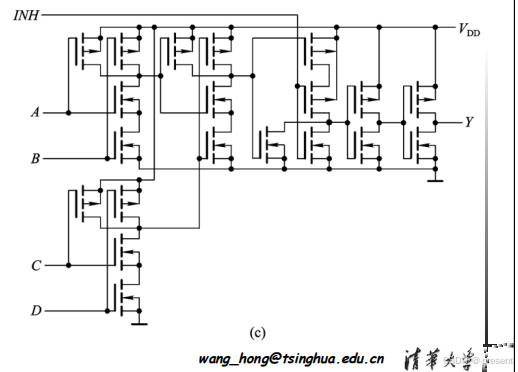

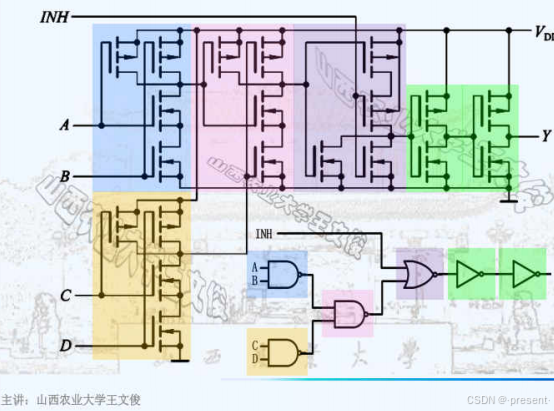

比如下图中的电路

我们应该从输出反过来一步步分析

首先是绿色模块,两级反相器

然后是紫色模块,直接看下拉部分,NMOS管并联,确定它是一个或非门

确定它是一个或非门后,再看输入是什么?

一个是INH信号,另一个是前一级模块

然后看粉色模块,直接看下拉部分,确定它是一个与非门,它的输出作为我们紫色模块或非门的输入

确定它是一个与非门后,再看输入是什么?

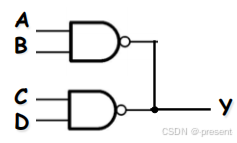

剩下就非常容易了,AB做与非,CD做与非,然后两个输出分别做粉色部分与非门的输入

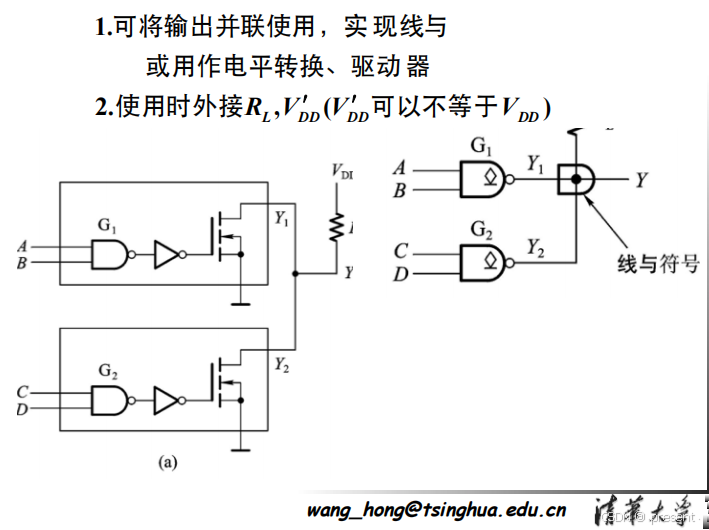

4.3.3 OD门(Open Drain)

在4.3.1节我们完善了门电路设计的缺陷,在输入和输出加上缓冲级,使输出信号重新变为高质量

但是这样就没问题了吗?

还没有那么简单

现在我们把两个与非门直接输出连在一起,想要实现逻辑与的功能

可以实现吗?

我们说可以实现,因为这样当上面输出1,下面输出0的时候,就相当于把输出0的门电路直接短路了

但是有问题吗?

我们可以把对应的门电路展开来看

当上面输出1,下面输出0时,分别都会有两个PMOS管和两个NMOS管导通,但是此时又没有像我们单刀开关一样,接一个限流电阻保护电源,最后导致的直接下场就是电源直接烧掉

于是,我们假如想要实现输出直接相连,实现逻辑与的功能(我们也把这种运算称为线与),采取这样的电路肯定是不行的!

造成这样的原因是什么呢?

直观上来说,就是输出逻辑“1”时,电源有通路和地直接相连,又没有限流电阻保护

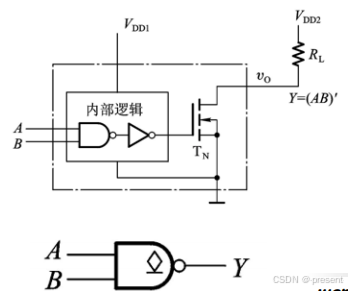

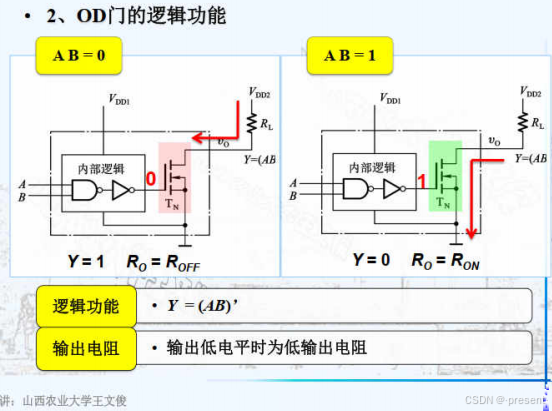

于是有一些“狠人”,直接把上面的PMOS管删掉,只留下来NMOS管,这样门电路直接没有电源,就不怕电源烧毁了,然后把这种漏极开路的门电路称为OD门

但是这样就无法输出高电平,于是对于OD门来说,每次使用OD门,都必须外接上拉电阻和电源,如图中的

R

L

R_{L}

RL

OD门的出现也验证了我们之前所说的观点,电路不是一成不变的,需要灵活变通,NMOS管和PMOS管可以互换实现跟随器,PMOS管甚至可以直接删掉以实现OD门,每一个器件的工作状态都有着它自己的用武之地.

但是

R

L

R_{L}

RL的出现,又会带来之前单刀开关遇到的问题

太小,限流能力弱,电流太大,容易把NMOS管烧掉 (充当限流电阻)

太大,作为电压源内阻太大,带负载能力就太弱 (充当电源内阻)

所以 R L R_{L} RL的确定也是一个技巧活

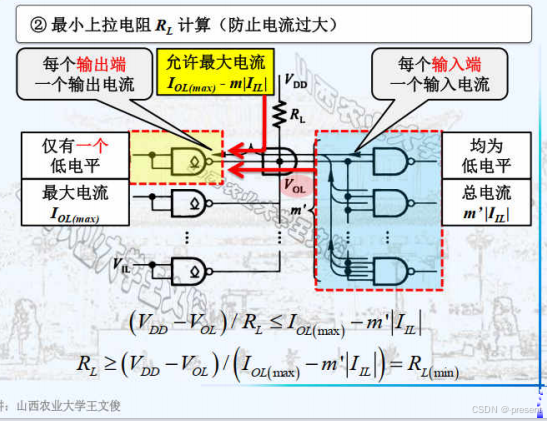

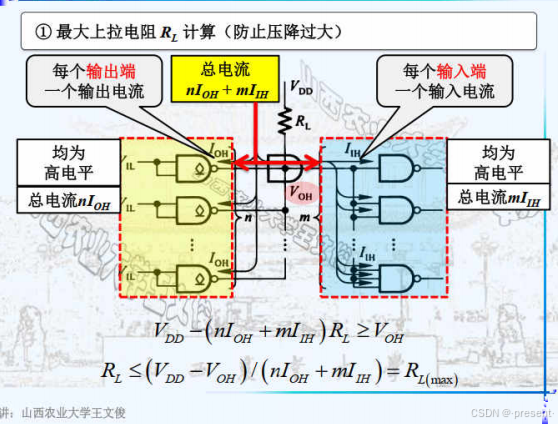

如何确定 R L R_{L} RL的阻值呢?

核心思想也是我们上面提到的两个问题,解决上述两个问题遇到的极限问题,自然就确定了阻值

当充当限流电阻时,极限情况,就是一个门电路承担流过的所有电流(来自电源支路的电流和后面所有门电路的输入电流)

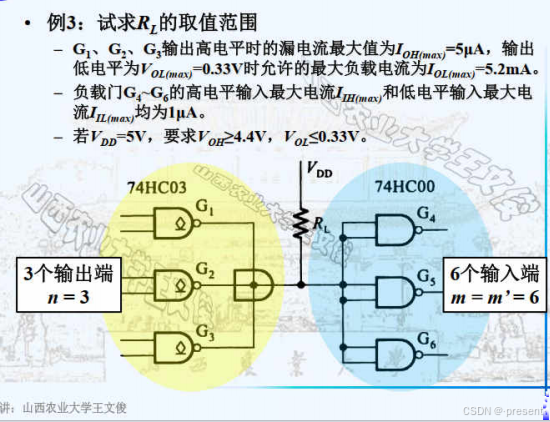

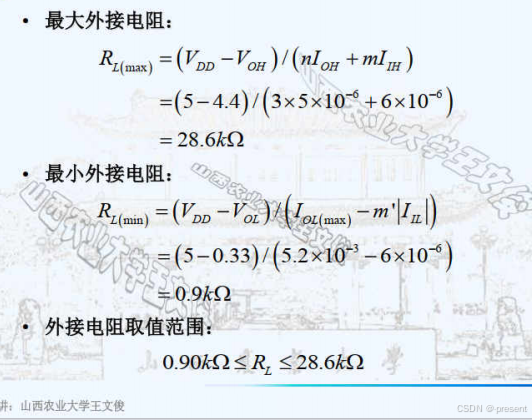

PS:一个输入端一个输入电流,如下图:m = 1 + 2 + 3 = 6

当充当电压源内阻时,我们希望输出的"1"是高质量的,尽量接近电源电压,有一定的负载能力

通过两种情况的讨论,便确定了

R

L

R_{L}

RL的阻值范围

王文俊老师也给出了对应的例题,供大家参考学习

那说了这么多OD门的设计难点,它有什么用呢?我们用它来做什么?

假如用过STM32或者51单片机的同学可能就对OD门有了解了

在我们的I2C总线设计时,利用的就是OD门线与功能,所有的外设通过OD门直接挂接在总线上,此时总线维持高电平不变

只有外设被选中的时候,总线才会被拉至低电平,CPU此时就知道有外设准备就绪,两者就可以进行通讯了

通过这样的设计,才实现了总线只有一个Master,多个Slave从设备的通信

除此之外,OD门还可以实现电平转换的功能

还是拿STM32单片机举例,在设计电路时不论是单片机还是外设芯片或是负载,每个个体的逻辑电平可能是不一样的,遇到这种情况,需要作电平的匹配,就用到了开漏输出模式

当MCU供电为3.3V,开漏输出引脚上接外部5V电源时,因为N-MOS不导通时,阻值非常大(导通沟道都没有),所以此时IO引脚上的电压就接近5V电压,从MCU的角度来说,减轻了MCU的负担

并且通过这种方式抬高了输出电平,通过调整电源,还可以输出不同的电压值

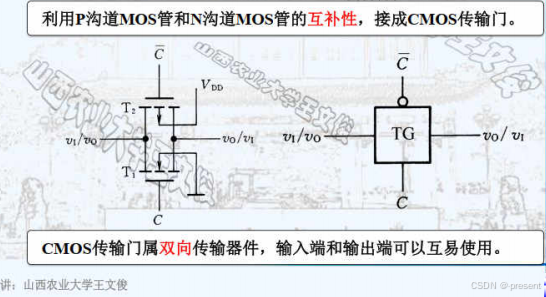

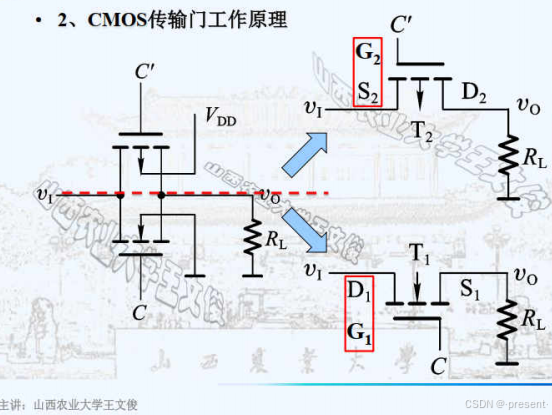

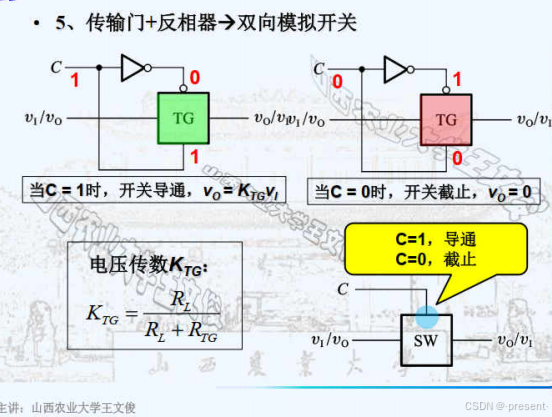

4.3.4 传输门

除了上述我们提到的CMOS门电路作为开关外,还有另外一种形式也可以作为开关

它利用的也是CMOS互补的特性,我们把它称作传输门

假如从中间割开,其实它和我们的CMOS门电路几乎没有区别

上面是PMOS管,下面是NMOS管

唯一需要注意的是,两个管子栅极的输入电压有了限制,NMOS输入电压假如是C,则PMOS输入电压是C的反,这意味着不存在两者输入同时为0或者同时为1的情况

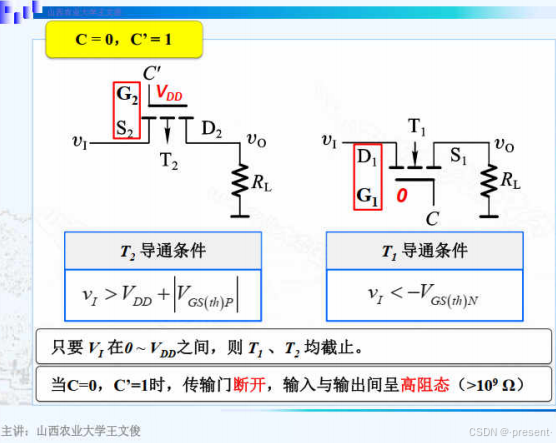

当

C

=

0

C= 0

C=0,

C

′

=

1

C^{'} = 1

C′=1时,两个管子同时截止,相当于开关断开

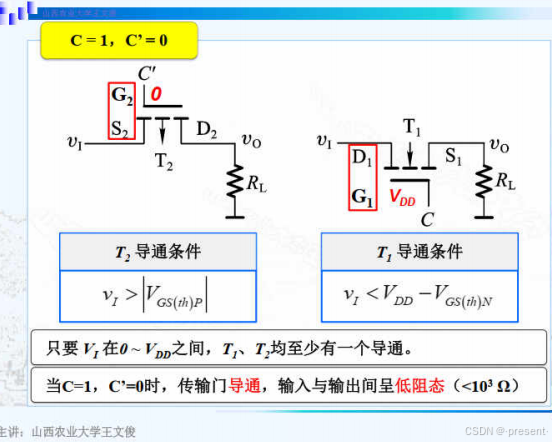

当

C

=

1

C= 1

C=1,

C

′

=

0

C^{'} = 0

C′=0时,两个管子同时导通,相当于开关闭合

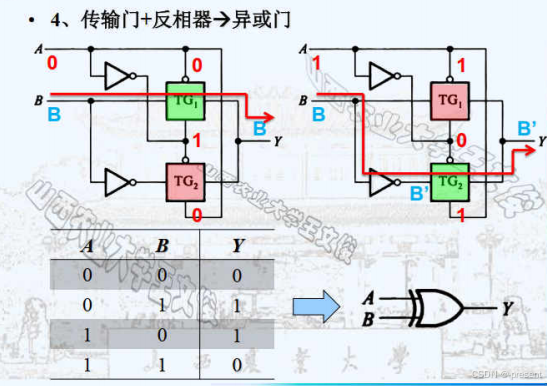

既然传输门可以作为开关使用,而且实际还是一个双向开关,那自然也可以用它来设计很多电路

这里给出它用来设计异或门的电路,整个设计还是非常巧妙的,总共用到了两个反相器,两个传输门,2*4 = 8个MOS管,相较于我们前面CMOS设计异或门用到了12个来说,一下子减少了4个管子

传输门导通的电阻和负载电阻相比,哪个更大?

答案是负载电阻远大于传输门导通电阻,否则就谈不上充当开关

如何使NMOS接 C C C,PMOS接 C ′ C^{'} C′呢?即如何保证两者的输入始终相反?

答案也很简单,一个反相器就可以解决

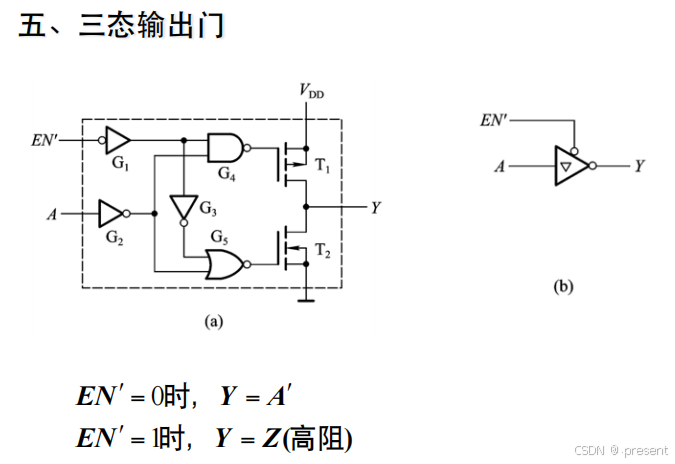

4.3.5 三态门

在上述CMOS设计的电路中,输出要么是“1”,要么是"0"

当然这也是我们想要的

但是有一种情况,其实我们一直在回避,没有讨论

那就是CMOS管没有输入的时候,此时两个管子都相当于断开,输出电阻非常大,静态功耗接近于0

我们把此时的输出称作为高阻态Z

那我们能不能设计一种电路可以输出高阻态?

答案是可以的!这样的门电路我们就把它称作为三态门(三态分别是指“1”,“0”,高阻态)

不难看出,

E

N

′

EN^{'}

EN′相当于一个选通信号

当它为1时,经过反相器

G

4

G_{4}

G4,输出一个0接到与非门

与非门只要有一个0,输出必定为1,不管另外一个输入是什么

再经过反相器

G

3

G_{3}

G3,输出一个1接到或非门

或非门只要有一个1,输出必定为0,不管另外一个输入是什么

此时最后的反相器的两个管子同时截止,输出的也就是高阻态了

当

E

N

′

=

0

EN^{'} = 0

EN′=0时,不管是与非门,还说或非门,输出都是看输入A是什么,此时就相当于一个反相器

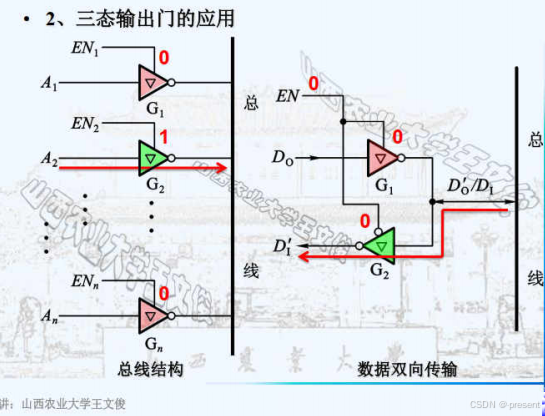

那为什么我们需要高阻态?它有什么作用?

无论我们是用面包板插线还是PCB板,一条线和另外一条线相连之后,就始终固定在一起,此时只要有电源接通,就必定会有电压电流关系

如何切断这个联系呢?

答案就是三态门,除非三态门打开,否则模块之间互不干扰

从而实现物理电气上保持相连,但是逻辑上是断开的

比如我们买笔记本,假如要接外设,可能就有很多个USB接口,我们希望这些USB接口之间是一个什么关系?

1.访问某个特定USB接口时,其它设备不会干扰我

2.我不需要拔下来其它外设的USB接口,物理上它们还是相连的,但是互不干扰

此时利用到的就是我们的三态门

其实三态门利用最为经典的一个场景,就是我们51单片机的总线

多个外设通过三态门挂接在总线上,只有三态门导通,外设才可以往总线上发消息(CPU通过总线向外设发消息)

外设与外设之间虽然物理上是直接相连的,但是因为三态门的缘故,逻辑上并不直接相连

而每一个外设,我们说,都有着它自己唯一的外设地址

这个地址是怎么来的?

E

N

′

EN^{'}

EN′选通端为1代表选中这个外设,其余

E

N

′

EN^{'}

EN′都为0,不就相当于对外设进行了编码?

而且这个编码也的确是唯一的,直接就是我们前面提到过的最小项的形式,且这个地址的长度决定于外设的数目

最小项的编码 与 地址的编码 一一对应

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?