rst?

`timescale 1ns/1ns

module main_mod(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

input [7:0]c,

output [7:0]d

);

wire [7:0]m,n;

sub_mod mod_ab(

.clk(clk),

.rst_n(rst_n),

.data_a(a),

.data_b(b),

.data_c(m)

);

sub_mod mod_bc(

.clk(clk),

.rst_n(rst_n),

.data_a(b),

.data_b(c),

.data_c(n)

);

sub_mod mod_mn(

.clk(clk),

.rst_n(rst),

.data_a(m),

.data_b(n),

.data_c(d)

);

endmodule

module sub_mod(

input clk,

input rst_n,

input[7:0]data_a,

input[7:0]data_b,

output reg[7:0]data_c

);

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

data_c<=0;

end

else if(data_a>data_b)begin

data_c<=data_b;

end

else begin

data_c<=data_a;

end

end

endmodule四位数值比较器

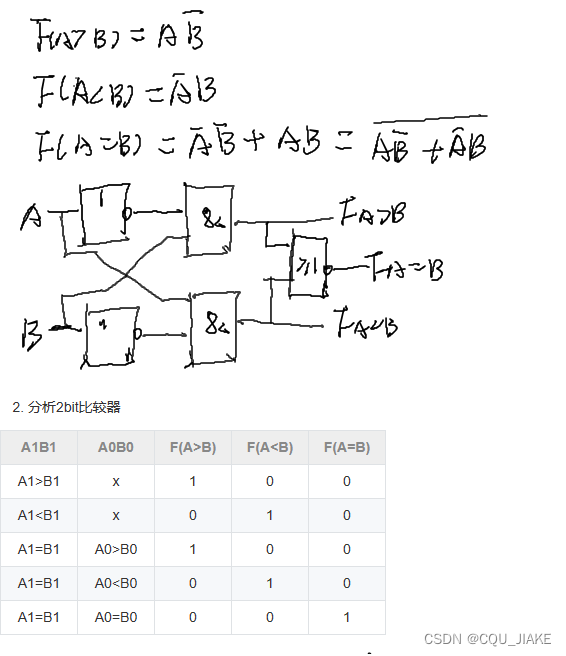

a与b都只有01

如果a要大于b,那么a为1,b为0,y2=a&!b

如果b要大于a,那么b为1,a为0,y0=!a&b

如果相等,那么y2,y0都不成立,y1=!(y2|y0)

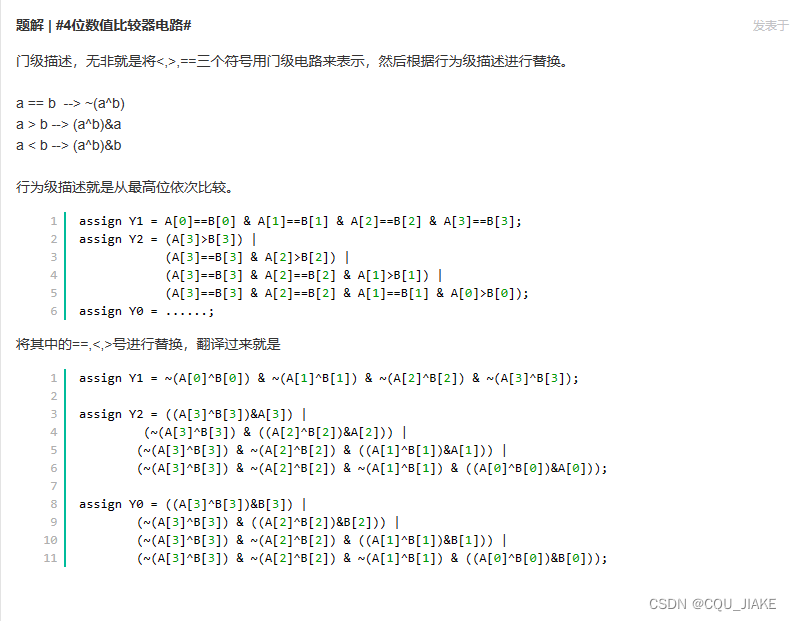

写一个每位的比较器模块,然后在主模块中不断循环调用

`timescale 1ns/1ns

module comparator_4(

input [3:0] A ,

input [3:0] B ,

output wire Y2 , //A>B

output wire Y1 , //A=B

output wire Y0 //A<B

);

wire y2temp[0:3];

wire y0temp[0:3];

wire y1temp[0:3];

genvar i;

generate

for(i=0;i<=3;i=i+1)

begin:loop

compare_1 comparei(

.a(A[i]),

.b(B[i]),

.y1(y1temp[i]),

.y2(y2temp[i]),

.y0(y0temp[i])

);

end

endgenerate

assign Y2=y2temp[3]|(y1temp[3]&y2temp[2])|(y1temp[3]&y1temp[2]&y2temp[1])|(y1temp[3]&y1temp[2]&y1temp[1]&y2temp[0]);

assign Y0=y0temp[3]|(y1temp[3]&y0temp[2])|(y1temp[3]&y1temp[2]&y0temp[1])|(y1temp[3]&y1temp[2]&y1temp[1]&y0temp[0]);

assign Y1=y1temp[3]&y1temp[2]&y1temp[1]&y1temp[0];

endmodule

module compare_1(

input a,

input b,

output y1,

output y2,

output y0

);

assign y0=(!a)&b;

assign y2=(!b)&a;

assign y1=!(y0|y2);

endmodule声明自模块,带;,带类名

与,或,非,异或

a^b保证a与b不同,再与上a,表示a为1,b与a不同,b为0,则a>b

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?