一、实验目的

1) 熟悉全加器的逻辑结构和电路实现方法。

2) 掌握n位行波进位补码加法/减法器的逻辑结构和电路实现方法。

二、实验要求

1) 做好实验预习,复习n位行波进位补码加法/减法器的原理,掌握实验元器件的功能特性。

2) 按照实验内容与步骤的要求,独立思考,认真仔细地完成实验。

三、实验电路

本实验使用的主要元器件有:与门、或门、异或门。

逻辑门电路的信息:

| 逻辑门电路 | 虚拟实验系统中的名称 | 符号 | 备注 |

| 与门 | ANDgate |

| |

| 或门 | ORgate |

| |

| 非门 | NOTgate |

| |

| 与非门 | NANDgate |

| |

| 异或门 | XORgate |

|

引脚的信息:

| 逻辑门电路 | 虚拟实验系统中的名称 | 符号 | 备注 |

| 输入引脚 | Pin |

| 使用点击工具点击可改变输入值为0/1 |

| 输出引脚 | Pin |

|

四、实验原理

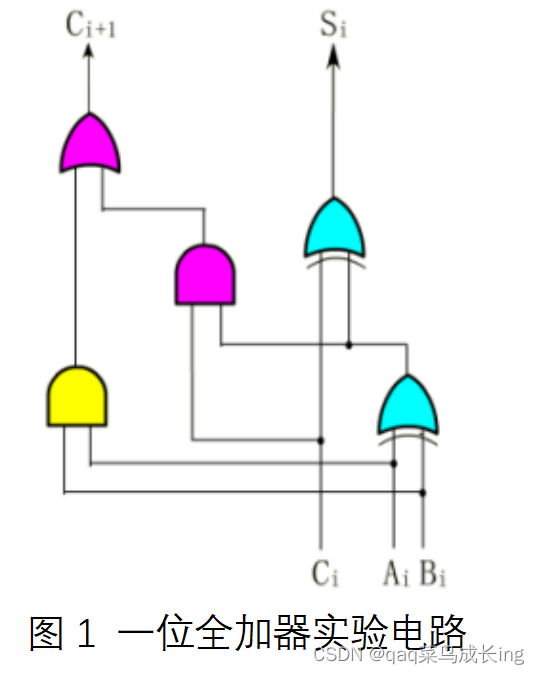

一位全加器FA有三个输入量:两个二进制数字 Ai、Bi 和一个低位的进位信号 Ci ,这三个值相加产生一个和输出 Si 以及一个向高位的进位输出 Ci+1 ,其逻辑方程如下:

Si=Ai ⊕Bi ⊕Ci

Ci+1=AiBi+(Ai ⊕Bi)Ci

五, 全加器

如下就是一个全加器

根据实验要求搭建实验电路如下

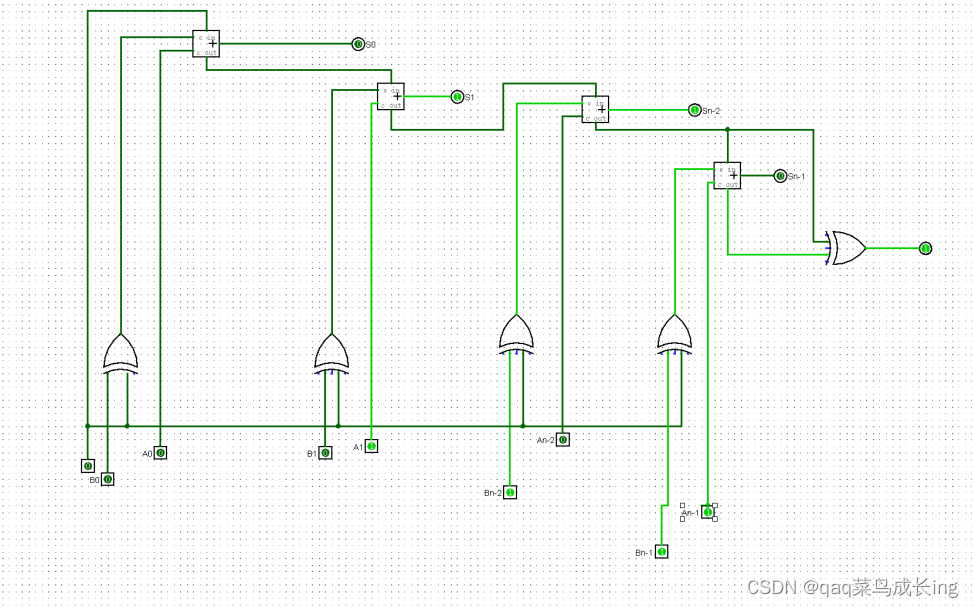

- 运行Logisim,从左边的实验设备列表选取所需组件拖到工作区中,按照图1搭建4位行波进位补码加法/ 减法器(其中最高位是符号位,其他3位是数据位) 的实验电路。运算结果(S3-S0 )和溢出检测结果使 用输出引脚显示出来。 A=+101,B=+010。求A+B= 0111 。请用搭建的电路图验证并附图。

A=0101

B=0010

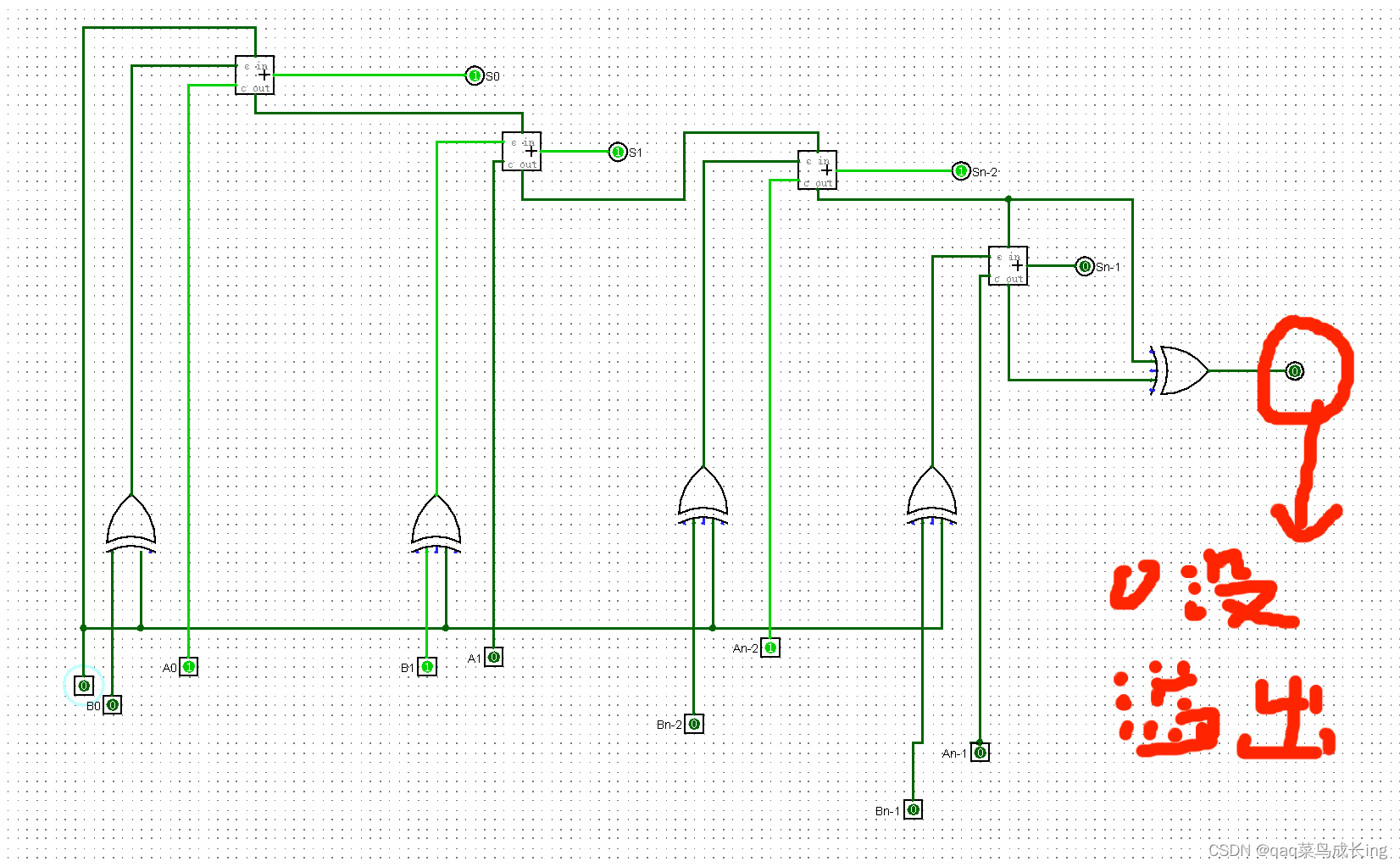

2. A=+101,B=-010。求A+B= 0011 。请用搭建的电路图验证并附图。

如果是正数,补码等于反码等于原码

如果是负数, 补码等于反码+1,而反码等于原码按位取反(符号位不变)

A的补码等于0101

B=1010,B的反码等于1101,补码等于1101+1=1102(往前进一位为1110)

如上,结果也是没溢出

如果是正数,原码反码补码相等

如果是负数,补码等于反码+1,反码等于原码按位取反(符号位不变)。

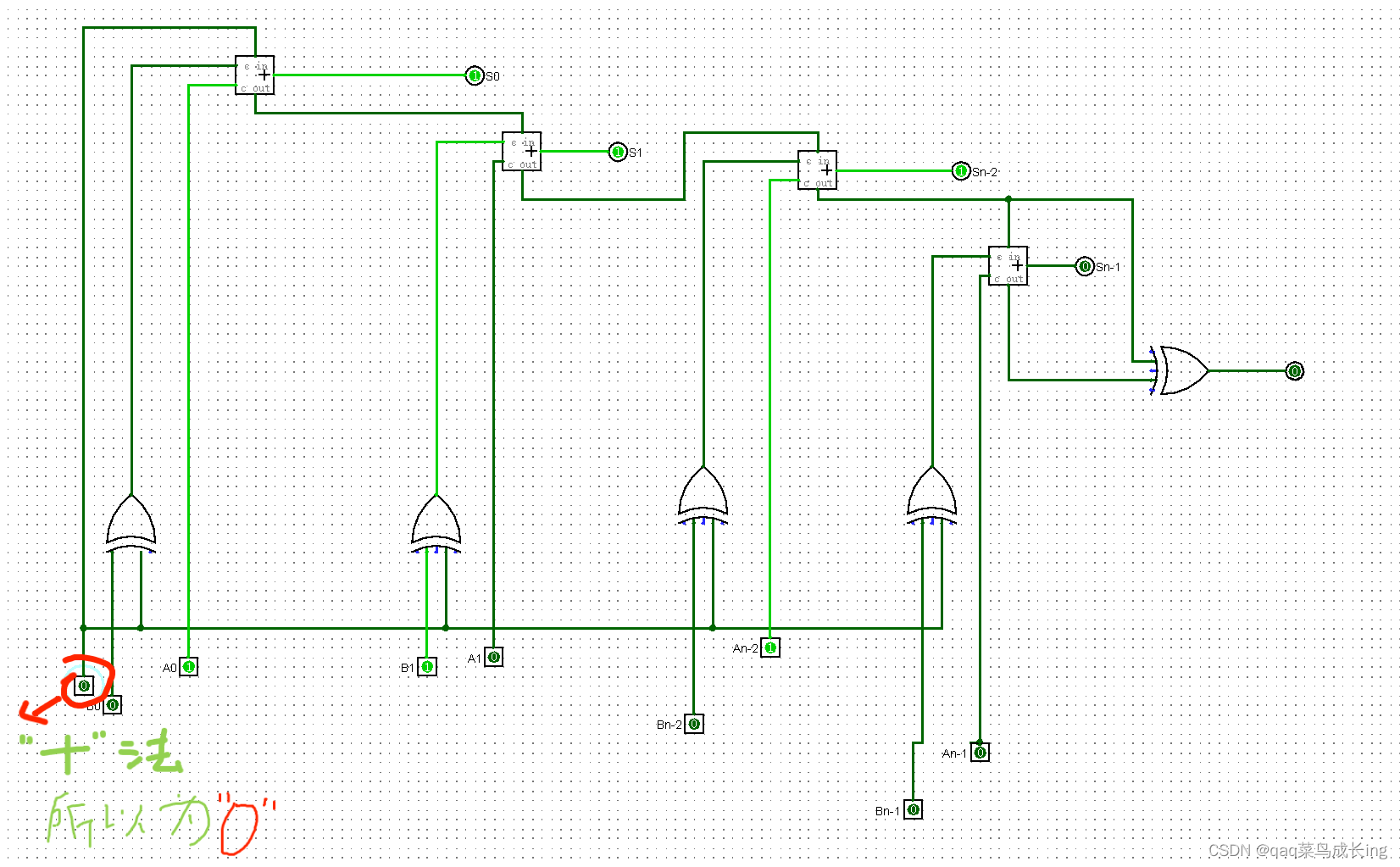

M=0时,B与0做异或,得到B与原来一样,做加法;

M=1时,B与1做异或,相当于对B按位取反,做减法。

本文介绍了全加器的逻辑结构和电路实现,包括n位行波进位补码加法/减法器的实验要求和原理,重点讲述了如何在Logisim虚拟实验系统中利用与门、或门和异或门搭建4位加法器进行实际操作,包括两个示例计算过程。

本文介绍了全加器的逻辑结构和电路实现,包括n位行波进位补码加法/减法器的实验要求和原理,重点讲述了如何在Logisim虚拟实验系统中利用与门、或门和异或门搭建4位加法器进行实际操作,包括两个示例计算过程。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?