广州大学学生实验报告

开课学院及实验室:计算机科学与工程实验室 2023年 月 日

| 计算机科学与网络工程学院 | 年级/专业/班 | 计科221 | 姓名 | 学号 | |||

| 实验课程名称 | 数字逻辑与计算机组成实验 | 成绩 | |||||

| 实验项目名称 | 数字电路实验 | 指导老师 | |||||

一、实验目的

1、熟悉 Logisim 软件的使用方法;

2、验证基本逻辑门功能,利用基础元器件库设计简单数字电路;

3、掌握组合逻辑电路的设计方法和步骤;

4、掌握时序逻辑电路设计的方法和步骤。

二、实验要求

1、电路图合理布局,适当添加标识符和注释文字,便于理解;

2、利用仿真测试,验证电路功能正确;

3、根据本次实验内容的要求,给出实验操作步骤,包括电路原理图、真值表、仿真检测图、错误现象及原因分析等内容写入实验报告。

4、 将实验报告和电路图.circ文件上交,文件名为学号,如200640001.docx、200640001.circ,所有题目的电路合在一个文件中。

三、学习资料

1、《数字逻辑与计算机组成习题解答与实验教程》第11章;

2、视频资料,视频地址:1.1 一小时玩转Logisim1_哔哩哔哩_bilibili

四、实验内容

(一)Logisim 软件的快速入门

0、下载安装 Logisim-ITA V2.16.1.0:https://sourceforge.net/p/logisimit,熟悉Logisim的基本功能、常用操作、基本组件库,学会Logisim自动生成电路的方法;

- 利用基本逻辑门设计一个3输入多数表决器;

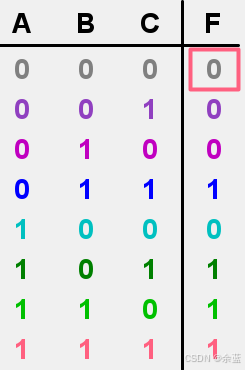

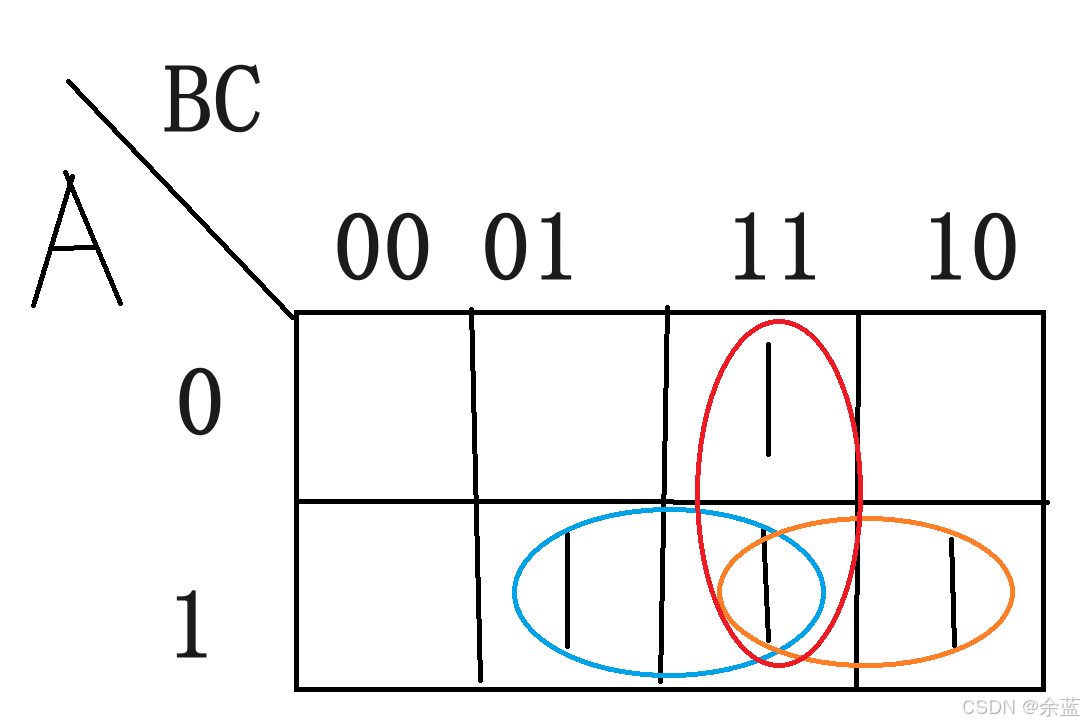

根据多数表决器的功能,当“1”为2个时,输出1,否则输出0,作出真值表,并画出卡诺图.

真值表和卡诺图如下图所示。

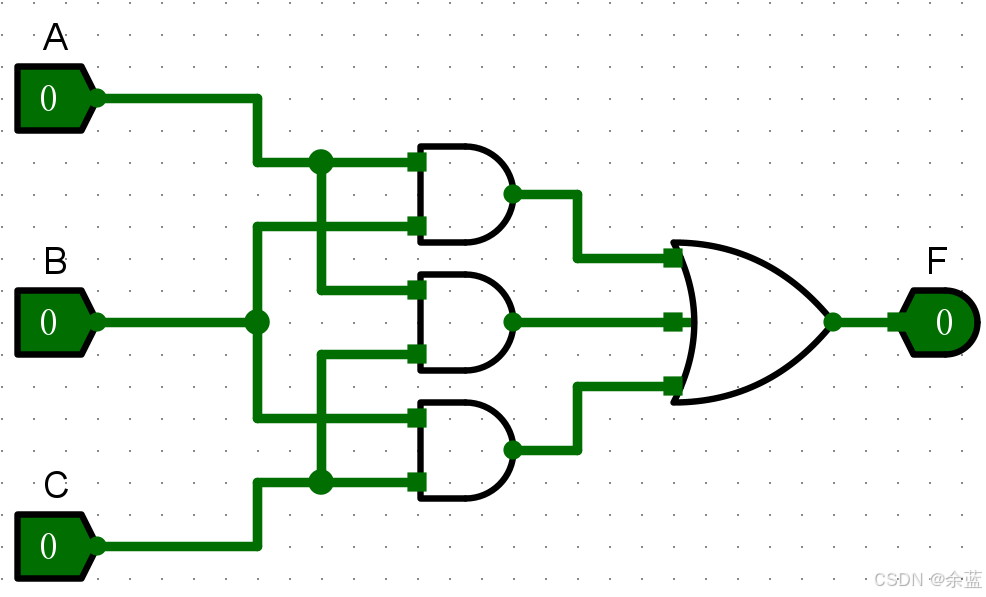

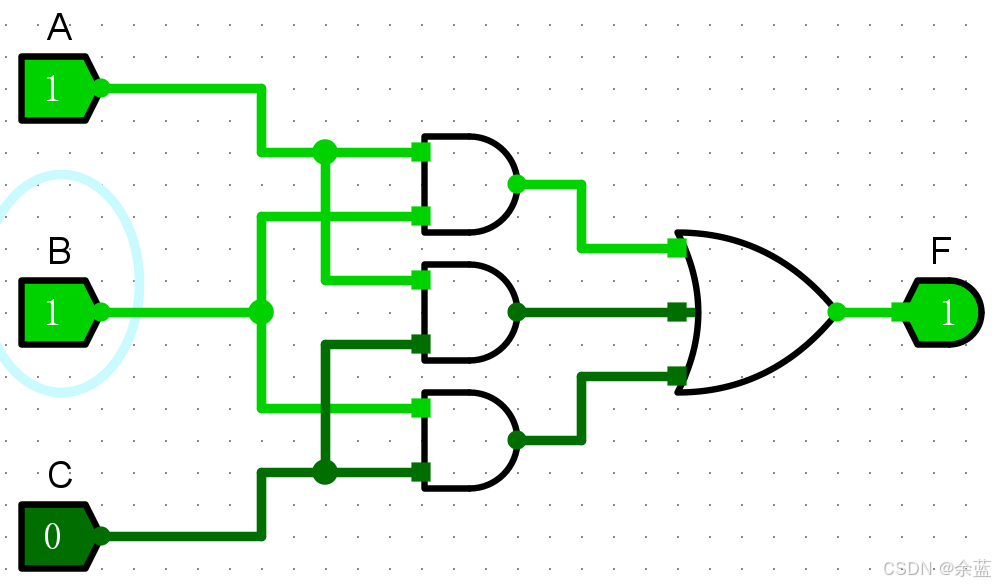

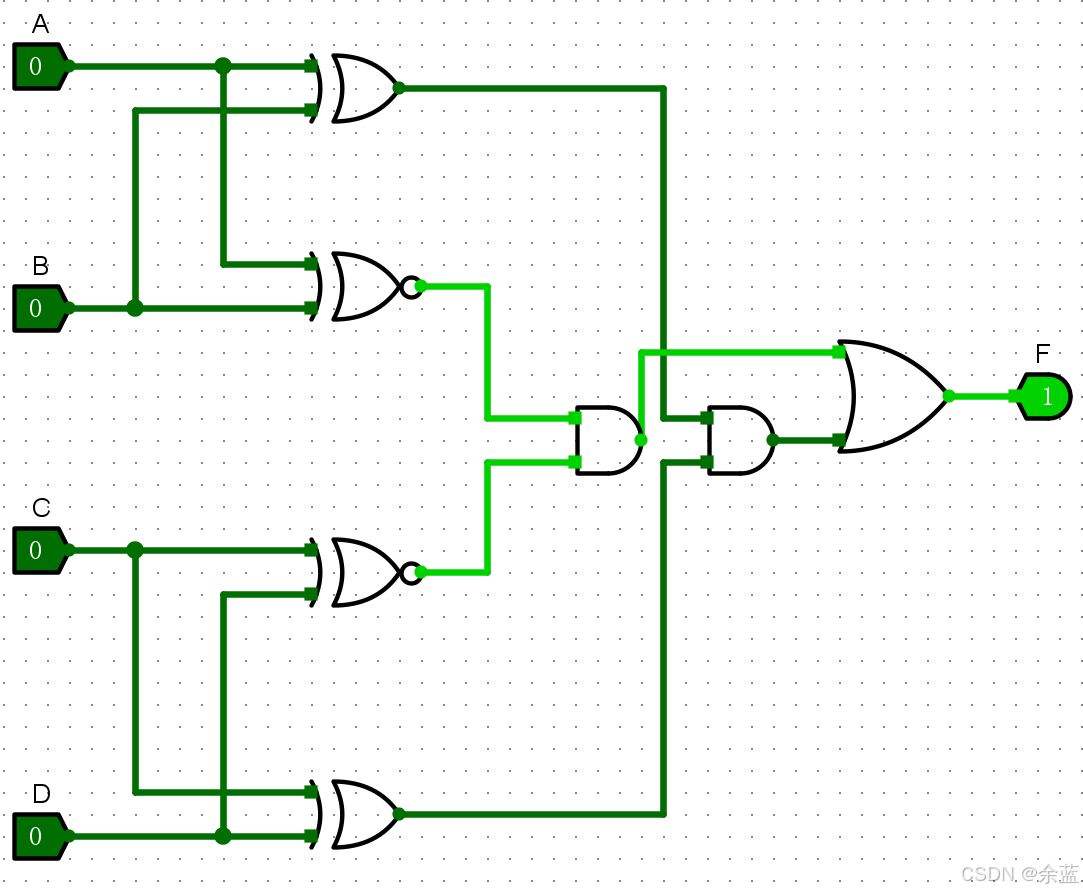

可知该多数表决器的逻辑函数为F=AB+BC+AC,由此作电路图。或门输入端个数为3个,为电路美观,将或门大小作了调整,如下图。

- 利用 CMOS 晶体管构建两输入或门,并验证其功能;

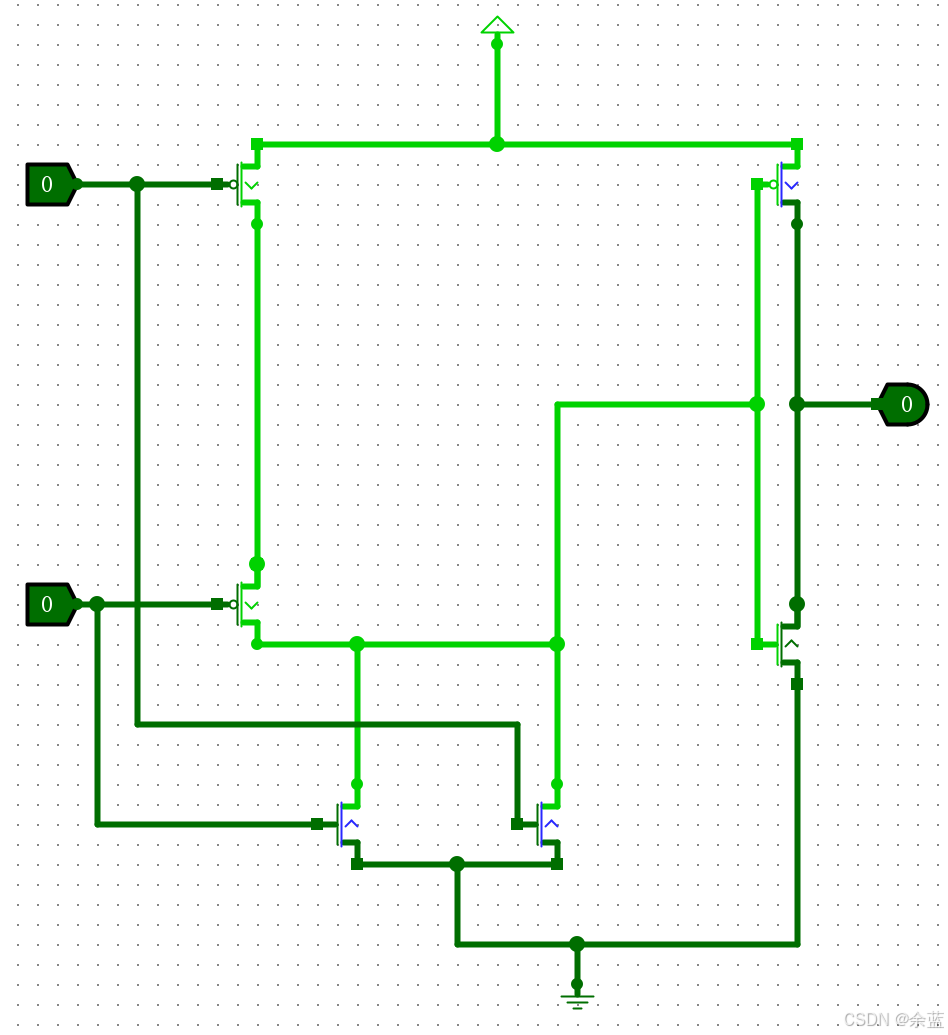

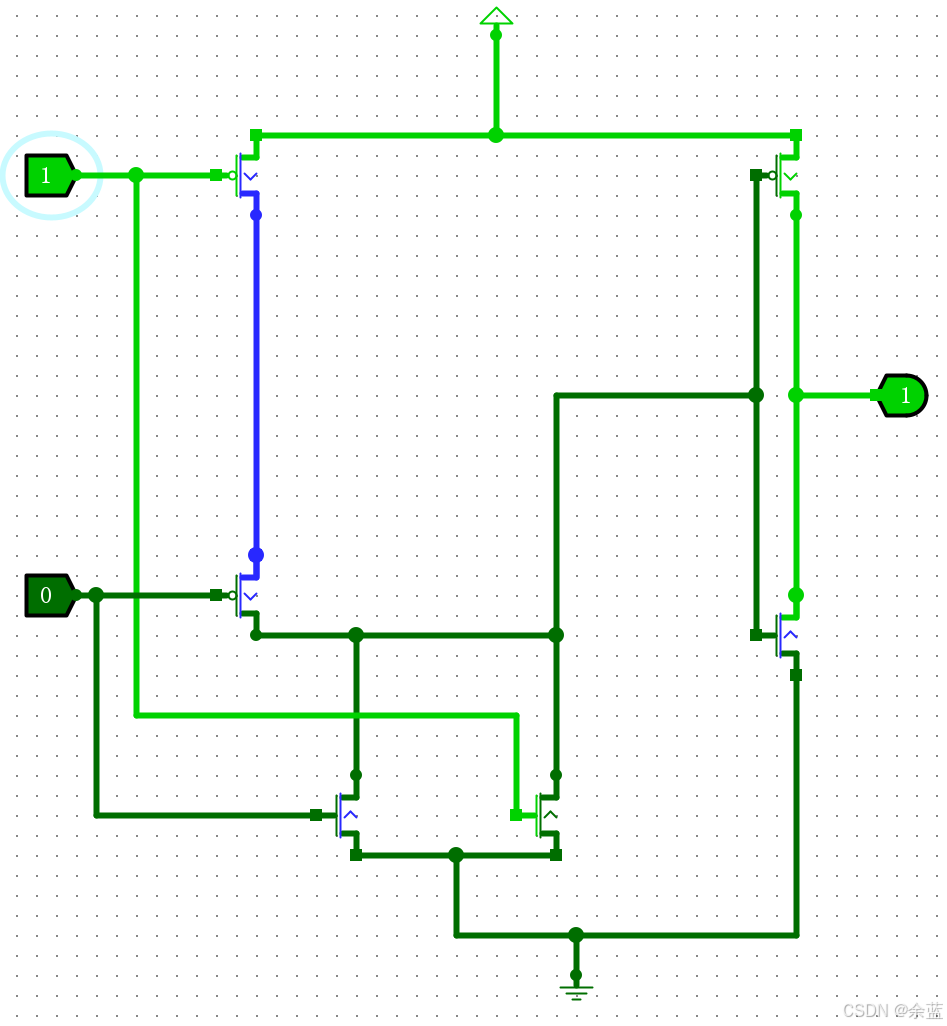

原理:由于或非门的实现更简单,所以先实现或非门,再加上非门即可。或非门的特点为当有一个输入为1,则输出0。所以两个NMOS 晶体管并联,即只要X或Y输入为1,则地线将会和输出端联通,输出低电平。PMOS晶体管串联,只有当X=Y=0时,才会输出电源的高电平。

最后,在上述电路输出端连接一个非门的CMOS电路,即可实现或门。

注意事项:设计电路时,应该注意P/NMOS晶体管中箭头^的朝向。

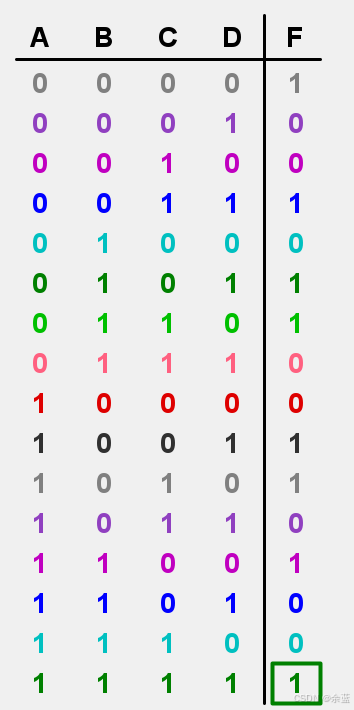

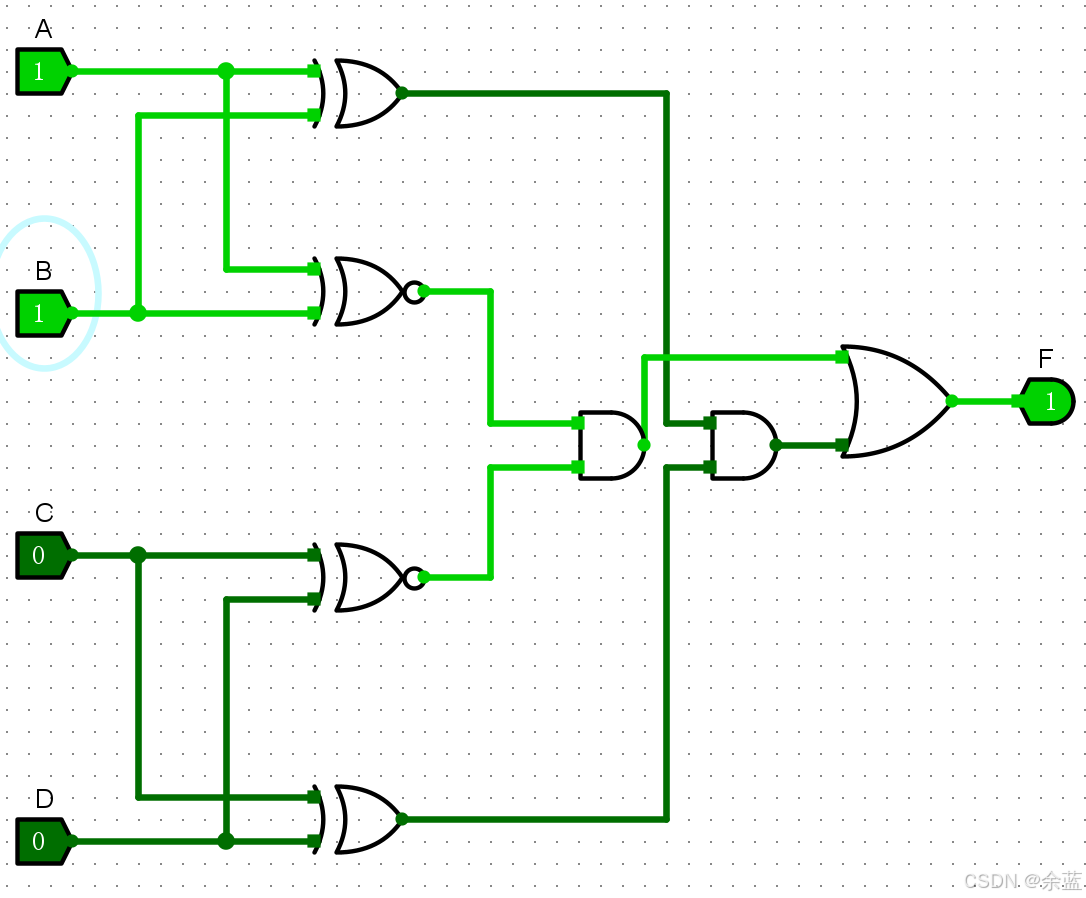

- 实现4位二进制数奇偶校验电路;

奇偶校验电路的功能为,“1”的个数为偶数时,输出1,根据上述功能列出真值表

由真值表,可得表达式

F=~A~B~C~D+~A~BCD+~AB~CD+~ABC~D+A~B~CD+A~BC~D+AB~C~D+ABCD,直接合并化简得F=(A XOR B)(C XOR D)+(A XNOR B)(C XNOR D),由此可作电路图。

测试结果如下。

- 利用 logisim 提供的 LED 矩阵显示本人姓名的字母缩写。

应该注意LED矩阵的位数和输入端的位数的匹配问题,根据实际情况做出调整。根据行列规律,通过改变输入端的值,将LED矩阵相应位置点亮即可。

(二)组合逻辑电路的设计

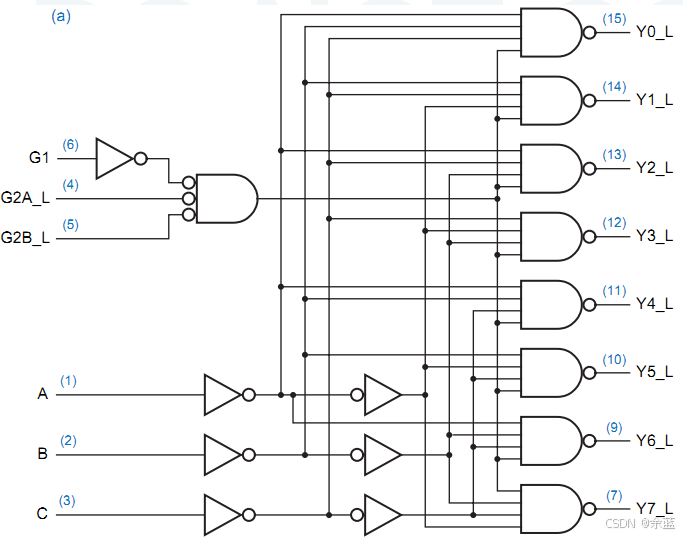

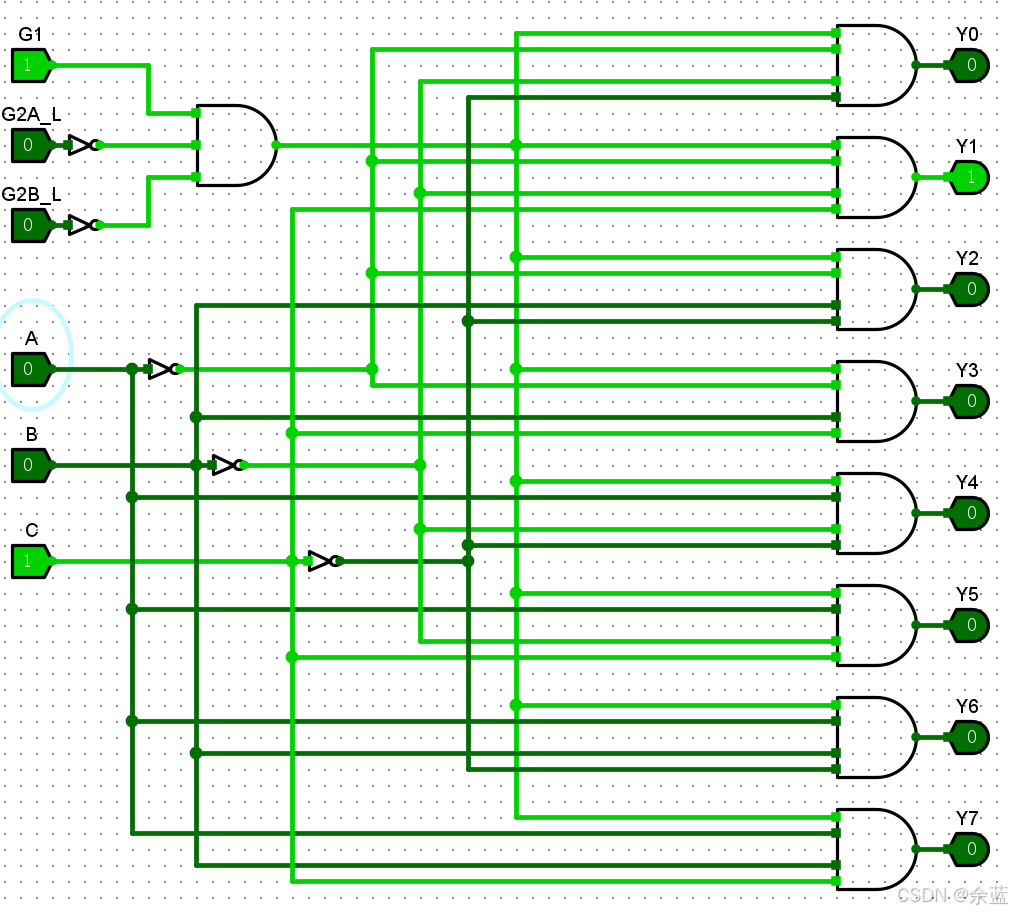

- 根据以下 3-8译码器芯片74X138的电路原理图,设计一个由逻辑门电路构成的 3-8译码器,并对电路进行仿真测试,以验证电路的功能。

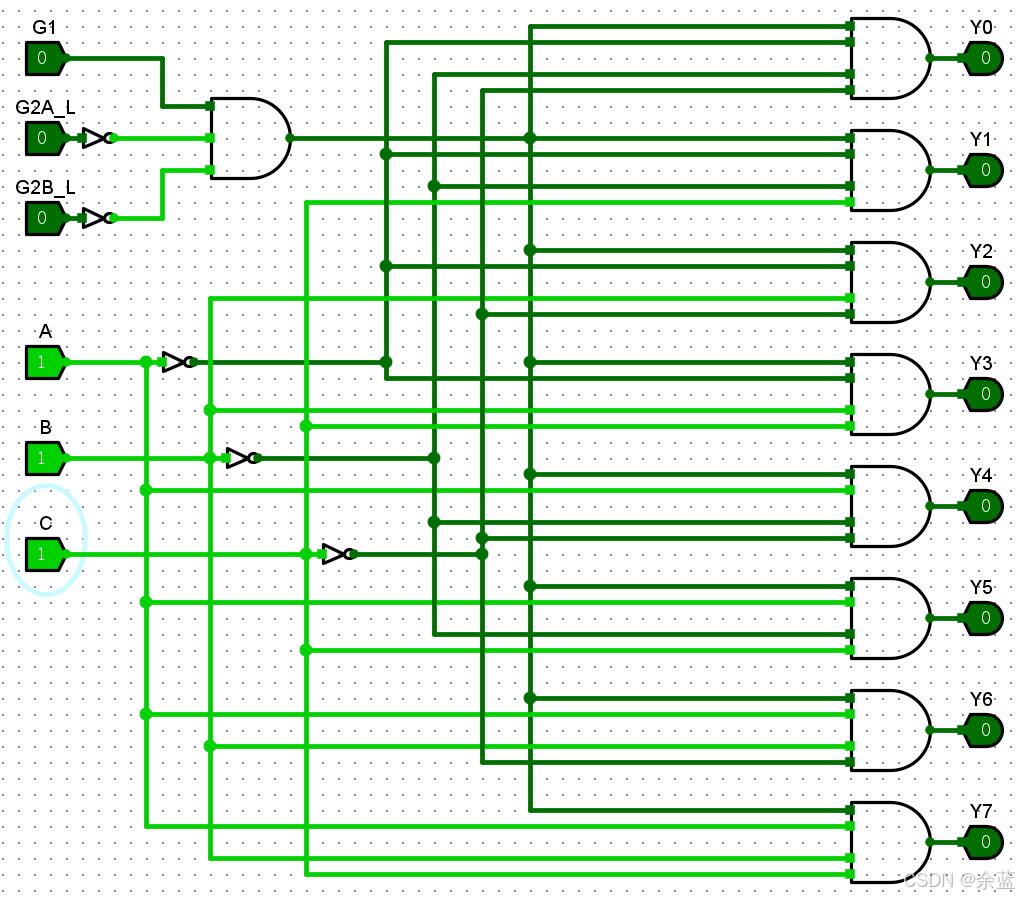

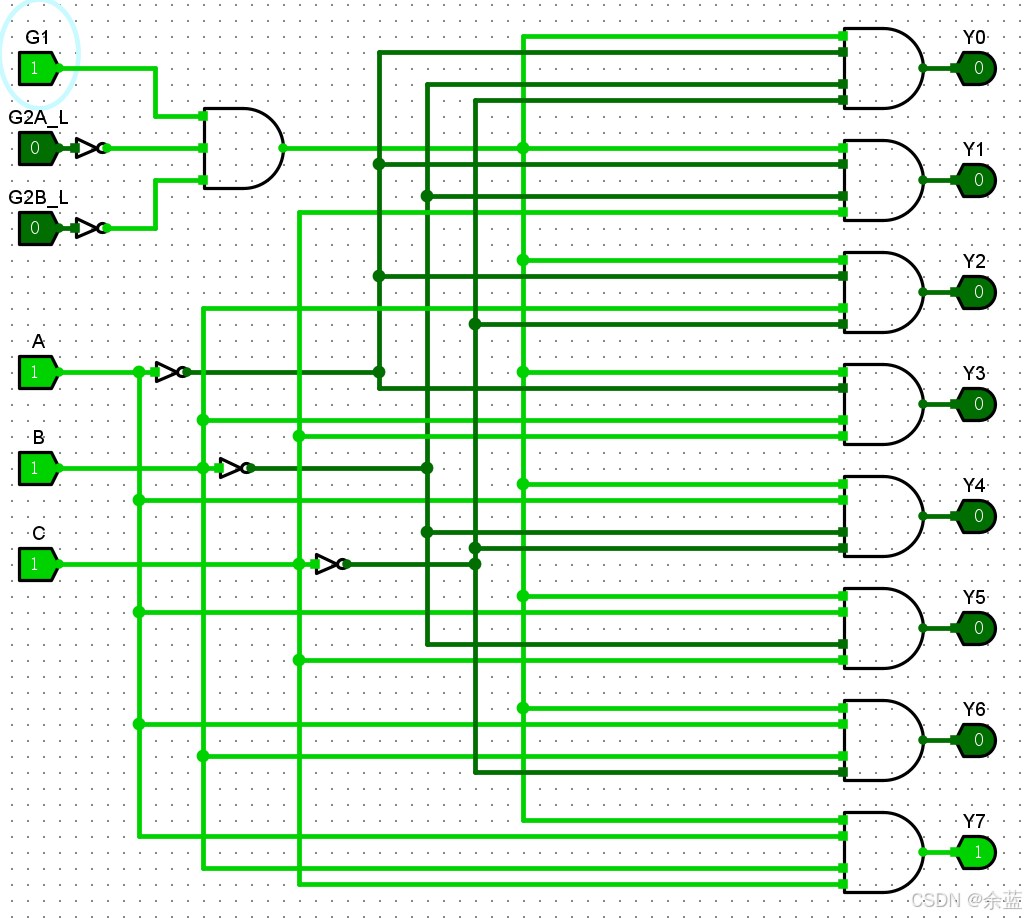

观察知,G1、G2A_L和G22B_L都是使能端,且每一个表达式都有G1~G2A_L~G2B_L,根据该表达式来连接三个使能端。当使能端无效,如下图所示的情况,则不管ABC的输入如何,每个输出均为0。

但当使能端有效,即满足G1~G2A_L~G2B_L这个关系式,则输出将会随输入端ABC的变化而变化,实现译码器的功能。

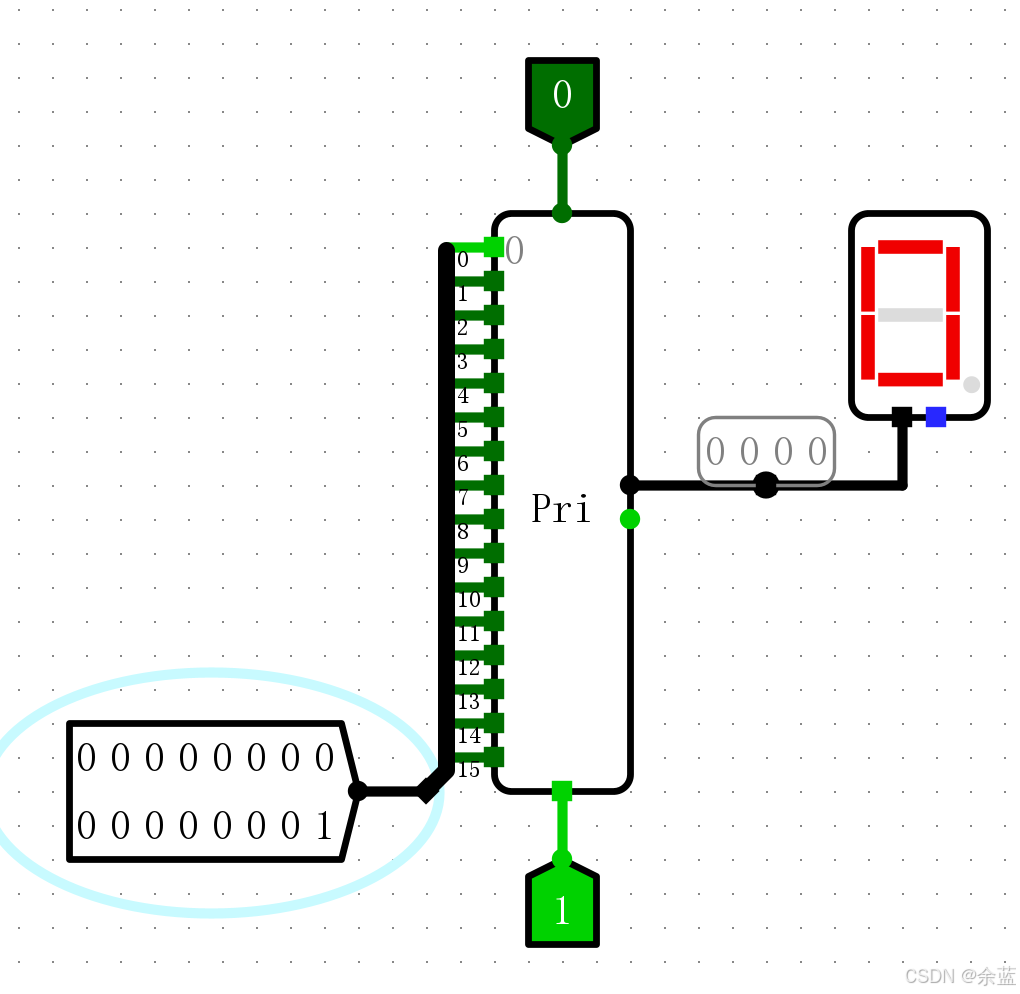

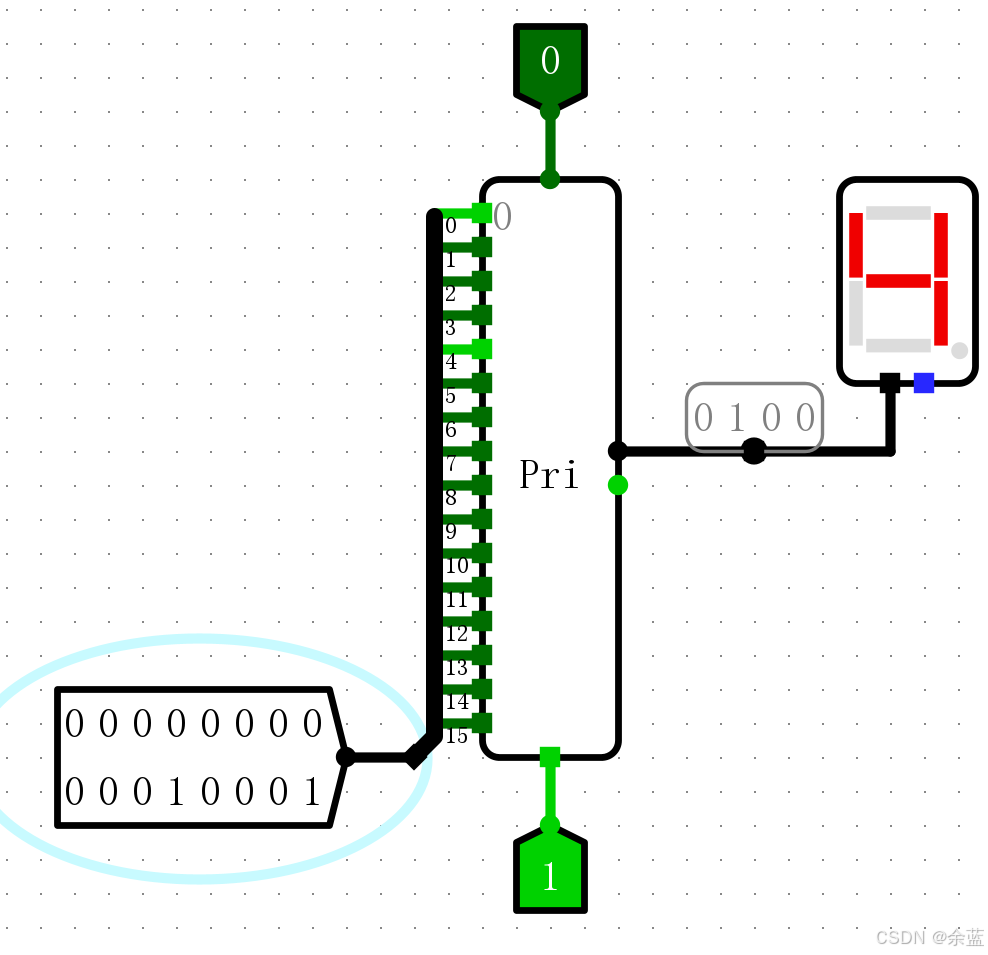

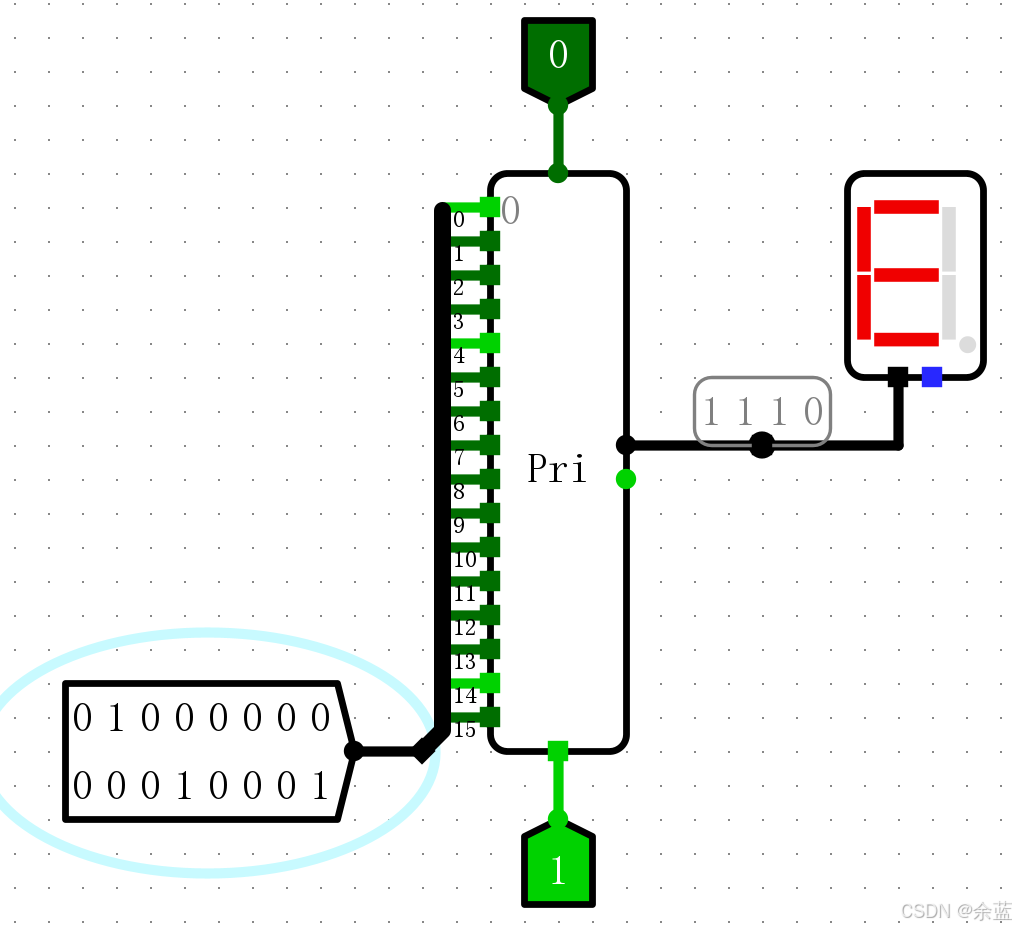

- 利用Logisim提供的优先级编码器,将编码器输出连接到一个十六进制数码管,通过数码管的输出显示来验证和测试电路。测试电路中可引入探针、分线器等,并增加电源和接地来连接数码管。

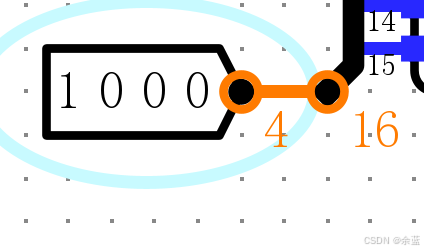

优先级编码器的特点是,最高位的“1”有效。如下图,最高位又1的即第0位,所以探针上显示0000且十六进制显示器显示0.

当有两个输入位为1且最高位为第三位,则如探针所示,值为0100,且十六进制计数器显示为4.

同理,不管为1的输入有几位,最高位是第14,则输出值为14.

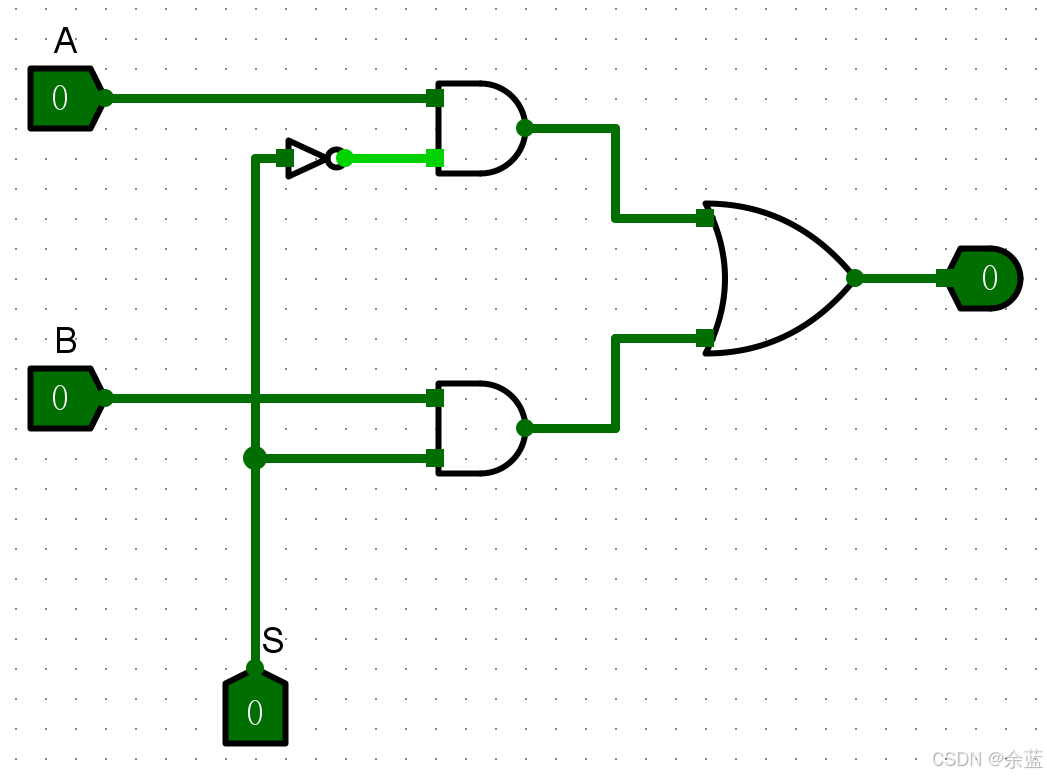

- 用基本门电路实现2选1多路选择器,并封装成子电路,用3个该子电路实现4选1多路选择器;

子电路为2选1多路选择器,具体结构如下图所示。

根据需求,当S为0时,输出A中的数据,所以将~S和A通过与门来连接;当S为1时,输出B中的数据,所以将S和B通过与门连接。最终用或门连二者的输出。

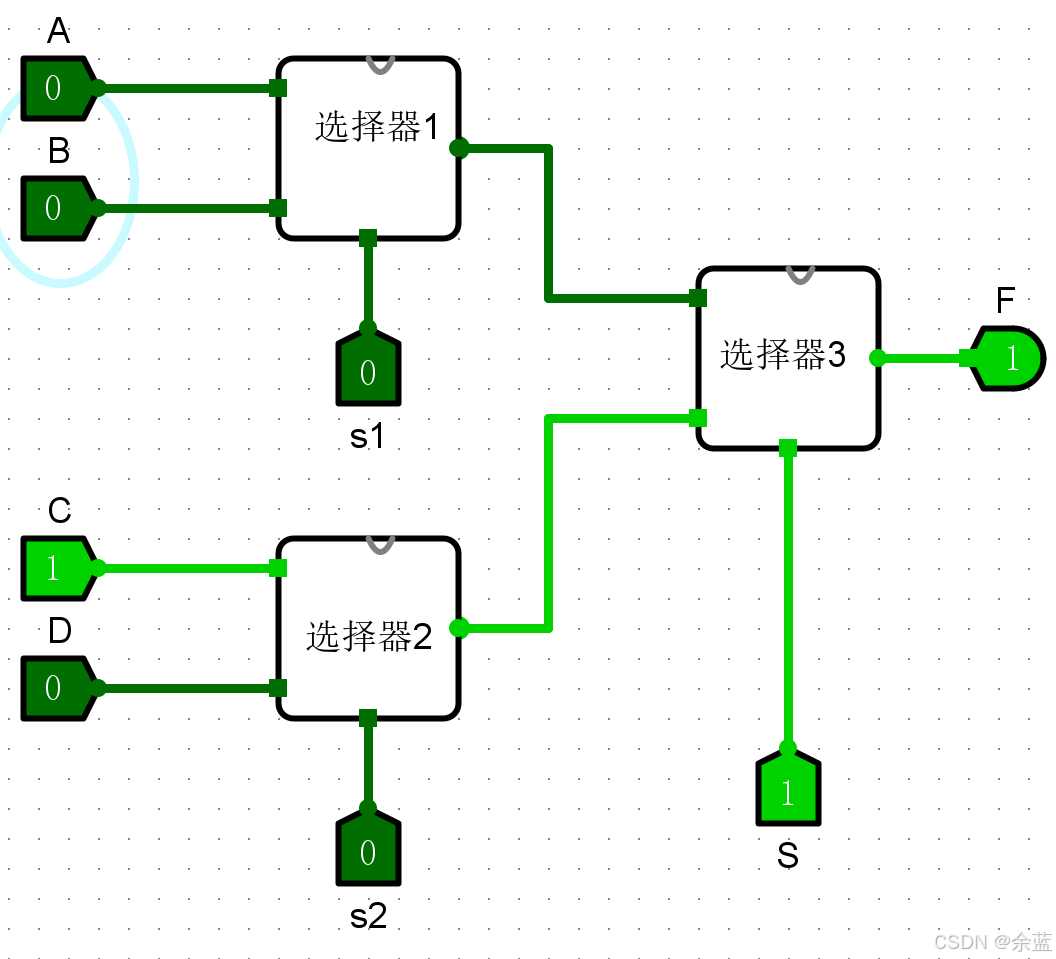

封装后s1控制左上的二路选择器,当s1值为0,控制输入A,此时A=0,所以将A输入到选择器3中;此时控制端S控制选择器3的输入,S=0,所以输入上端的数据,此时上端的数据为A,即0,所以输出F=0。

由于s1=s2=0,所以选择器1、2的有效输入端分别为A和C,所以进入选择器3的输入端的数据分别为A和C,即0和1。然而S=1,即选择器3的下端有效,所以输出F=C=1。

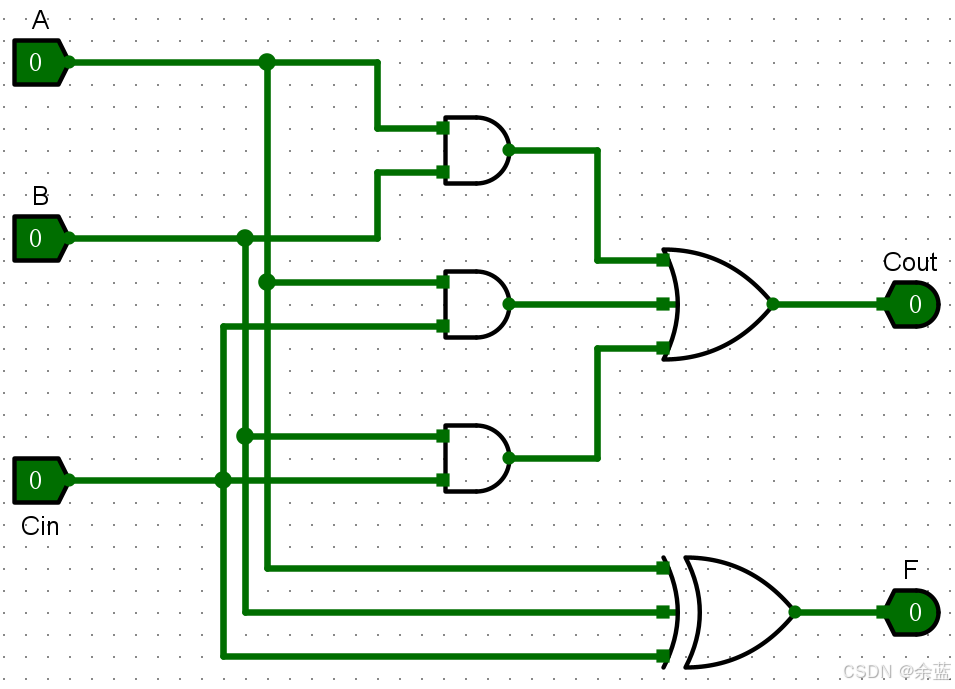

- 设计一个全加器(FA),并在此基础上将4个全加器串联成一个4位串行进位加法器。将输入、输出分别连接到16进制数码显示管(Hex Digital Display)进行验证。

本题的子电路,即全加器的电路,如下图所示。

本电路根据全加器的逻辑表达式设计。

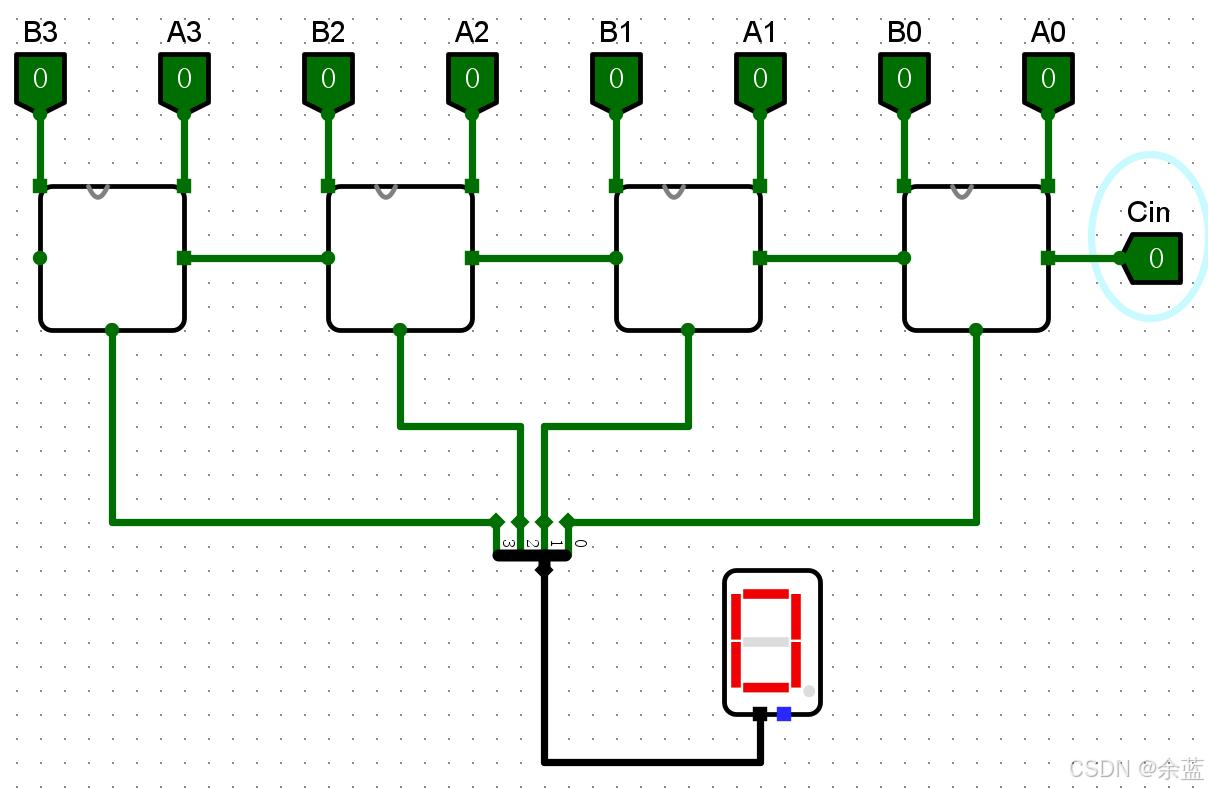

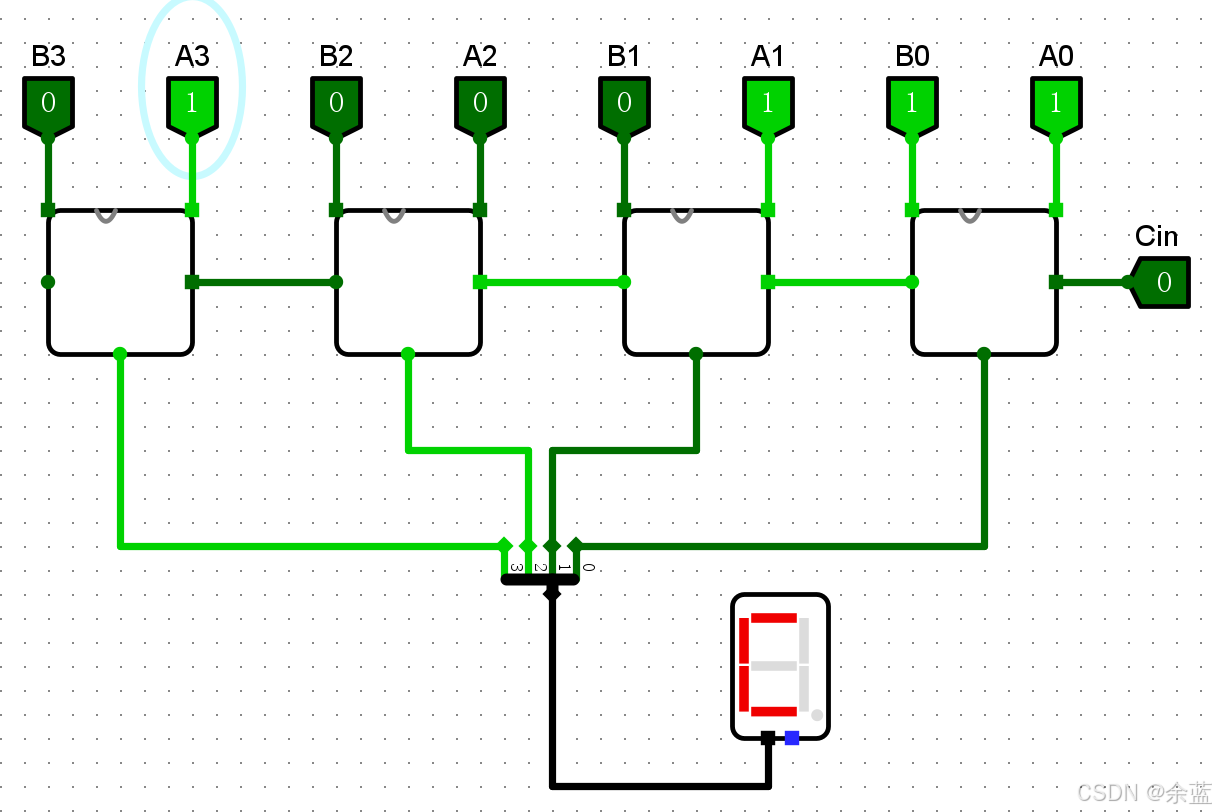

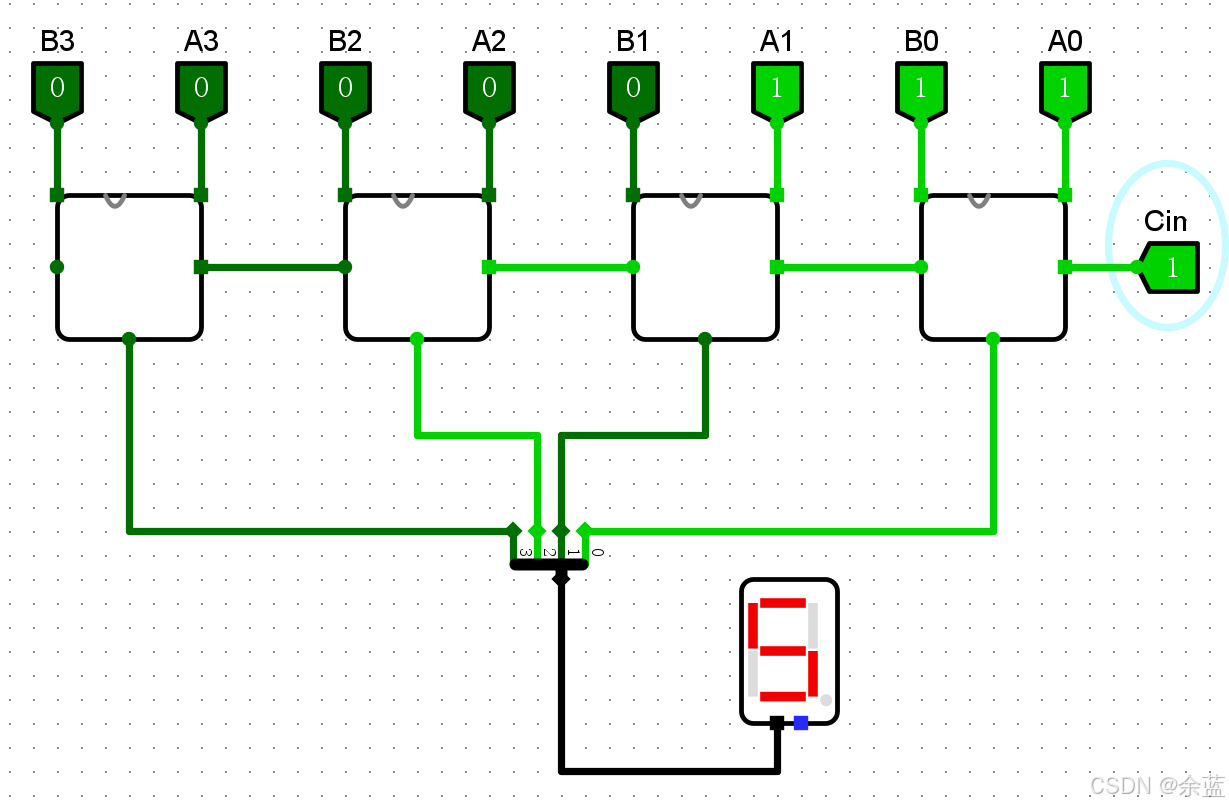

封装后串联成4位串行进位加法器,利用分线器,连接了十六进制数码显示管。

如图,最低位的加数为1、1,所以向高位进位1,并且最低位仍然为0。第二位加上来自低位的1后,向第三位进位,且第二位仍为0,此时第三位为1。由于第四位有加数A3,所以为1.综上,四个位的值为1100,即12(十进制),所以十六进制数码管显示C,符合要求。

如图,最低位有两个加数,且又有一个进位1,那么将会向第二位进位,且最低位还有一个1。由于第二位已有一个加数,所以又向第三位进位。最终该加法器的四位分别为0101,所以值为5。

(三)时序逻辑电路设计

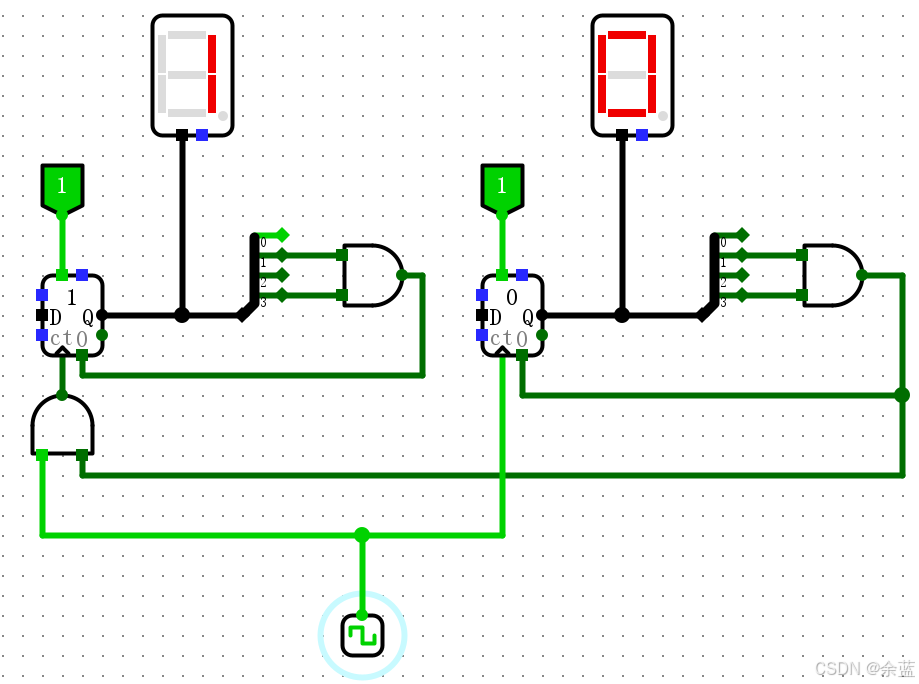

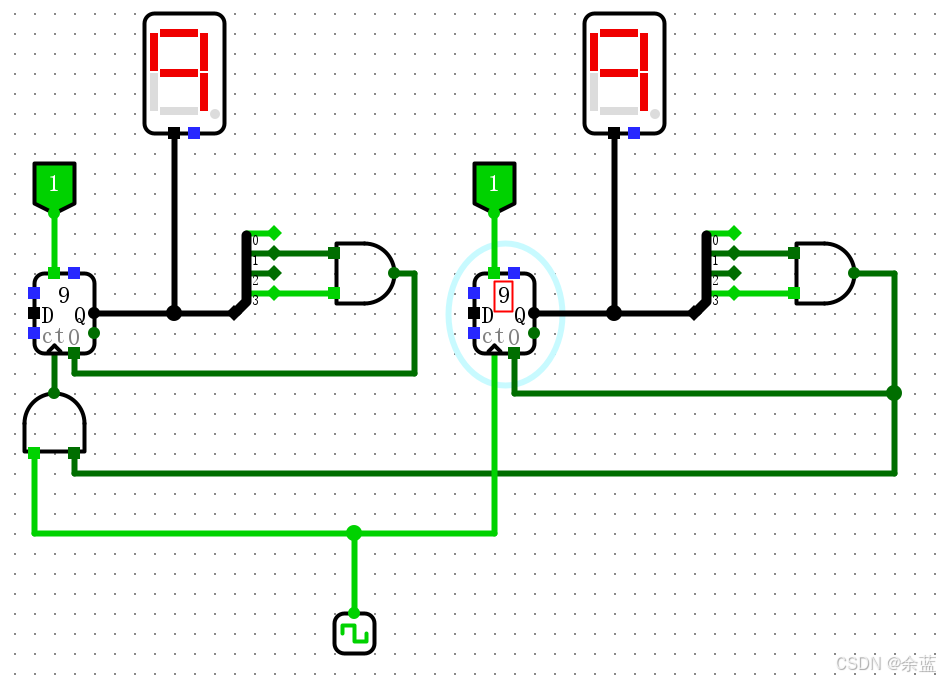

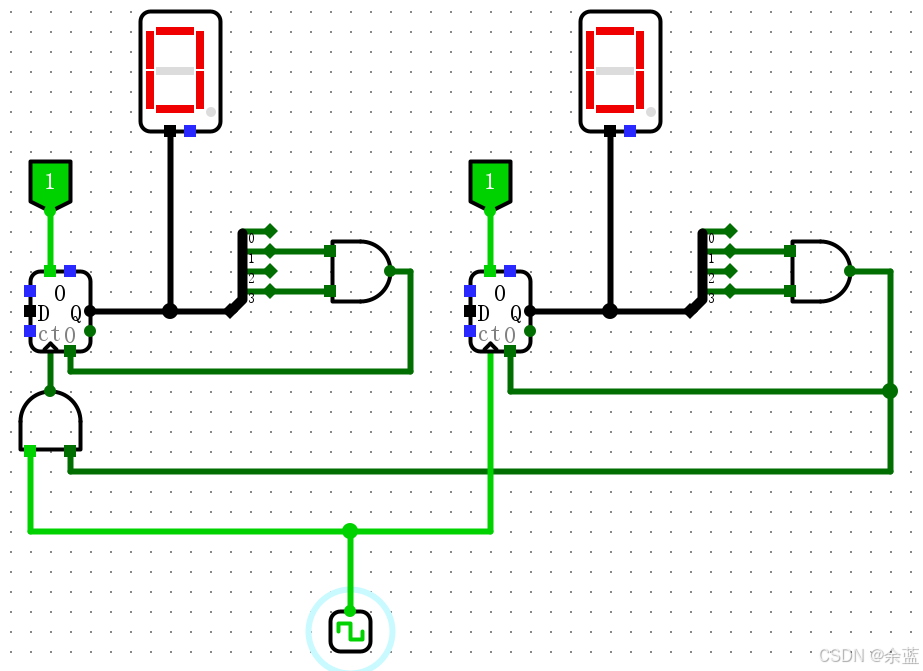

- 利用2个计数器,实现两位十进制计数(从0到99),两位连接到数码管输出显示。

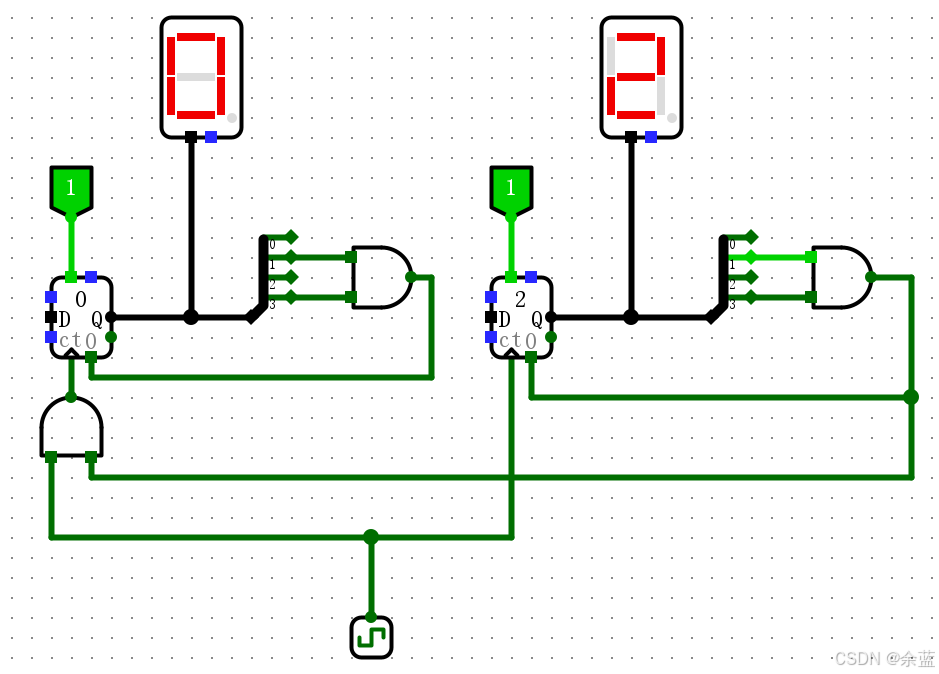

由于计数器是十六进制的,所以第一步是对计数器进行改装,以实现十进制计数功能,本处用到反馈回零法,当计数器的计数值达到10,那么将反馈到计数器的异步置零端(此处用分线器将计数器的四位计数值分位输出,记为A0A1A2A3,当值为10时,即A0A1A2A3=1010,应该要反馈回零,所以用与门将A0 A2连接到置零端,即可实现十进制计数功能。

然后,将两个十六进制显示器连接到计数器的输出端,显示计数器值。对于高位计数器,它的计数信号应该是时钟边沿到来且低位计数器的计数值已经溢出。所以将低位的反馈置零信号和时钟信号用与门连接到高位计数器的时钟信号端。

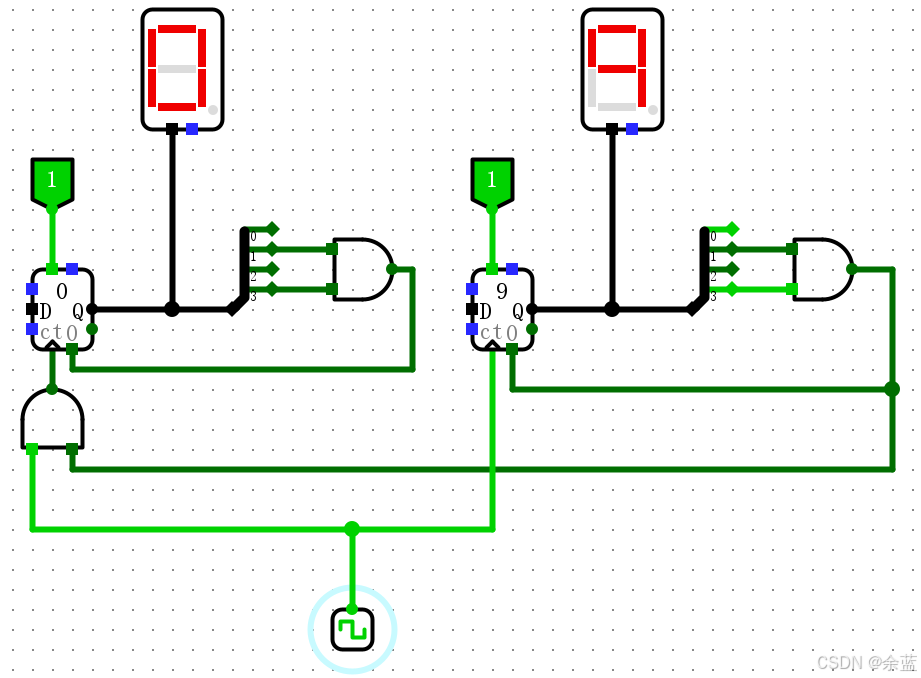

测试该电路,当时钟上升边沿到来,低位计数器便会计一次数。当它计到9时,反馈回零,所以将会输出零,并且在下一个时钟信号到来的时候,将高位计数器的计数值进一。如下图所示。

当计数器值为99,那么下一时刻将会置为00。如下图所示。

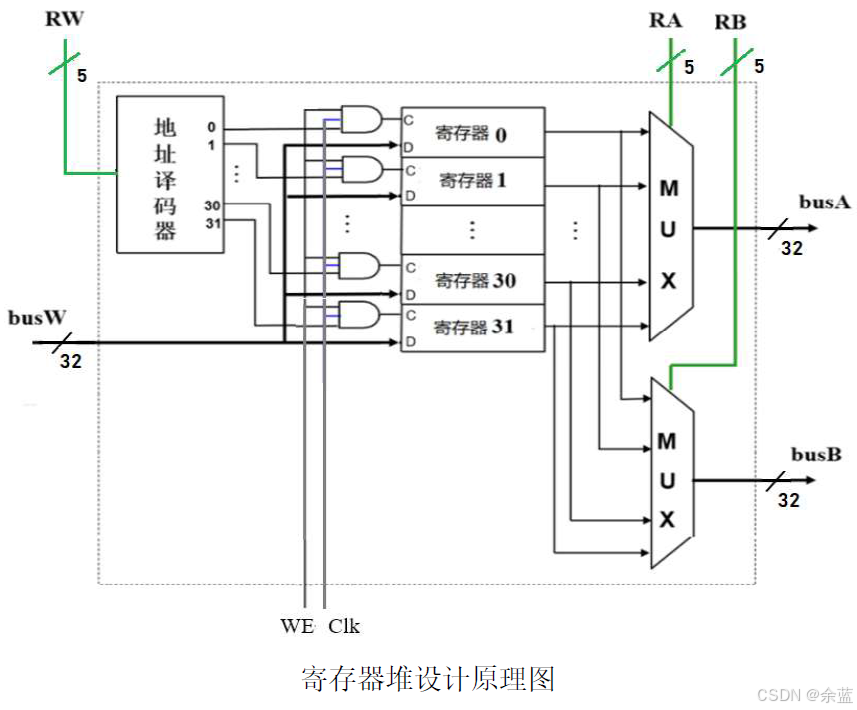

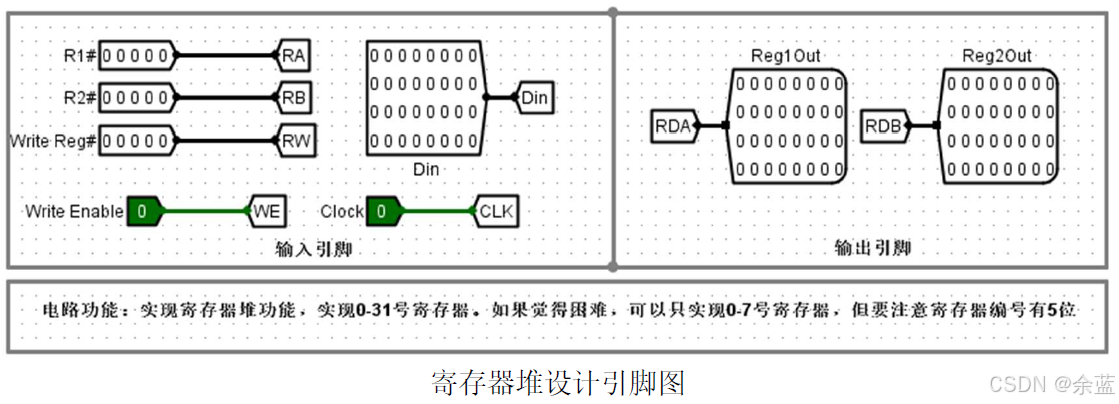

- 根据以下寄存器堆的原理图及给出的引脚图,构建实现至少含有 8 个 32 位寄存器堆Regfile的读写电路,写入操作需有时钟信号控制,读取操作是组合电路。要求:

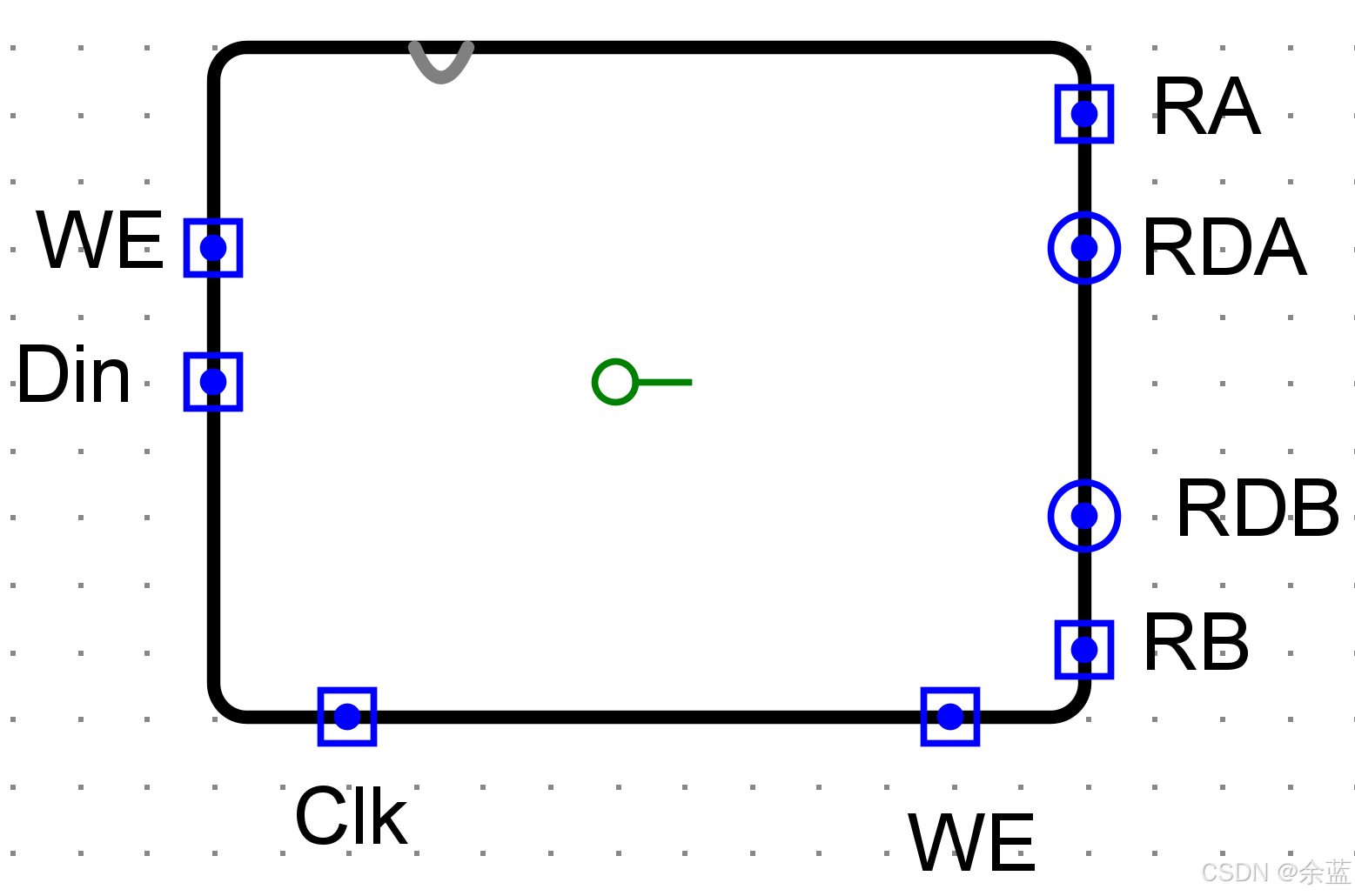

1) 有两个读口和一个写口,并封装成子电路。

2) 能在时钟信号有效时写入数据到指定寄存器,能够随时读取任意一个寄存器的数据。

本题要求实现32个寄存器,起初我使用5个选择端的译码器,但是电路非常不美观(线太多),于是我参考了课本教程的做法,使用4个3选择端的译码器,关键的思路是模运算思想。

模8运算,即第8个寄存器又可以视为寄存器0,第十六个也可以视为寄存器0。于是32个寄存器只需要3位编码,但是,模运算要求我们指定具体是哪一次循环中的,比如第十六个寄存器应该是第三次循环。所以增加两位编码来指定循环。

最终确定5位编码,低三位指定模内的寄存器编号,高二位指定第几次循环。

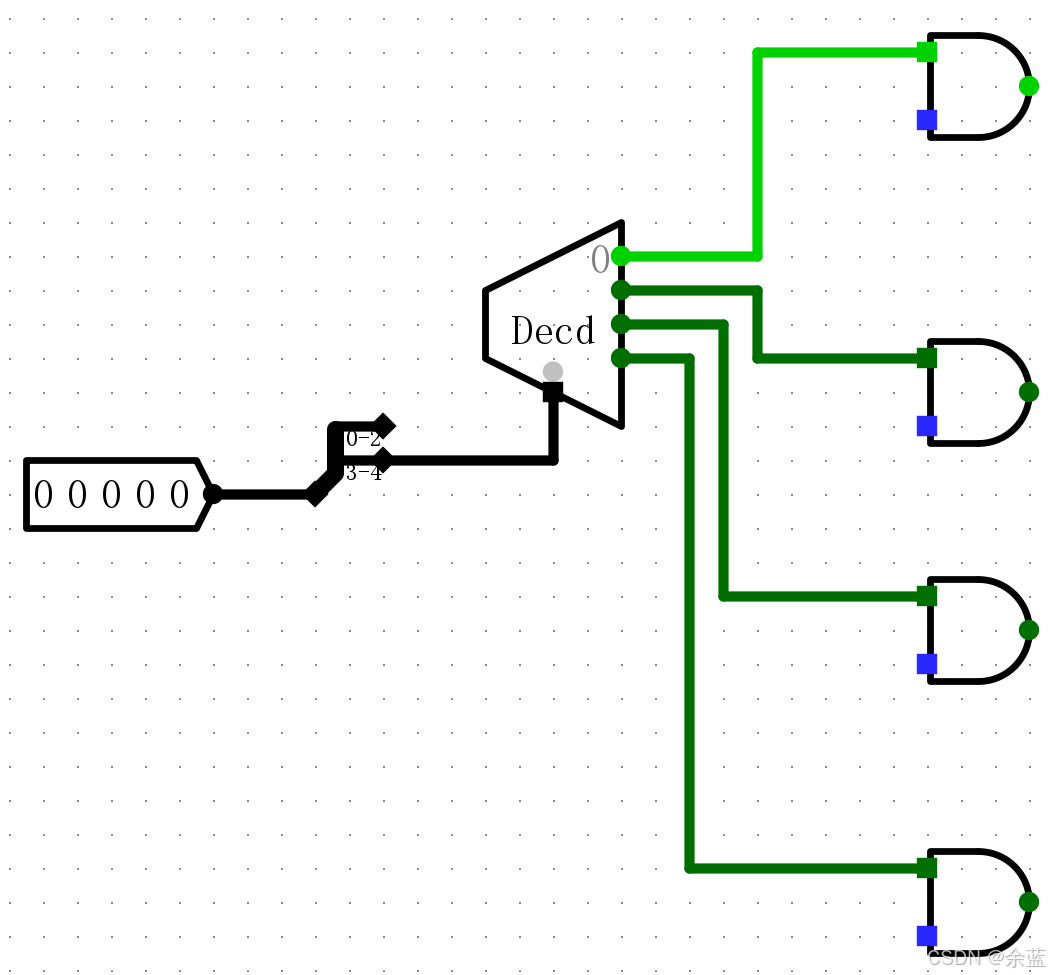

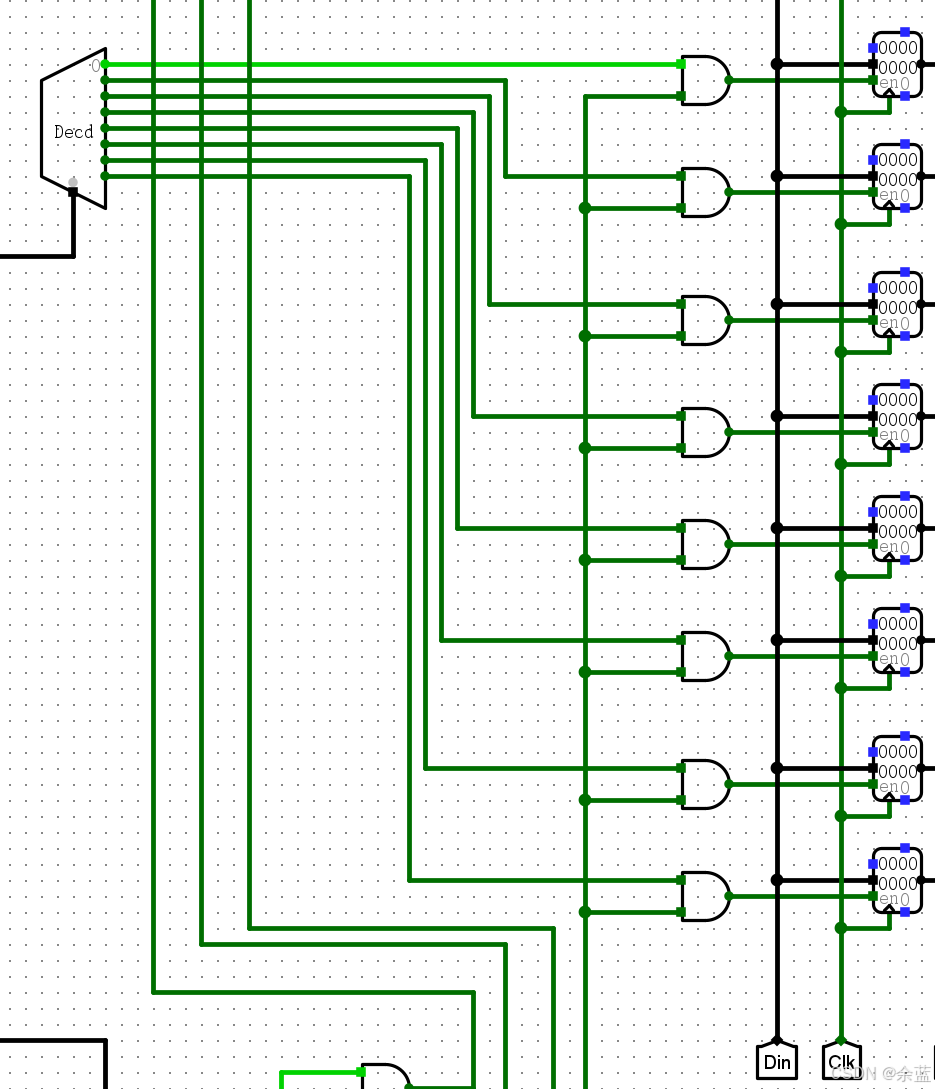

所以使用分线器,将五位编码分成低三位和高二位,如下图。

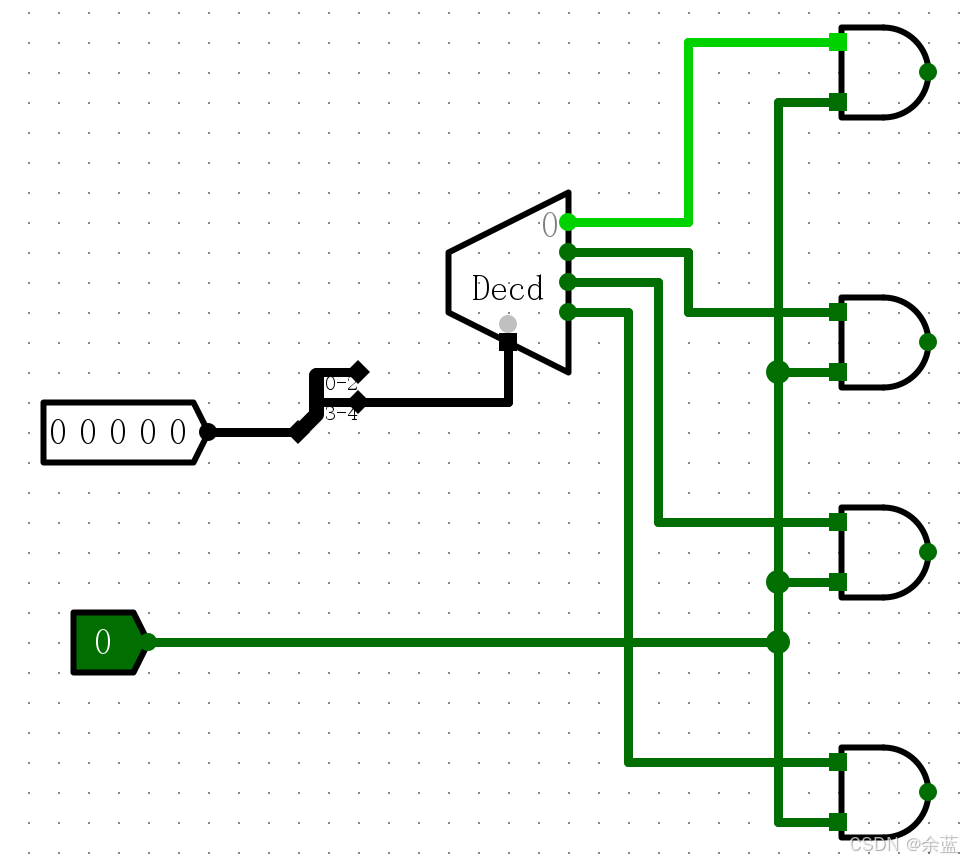

接着,为电路的美观(避免太多冗余线路),将使能端就在此连接。

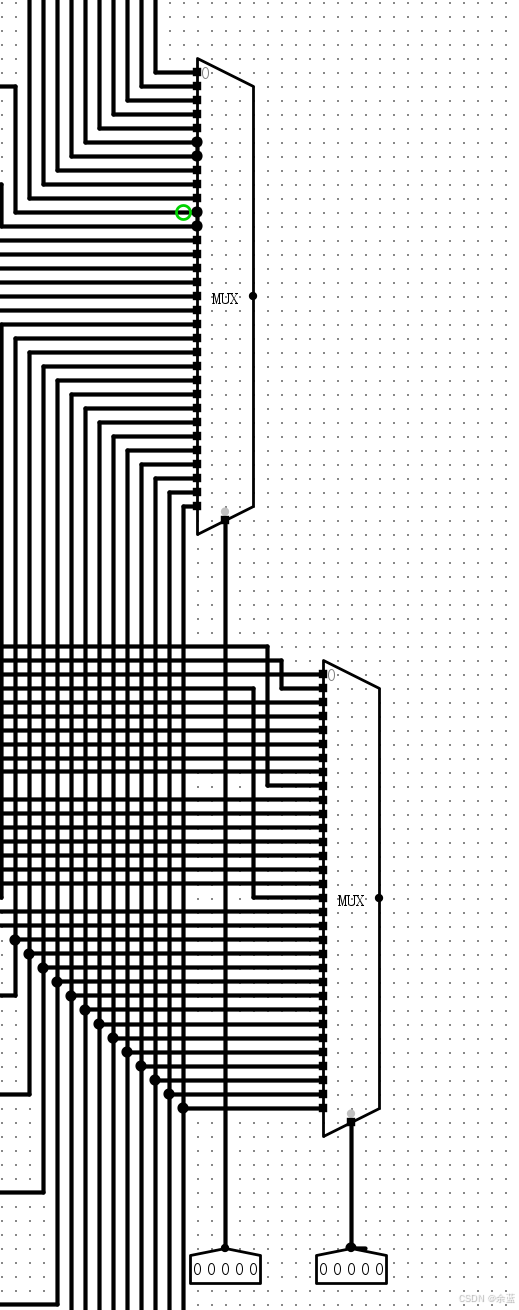

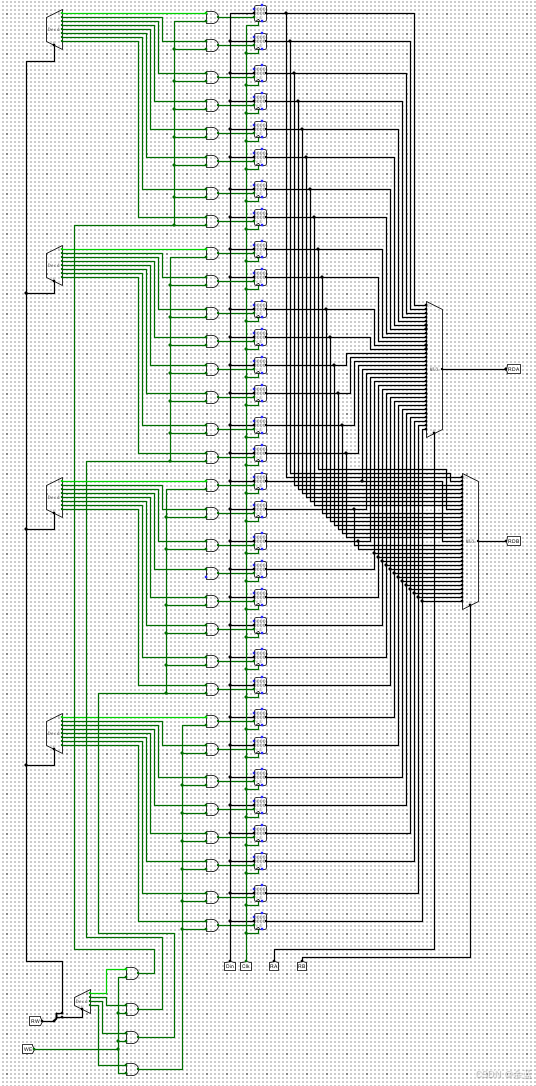

接着将32个寄存器的输出端连接到两个多路选择器,如图。

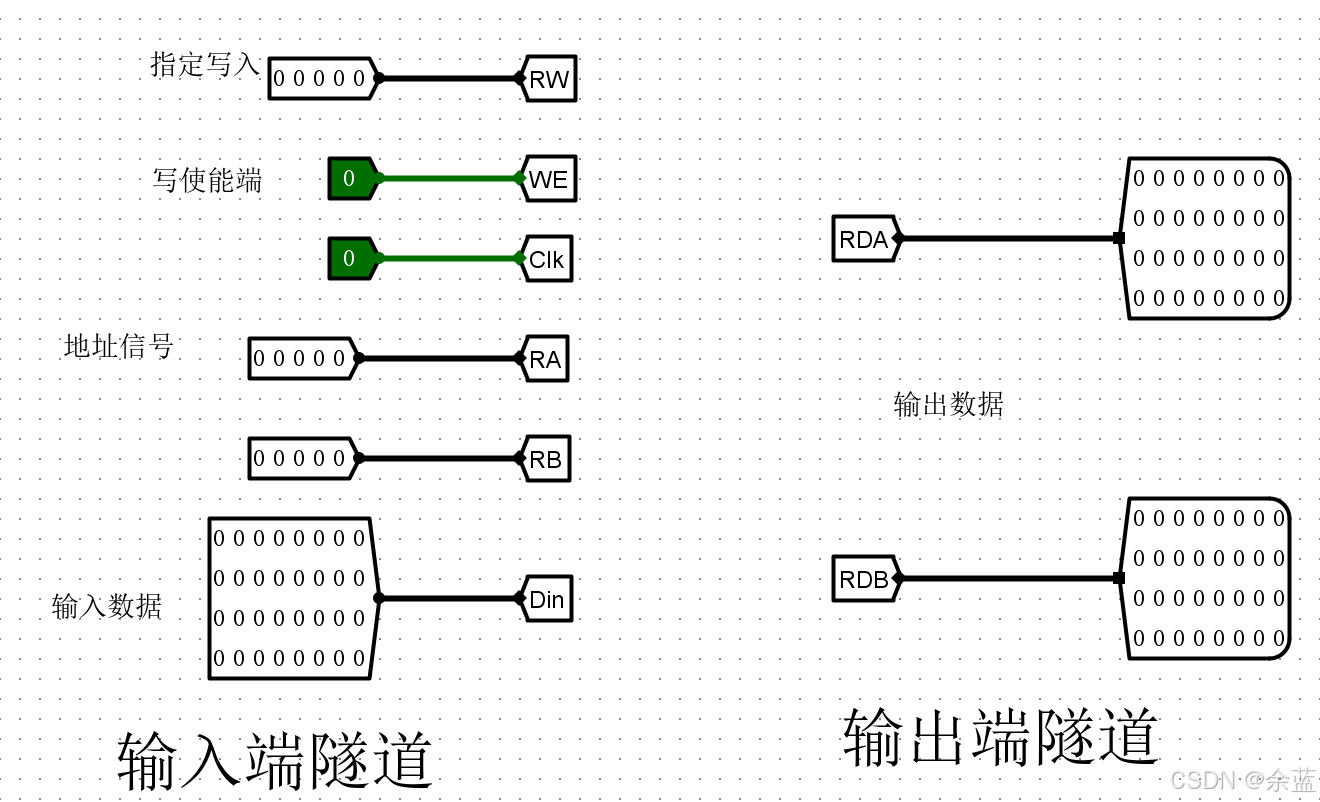

本题采用隧道的方式实现,各个隧道的说明如下

具体电路如下,其中RW是写口的寄存器编号,它通过连接一个译码器,指定将Din的数据写入哪个寄存器中。WE是写使能端。RA、RB是寄存器地址信号,指定将读出的数据输出到端口RDA还是RDB。

按照模运算思想,寄存器八个一组,其中一组如下图。

整体电路如下。

WE、时钟信号Clk、译码器 通过与门,连接各个寄存器,实现的功能是:在WE有效的情况下,下一个时钟有效信号到来时,将Din上的数据写入RW指定的寄存器中。当寄存器的地址编号(RA 或RB)到达后,通过多路选择器,读出的信息将会在RDA或 RDB上有效。

将电路封装,如下图所示。

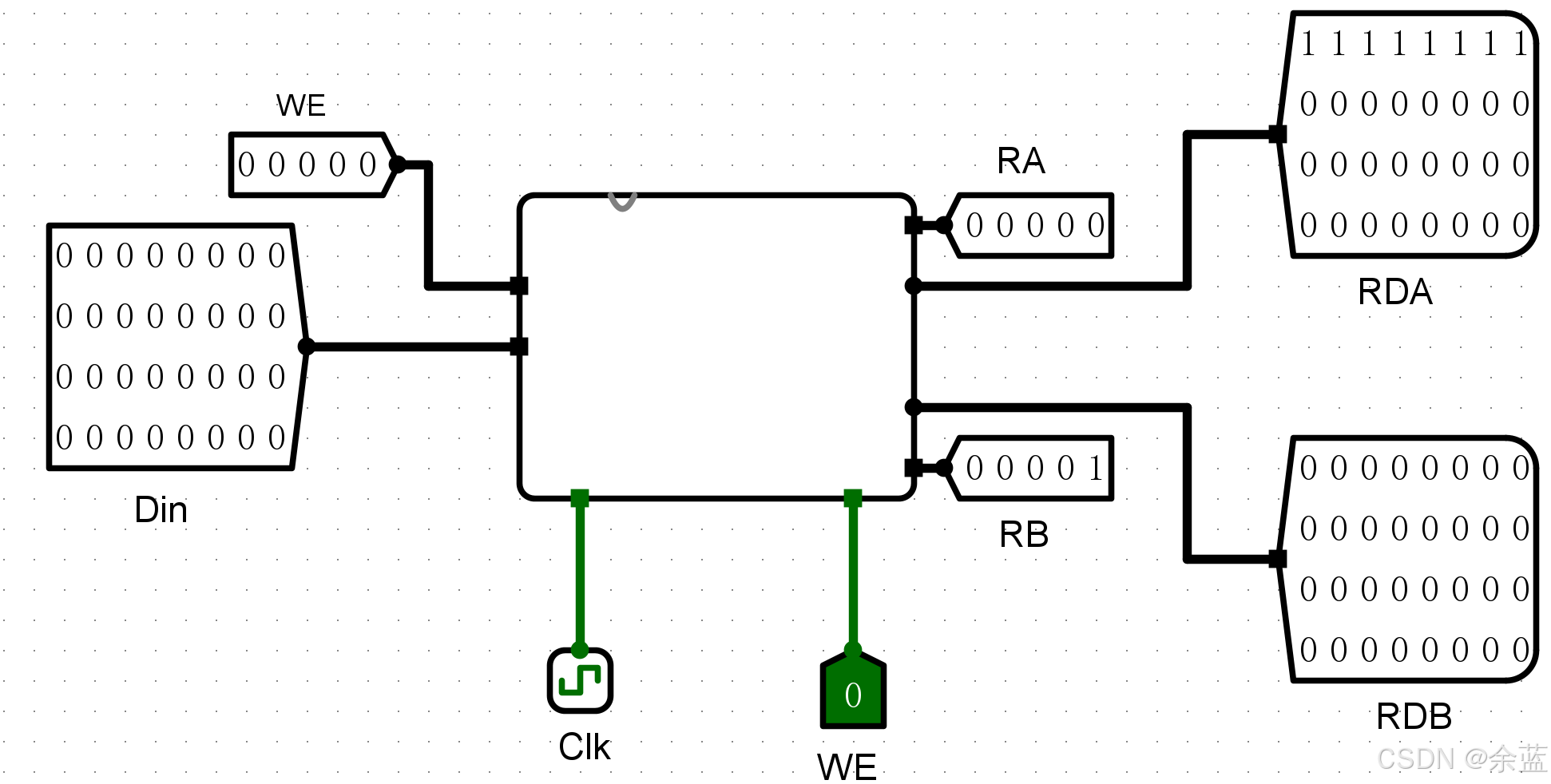

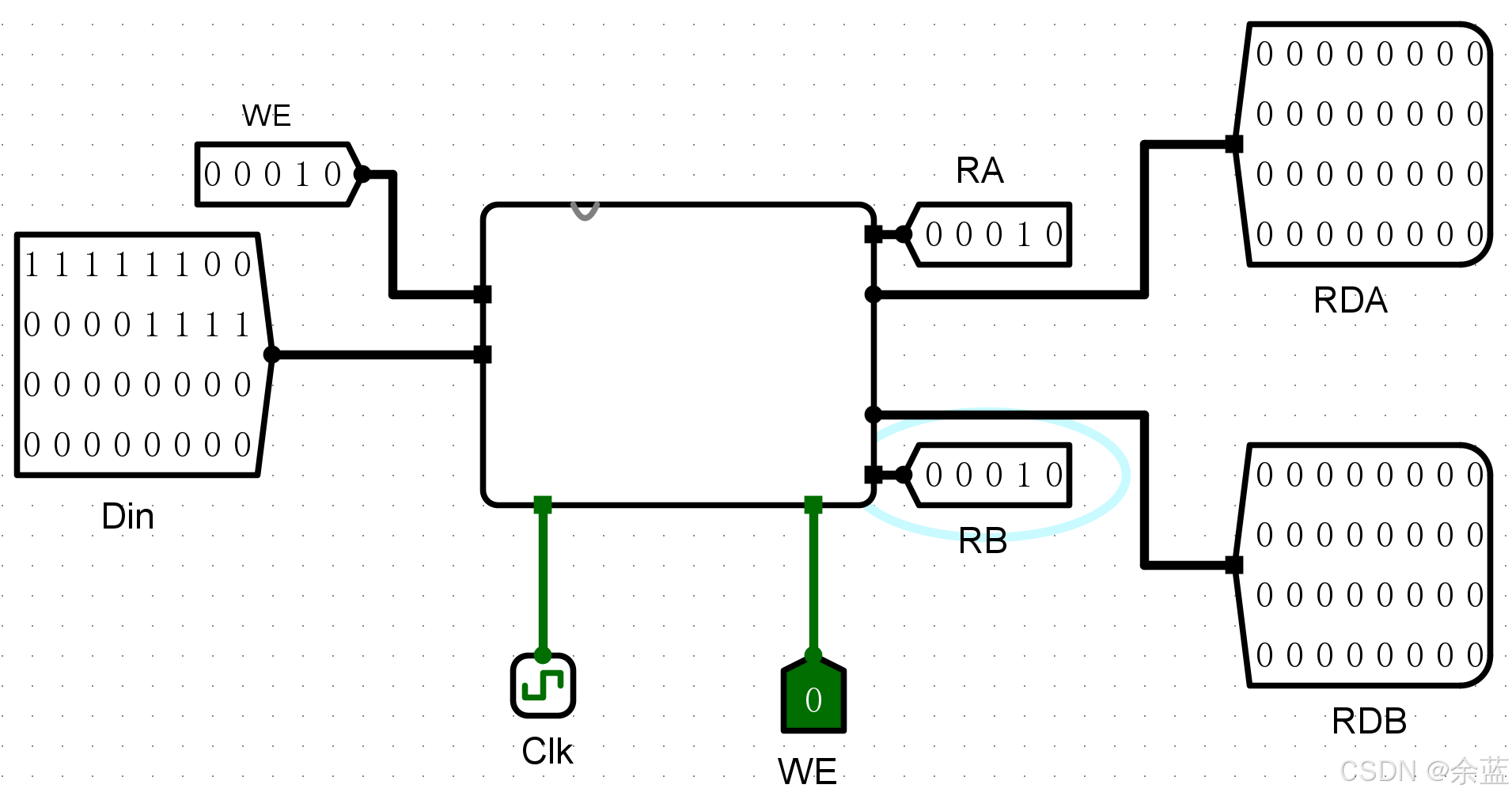

利用封装好的电路连接好第十题电路,作写、读操作。

测试电路:

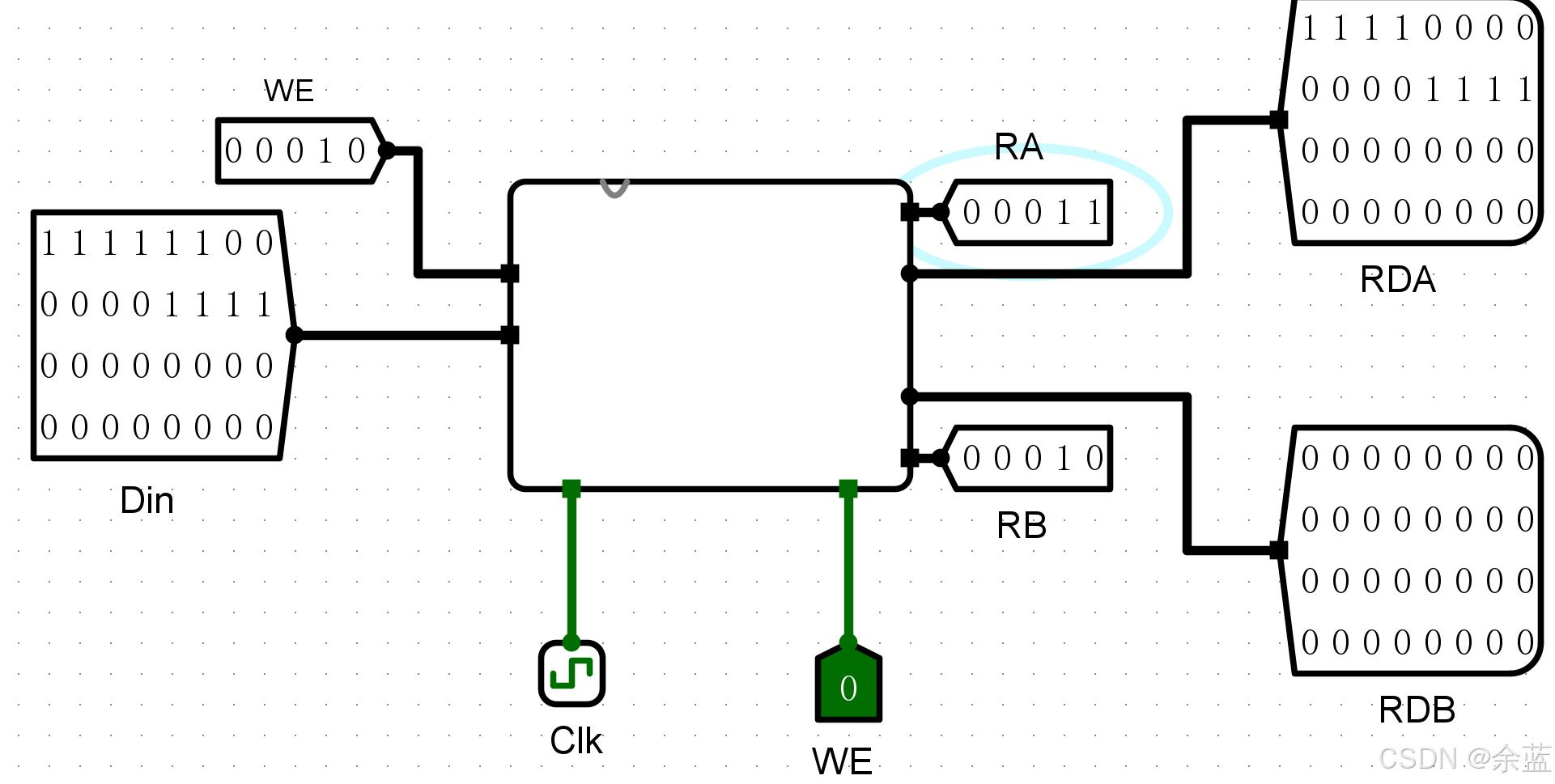

如下图,WE=00011,即指定将Din中的数据F00F0000写入3号寄存器中。且RA=00011,RB=00001,说明RDA输出端要接收来自3号寄存器的数据,而RDB输出端要接受来自1号寄存器的数据。因为3号寄存器已存入数据F00F0000,所以RDA输出该值。但是1号寄存器还是空白值,所以输出为0。

值得注意的是,写操作是时序逻辑电路,必须要在时钟信号有效的情况下,操作才会有效,而读操作是组合逻辑电路,就算没有有效的时钟信号,依然可以有输出。

当使能端无效或者时钟信号无效,那么上述功能读功能将失效,符合电路的基本要求。

但是读操作依然有效(前提是相应寄存器有存储着数据)。

如下图,就算时钟信号无效,但由于3号寄存器中还存储着数据,所以当RA指定将3号寄存器数据读取时,RDA可以输出有效的数据。

五、实验步骤及结果

实验步骤(包括逻辑表达式推导和电路设计等)及结果已经放到每道题目后面。

六、分析与思考

- 设计CMOS电路时,要注意CMOS晶体管中小箭头的朝向,具体朝上朝下应该有所讲究,否则电路将无法正常工作。

此外,由于或非门、与非门相对或门、与门的设计更为简单,所以先实现前者,再在上述基础上增加非门即可。

- 设计位数较多的复杂电路时,可以根据提示来改变端口位宽,当导线呈橙色时,是由于位宽不匹配导致,所以应该在这方面做出考虑。比如下图所示。

- 在设计带使能端的电路时,可以先设计使能端,完成后再将剩余电路看成无使能端的普通电路来设计,最后利用与门等逻辑门将两部分连接即可。比如第五题就是一个例子。

- 通过第八题的电路设计,我对加法器的理解更深刻了。第八题要求设计串行加法器,我的设计思路是,将封装好的加法器的Cout端连接到较高位的加法器的Cin端,以此激励模式实现串行进位。将各位的F端通过分线器汇集,并通过十六进制显示器来显示加法器各位的二进制数值。

- 第九题的最核心思想是反馈回零法。由于logism提供的计数器是十六进制的,所以需要将其改装为十进制。利用反馈回零法(具体做法已呈现在第九题下方),当计数器值为10时,反馈到异步置零端,以此实现十进制计数功能。对于高位计数器,它的计数信号应该是时钟边沿到来且低位计数器的计数值已经溢出。所以将低位的反馈置零信号和时钟信号用与门连接到高位计数器的时钟信号端。

- 第十题是综合性较强的题目,综合了多路选择器、译码器、寄存器等知识点。我采用模运算的思想,以减少电路的复杂性。具体思路已写在第十题后面。即模8运算,将32位寄存器按8个一组,这样写信号就可以作模运算,以指定不同循环内的寄存器编号。通过该电路的设计,我对寄存器堆有了更为深刻的理解。比如,因为写入操作是时序逻辑电路,所以需要时钟信号,还需要RW来选择写入哪个寄存器中。虽然32位寄存器数目比较大,连线比较多,但是逻辑清晰的时候,实现起来还是比较容易的。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?