计算机组成原理课程设计指导书

计算机组成原理课程设计是根据《计算机组成原理》及相关课程的基础知识和基本原理以及课内实验要求做的设计性课题,本次课程设计请同学们根据设计要求完成系统电路的仿真设计撰写报告,报告统一使用长春理工大学报告册(电子版)。

一、课程设计要求;

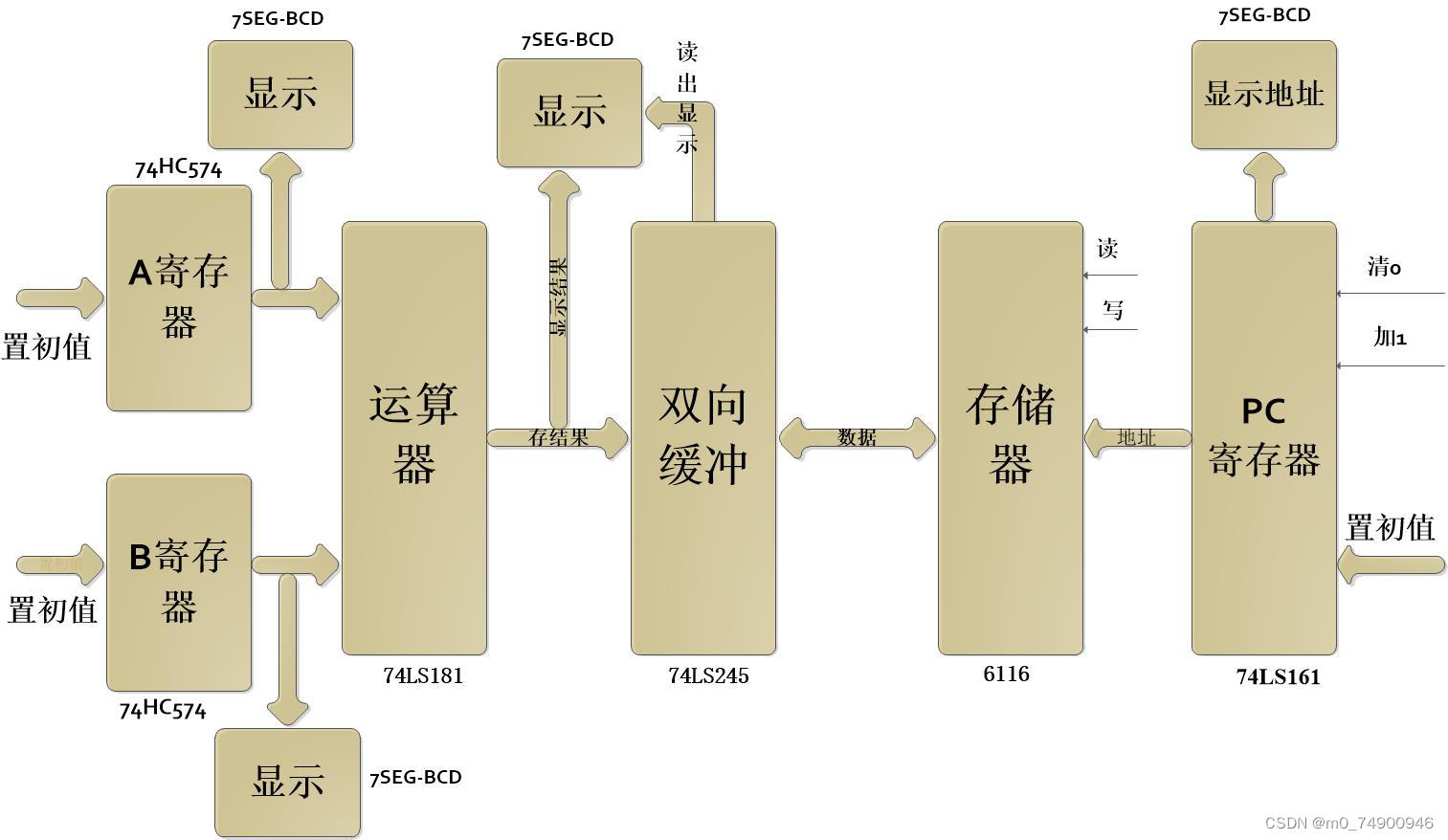

1.系统设计:根据任务要求,能设计出一个简单的计算机硬件系统,系统中包括寄存器,运算器,程序计数器,存储器。

2.系统仿真及电路测试:所设计的系统能在仿真环境下实现并运行,结果正确

3.报告内容要求:设计报告的内容包括系统分析、设计和实现以及实验结果等各个部分;字数2000字~3000字,内容充实、逻辑严谨、叙述清晰、格式规范。雷同报告或抄袭他人设计电路的做不及格处理!

二、设计任务与要求

任务:设计一个简单的计算机硬件系统并在Proteus环境下仿真运行。

要求:能够完成对寄存器内容进行多种运算并按地址寄存器中地址的指示写入到存储单元中,另外可以对存储器单元内容进行读出并显示。要求电路尽量简化,在Proteus上进行系统电路的设计和并能仿真运行。

三、方案设计思路

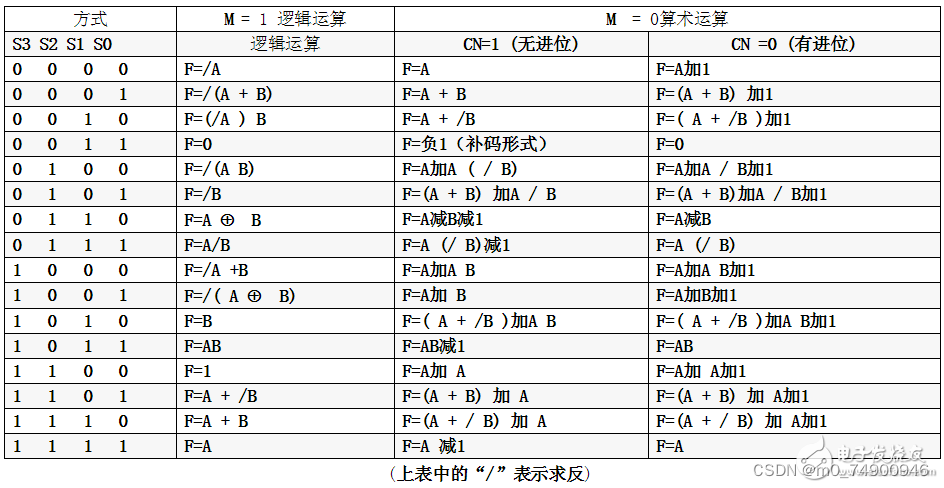

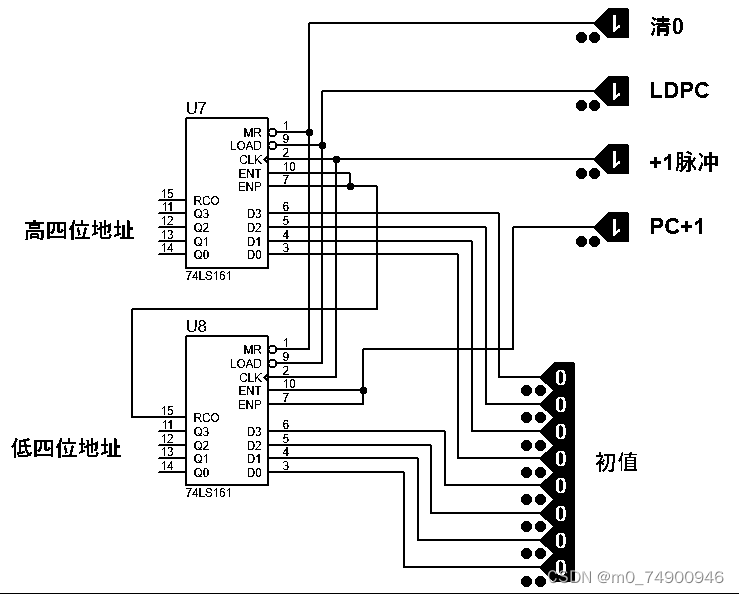

A和B寄存器都是八位寄存器,可以用8位三态D触发器74HC574,运算器用两片4位先行进位ALU74LS181构成八位运算器,存储器用SRAM intel 6116,可以进行写入和读出,PC寄存器用两片同步四位二进制计数器的74LS161构成八位计数器,内容做为地址使用,显示部分用BCD七段数据码显示。

四、主要元器件和功能介绍

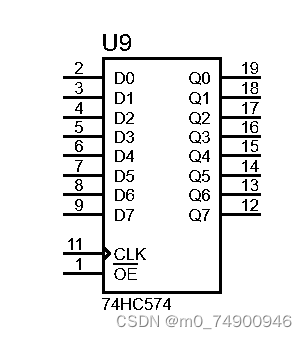

1、用74HC574(八D边沿触发触发器(三态))来构成A和W寄存器。

(1)引脚图及引脚功能:

在CLK的上升沿将输入端的数据打入到8个触发器中

当OE = 1 时触发器的输出被关闭,当OE=0 时触发器的输出数据

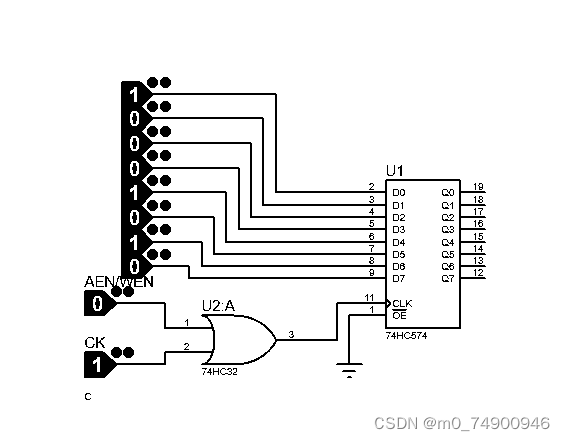

(2)仿真电路

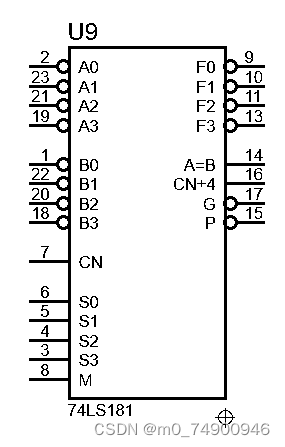

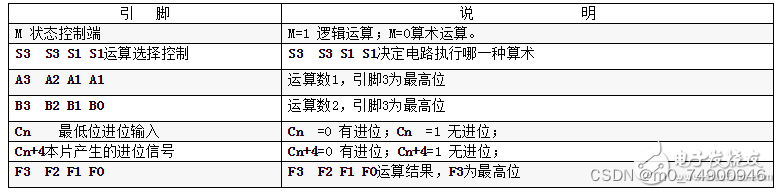

2、74LS181是能完成4位二进制代码的算逻运算部件

(1)引脚图及引脚功能:

(2)仿真电路

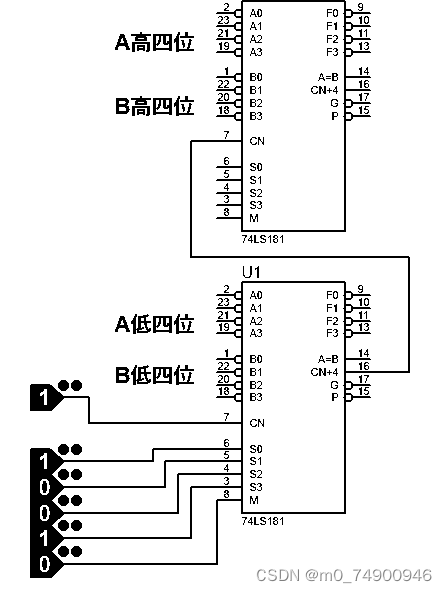

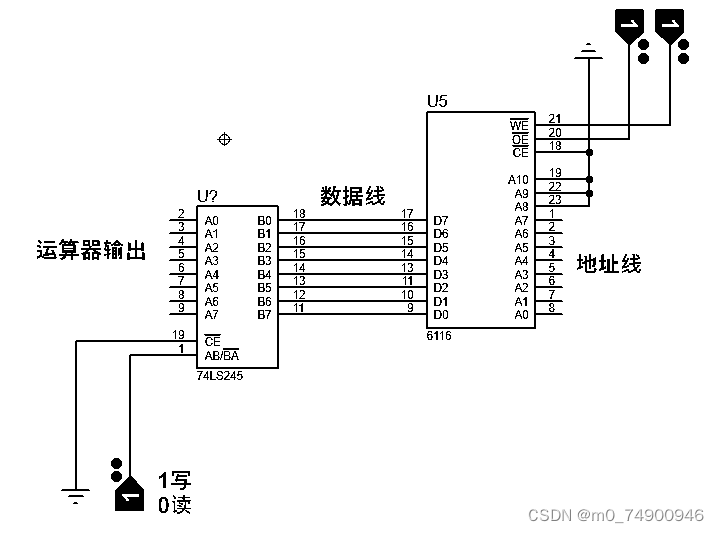

3、74LS245还具有双向三态功能,既可以输出,也可以输入数据。

引脚图及引脚功能:

DIR:方向控制

A0~A7:输入/输出

B0~B7:输出/输入

OE:输出使能

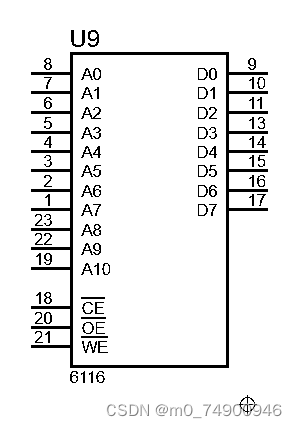

4、静态存储器芯片 6116

6116是一种数据宽度为8位(8个二进制位),容量为2048字节的静态存储器芯片,有8根双向三态数据线D7-D0,11根地址线A10-A0,3根控制线CS片选控制信号,低电平时,芯片可进行读写操作,高电平时,芯片保存信息不能进行读写:WE为写入控制信号,低电平时,把数据线上的信息存入地址线 A10-A0指示的存储单元中;OE为输出使能控制信号,低电平时,把地址线 A10-A0指示的存储单元中的数据读出送到数据线上。

(1)引脚图及引脚功能

A0~A10:地址线,用于选择存储单元。

D0~D7:数据线,用于数据的读写。

CE(片选信号):低电平有效,用于选择芯片进行读写操作。

OE(输出允许信号):低电平有效,用于允许数据输出。

WE(写允许信号):低电平有效,用于允许数据写入。

当CE为低电平,OE为低电平时,进行读操作,数据从D0~D7输出。

当CE为低电平,WE为低电平时,进行写操作,数据从D0~D7写入。

(2)仿真电路

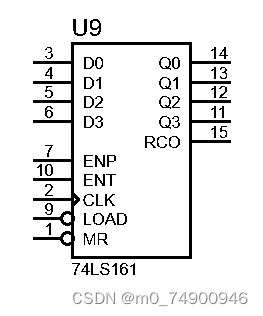

5、74LS161记数器

74ls161是一个常用的四位二进制可预置的同步加法计数器,

如果清零端CR=“0”时,计数器输出Q3、Q2、Q1、Q0都会马上为全“0”,这个时候是异步复位功能。当CR=“1”并且LD=“0”时,CP信号上升沿作用之后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,这个时候是同步置数功能。而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

D0-D3:数据输入端

ENP、ENT:使能输入端

CLK:时钟输入信号

LOAD:置数端(低电平有效)

MR:清零端(低电平有效)

Q0-Q3:数据输出端

RC0:进位输出端

(2)仿真电路

完整电路图和实验报告在百度网盘内

链接: https://pan.baidu.com/s/1ChEfm0iB5glc34Tsxni2aQ?pwd=iixy 提取码: iixy

仅供参考!!!

2336

2336

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?