首先说明一点:只要是基于ARM7内核的处理器,其中断都是从0x00-0x1c(8个中断向量)处开始执行。

处理器的存储器映射可以归结为三种情况:

1 没有存储器的映射

这样的处理器有:三星的S3C44BX处理器。没有存储器映射的处理器,其BANK地址是固定的,而且第一级中断向量的都是放到规定好的BANK0处(即地址0x00处)。可以归纳为:BANK地址固定且第一级中断向量位置固定(0x00)。

2 有存储器的映射

地址空间的重新分配,与处理器的硬件结构紧密相关。总体来说,32位系统中的地址重映射机制可以分为两种情况:一类是处理器内部专门的寄存器可以完成Remap,这样只需将Remap寄存器的相应位置1,由硬件逻辑来完成地址的重新映射,如Atmel AT91xx系列;另一类没有专门的Remap控制寄存器,需要重新改写处理器内部用于控制Memory起止地址的Bank寄存器,来实现Remap过程。如S3C4510B。

2.1 BANK地址固定,但是第一级中断向量位置不固定(即复位后不一定从0x00执行)

这样的处理器有:LPC2200系列(以LPC2214为例)。

LPC2214中有存储器映射控制,用于改变从地址0x00000000开始的中断向量的映射,这就允许了在不同存储器空间的代码对中断进行控制。

要重新映射的部分包括:中断向量区(32个字节)和额外的32个字节。具体代码如下所示。

;中断向量表

Reset

LDR PC, ResetAddr

LDR PC, UndefinedAddr

LDR PC, SWI_Addr

LDR PC, PrefetchAddr

LDR PC, DataAbortAddr

DCD 0xb9205f80

LDR PC, [PC, #-0xff0]

LDR PC, FIQ_Addr

ResetAddr DCD ResetInit

UndefinedAddr DCD Undefined

SWI_Addr DCD SoftwareInterrupt

PrefetchAddr DCD PrefetchAbort

DataAbortAddr DCD DataAbort

Nouse DCD 0

IRQ_Addr DCD 0

FIQ_Addr DCD FIQ_Handler

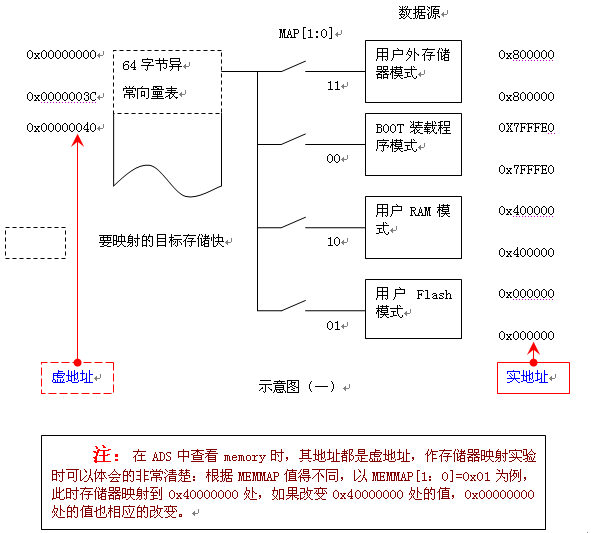

下面是存储器映射控制的示意图(一)(参考文献[1])。

|

示意图(一) |

|

数据源 |

|

11 |

|

00 |

|

10 |

|

01 |

|

0x00000000 |

|

0x0000003C |

|

0x40000000 |

|

0x4000003C |

|

0x7FFFE000 |

|

0X7FFFE03C |

|

0x80000000 |

|

0x8000003C |

|

0x00000000 |

|

0x0000003C |

|

0x00000040 |

|

要映射的目标存储快 |

|

BOOT装载程序模式 |

|

用户Flash模式 |

|

用户RAM模式 |

|

用户外存储器模式 |

|

MAP[1:0] |

|

11 |

|

00 |

|

10 |

|

01 |

|

虚地址 |

|

实地址 |

|

64字节异 常向量表 |

|

注:在ADS中查看memory时,其地址都是虚地址,作存储器映射实验时可以体会的非常清楚:根据MEMMAP值得不同,以MEMMAP[1:0]=0x01为例,此时存储器映射到0x40000000处,如果改变0x40000000处的值,0x00000000处的值也相应的改变。 |

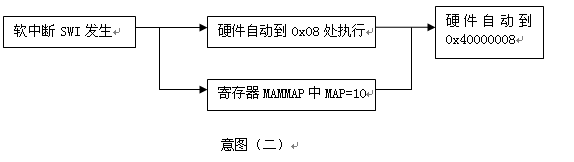

下面以一个具体的中断例子来说明存储器的映射问题。假设现在发生了软中断SWI,此时程序运行在用户的RAM模式(通过设置MEMMAP[1:2])。中断响应流程见示意图(二):

|

软中断SWI发生 |

|

硬件自动到0x08处执行 |

|

寄存器MAMMAP中MAP=10 |

|

硬件自动到0x40000008 |

|

意图(二) |

文字描述为:当发生软件中断时,ARM7内核硬件本来自动到0x08处执行,但此时的寄存器MEMMAP[1:2]为10,将控制硬件到0x40000008去执行代码。

2.2 BANK地址不固定,但是第一级中断向量位置固定(即复位后始终从0x00执行)

这样的处理器有:三星的S3C4510B。

S3C4510B的每一个BANK的地址都是可以通过重映射改变的,因此,系统的存储器无论是Flash还是SDRAM,其起始地址都不是固定的。

S3C4510B内部有几个特殊寄存器,用于实现地址空间和芯片内外存储介质的映射。这几个寄存器的简介如下:

l SYSCFG:设置特殊寄存器的起始地址和片内SRAM的起始地址。

l EXTDBWTH:设置各Bank寄存器所映射芯片的数据线宽度。

l ROMCON0~ROMCON5:设置系统内片扩展ROM和Flash的起始和终止地址。

l DRAMCON0~DRAMCON3:设置系统内片外扩展RAM的起始和终止地址。

S3C4510B芯片内特殊寄存器段的物理地址为0x3ff0000。各特殊寄存器的偏移地址详见S3C4510B的技术手册。

图1为系统的硬件结构。此系统是以Samsung公司给出的测试板为参考建立的,其中ROM的容量为512KB,8位数据总线,Remap前的地址范围为0x0000000~0x0100000,Remap后的地址范围为0x1000000~0x1100000;RAM的容量为16MB,32位数据总线,Remap前的地址范围为0x0100000~0x100000,Remap后的地址范围为0x0000000~0x1000000;Flash的容量为2MB,16位数据总线,Remap前后地址不变,均为0x1100000~0x1300000。Remap前后的地址映射关系如图2所示。

参考文献

[1] 周立功等编著.ARM嵌入式系统基础教程.北京:北京航空航天大学出版社,2005.1

635

635

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?