答案解析:

存储周期是指( )。

- A、

- B、

- C、

- D、

答案解析:

答案解析:

答案解析:

高的是( )。

答案解析:

Ⅰ. 64K×8 位 Ⅱ. 32K×4 位 Ⅲ. 32K×16 位 Ⅳ. 16K×32 位

答案解析:

答案解析:

答案解析:

答案解析:

答案解析:

答案解析:

I RAM是易失性存储器,ROM是非易失性存储器

II RAM和ROM都是采用随机存取方式进行信息访问

III RAM和ROM都可用做Cache IV RAM和ROM都需要进行刷新

答案解析:

答案解析:

若存储器容量为32K×16,则( )。

- A、

- B、

- C、

- D、

二.填空题(共8题)

计算机系统中的存储器分为____ 和____。在CPU执行程序时,必须将指令存放在____中。

内存;内存储器

外存;外存储器

内存;内存储器

我的答案:

答案解析:

我的答案:

答案解析:

DRAM存储器的刷新一般有____、____和____三种方式,之所以刷新是因为有电荷泄漏,需定期补充。

集中式

分散式

异步式

我的答案:

我的答案:

答案解析:

三.判断题(共10题)

答案解析:

答案解析:

答案解析:

答案解析:

答案解析:

答案解析:

答案解析:

答案解析:

答案解析:

答案解析:

1.用512K×8 位的Flash 存储芯片组成一个4M×32 位的半导体只读存储器,存储器按字节编址,试回答以下问题:

(1)该存储器的数据线数和地址线数分别为多少?

(2)共需要几片这样的存储芯片?

(3)说明每根地址线的作用。

解:

(1)由于所需组成存储器的最终容量为4M×32 位,所以需要32 根数据线。而存储器又是以字节编址,所以我们需要将存储器的容量先转换成16M×8 位,所以需要地址线24 根(224=16M)。

(2)采用512K×8 位的Flash 存储芯片组成4M×32 位的存储器时,需要进行位扩展和字扩展:

位扩展:4 片512K×8 位的Flash 存储芯片位扩展可以组成512K×32 位的Flash 存储芯片。

字扩展:8 组512K×32 位的Flash 存储芯片字扩展可以组成4M×32 位的存储器。

综上,一共需要4×8=32 片512K×8 位的存储芯片。

(3)在CPU 的24 根地址线中(A0~A23),地址线的作用分配如下:

A0、A1、: 由于在进行位扩展中,使用了4 片512K×8 位的Flash 存储芯片,而存储器是按字节编址的,所以必须在某个时候都可以取到其中的任何一片,使用00、01、10、11 分别来标记这4 片。

A2~A20 :每一片都是512K,所以需要19 位(219=512K)来表示。

A21、A22、、A23:因为在扩展中4 片一组,一共有8 组,所以需要用3 位地址线来决定取哪一组(通过3-8 译码器形成片选信号)

2.

设有一个具有20位地址和64位字长的存储器,问:

(1)该存储器能存储多少个字节的信息?

(2)如果存储器由256K x 8位SRAM芯片组成,需要多少片?

(3)需要多少位地址作芯片选择?为什么?

【解】

(1)220 * 64 / 8 B = 1M * 8 B = 8 MB

(2)8MB / (256K * 8 / 8 B) = 8MB / 256KB = 32片

(3)∵每8片芯片组成一组256K * 64位的存储器,每片芯片有18位地址(对应于256K个存储单元)

∴低18位地址直接接芯片的18位地址端,高2位地址通过2:4译码器作芯片选择。

3.

什么是存储器的带宽?若存储器的数据总线宽度为32位,存取周期为200ns,则存储器的带宽是多少?

解:存储器的带宽指单位时间内从存储器进出信息的最大数量。

存储器带宽 = 1/200ns ×32位 = 160M位/秒 = 20MB/秒(注:1ns=10-9s)

4.

一个容量为16K×32位的存储器,其地址线和数据线的总和是多少?当选用下列不同规格的存储芯片时,各需要多少片?

1K×4位,2K×8位,4K×4位,16K×1位,4K×8位,8K×8位

5.

设有一个具有24位地址和8位字长的存储器,求:

(1)该存储器能存储多少字节的信息?

(2)若存储器由4M×4位的RAM芯片组成,需要多少片?

(3)需要哪种译码器实现芯片选择?说明地址线分配情况

解:

⑴ 存储单元数为224=16MB,故能存储16M字节的信息。

⑵ 由于存储容量为16MB(8位字长),每4M字节需要2片(位并联方式),故需芯片数为16/4×2=8片。

⑶ 若用8片组成一个16M(8位字长),地址总线的低22位可直接连到芯片的A0-A21管脚,而地址总线的高2位(A22,A23)需要通过2:4线译码器进行芯片选择。存储器组成方案为位并联和地址串联相结合的方式。

6.

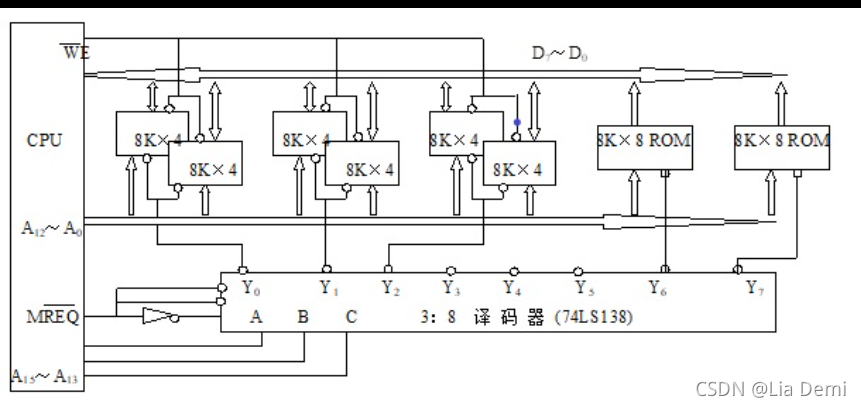

用8K×8位的ROM芯片和8K×4位的RAM芯片组成存储器,按字节编址,其中RAM的地址为0000H~5FFFH,ROM地址的地址为C000H~FFFFH,设计出此存储器组成结构图及与CPU的连接图。

解:RAM的容量为:8K×3=24K,RAM用8K×4的芯片组成,需8K×4的芯片6片;

7.

设某主存储器访问一次存储器的时间如下:传送地址1个时钟周期,读写4个时钟周期,数据传送1个时钟周期,采用下述3种主存结构读写16个字的数据块,各需要多少时钟周期?

(1)单字宽主存,一次只能读写一个字;

(2)4字宽主存,一次可读写4个字,但CPU与主存的数据传送宽度为1个字;

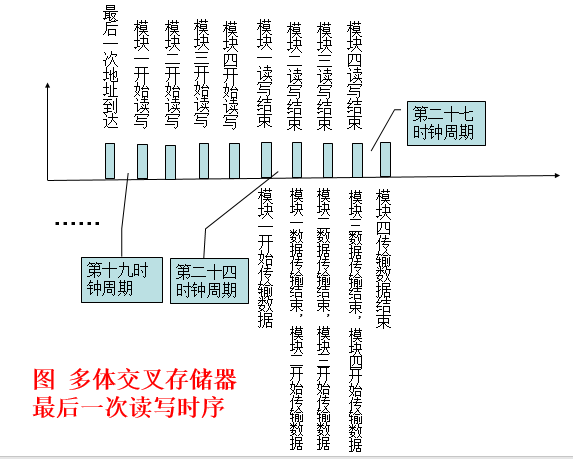

(3)4体交叉存储器,每个存储体为单字宽。

解:

(1)顺序方式:单字宽主存,一次读/写1个字,只能采用串行方式进行读写,16个字所需时间为:(1+4+1)×16=96;

(2)单体多字:4字宽主存,一次可读写4字,16个字需读写4次,但最后一次读出还需要增加3个时钟周期才能将数据送到CPU(前三次CPU收到四个返回数据中第一个就开始发下一次的地址。因此,对于前三次,收到的后三个数据传送时间与后面传送地址时钟周期、读写时钟周期重叠,不计算在总时间内):所需时间=4*6+3=27;

(3) 多体交叉:4体交叉存储器,每个存储体为单字宽:每个体访问4次,最后再加上3个时钟传送数据。总共需要 6*4+3=27 个时钟周期。(详见下图)

468

468

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?